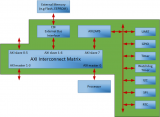

Virtex®-7 2000T拥有 68 亿个晶体管, 200 万个逻辑单元,相当于 2,000 万个 ASIC 门。这也是首款采用赛灵思独特的堆叠硅片互联(SSI)技术的FPGA。Virtex-7 2000T将使其无需借助并行或者串行I/O, 或者通过片外的 PCB连线与相邻的 FPGA 互联, 即可充分享受到FPGA芯片内高带宽、低时延、低功耗互联机制的优势。

了解如何将复杂的SoC平台映射到单个Virtex®-7 2000T FPGA

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1630文章

21796浏览量

605848 -

赛灵思

+关注

关注

32文章

1794浏览量

131483 -

soc

+关注

关注

38文章

4199浏览量

219036

发布评论请先 登录

相关推荐

如何设置内网IP的端口映射到公网

在现代网络环境中,端口映射(Port Mapping)是一项非常实用的技术,它允许用户将内网设备的服务端口映射到公网,使外网用户可以访问内网中的服务。这项技术在远程办公、设备远程控制、游戏

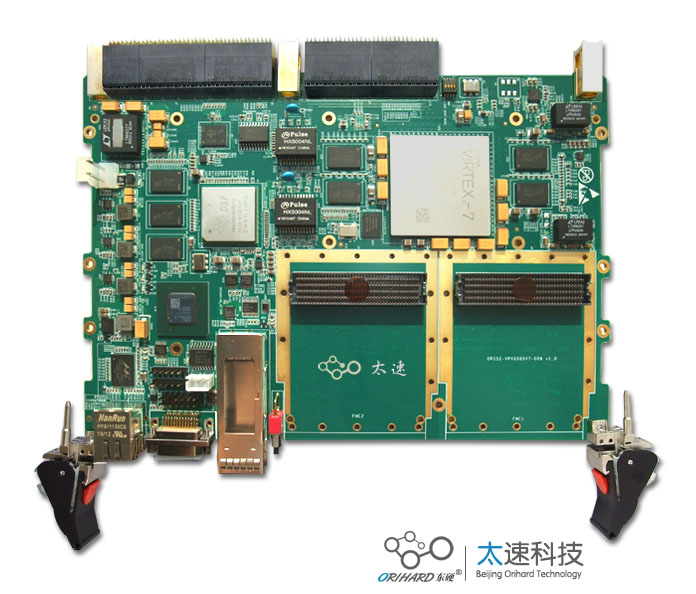

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信号处理卡

本板卡基于标准6U VPX 架构,为通用高性能信号处理平台,系我公司自主研发。板卡采用一片TI DSP TMS320C6678和一片Xilinx公司Virtex 7系列的FPGA

如何将自定义逻辑从FPGA/CPLD迁移到C2000™微控制器

电子发烧友网站提供《如何将自定义逻辑从FPGA/CPLD迁移到C2000™微控制器.pdf》资料免费下载

发表于 09-23 12:36

•0次下载

兼容7A100T和PG2L100H双芯核心板,米尔FPGA平台

不同需求

MYIR推出FPGA 开发平台具有极高的灵活性,用户可以根据项目需求自由选择AMD XC7A100T 和紫光同创 PG2L100H 这两款核心板,共享同一底板平台,可以实现无

发表于 09-14 16:08

在单个C2000™MCU上使用FCL和SFRA进行双轴电机控制

电子发烧友网站提供《在单个C2000™MCU上使用FCL和SFRA进行双轴电机控制.pdf》资料免费下载

发表于 09-14 09:40

•0次下载

FPGA核心板 Xilinx Artix-7系列XC7A100T开发平台,米尔FPGA工业开发板

MYC-J7A100T核心板及开发板Xilinx Artix-7系列XC7A100T开发平台,FPGA工业芯XC

发表于 05-31 15:12

•10次下载

能否建议通过内存映射提高aur性能?

我们使用英飞凌 Aurix TC364 作为平台。 我们试图通过将 ISR 映射到不同的内存单元来提高 ISR 函数的性能,具体方法是使用 #pragma section code

发表于 05-29 07:39

简谈Xilinx Zynq-7000嵌入式系统设计与实现

)和可编程逻辑资源集成在单个芯片中,产生了一种全新的设计平台,我们称之为全可编程片上系统(ALL Programmable System-on-chip,APSoC).

SoC的

发表于 05-08 16:23

STM8S105的TIM1_CH4重映射到了PD7之后,为什么PC4仍然有PWM输出?

STM8S105的TIM1_CH4重映射到了PD7之后,为什么PC4仍然有PWM输出

要想PC4回复为正常的GPIO还要怎么设置?

发表于 05-07 08:21

STM8S105的TIM1_CH4重映射到了PD7之后,为什么PC4仍然有PWM输出呢?

STM8S105的TIM1_CH4重映射到了PD7之后,为什么PC4仍然有PWM输出

发表于 04-29 06:16

中高端FPGA如何选择

为了使数据传输更加高效,Achronix FPGA上的Memory资源也是非常给力,不管是片上Ram还是DDR接口,都比Virtex Ultrascale+有很大优势。

发表于 04-24 15:09

如何将复杂的SoC平台映射到单个Virtex-7 2000T FPGA上

如何将复杂的SoC平台映射到单个Virtex-7 2000T FPGA上

评论