CAN测试边沿时间意义

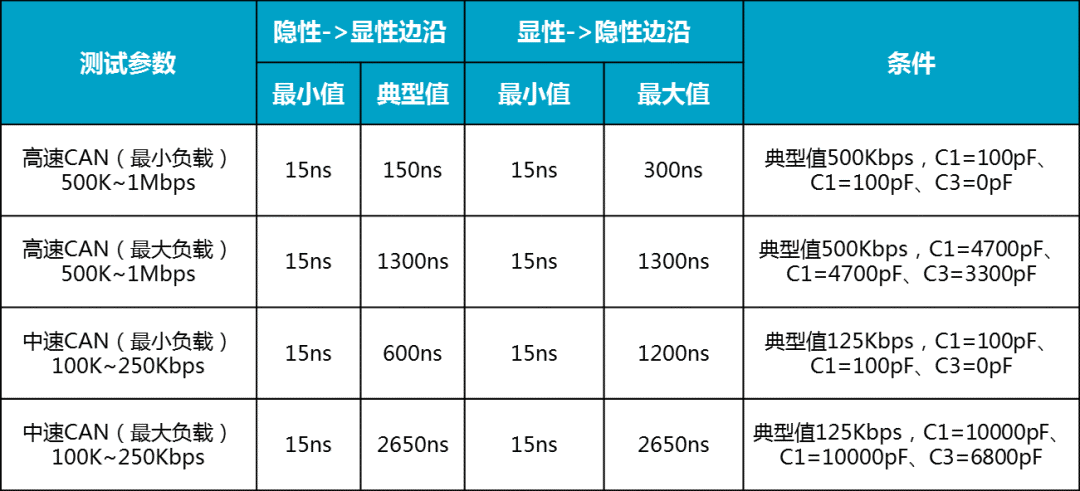

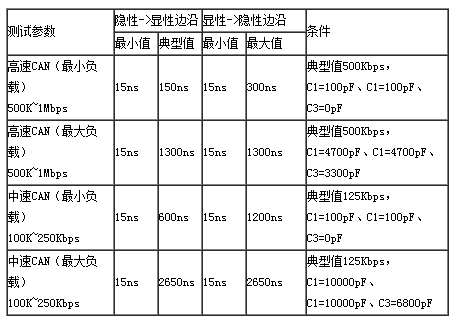

目前在国内汽车电子行业没有明确的标准,也就造成汽车零配件质量良莠不齐,零配件整装到汽车上将会造成CAN总线通信异常,给汽车驾驶带来安全隐患。如下是GMW3122信号边沿标准对CAN总线边沿的规范要求。

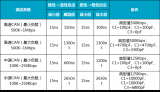

表中根据需求不同,波特率不同分为高速CAN、中速CAN。测试的是信号边沿时间,边沿时间是指隐性电平到显性电平时间和显性电平到隐性电平变化的总时间。隐性电平(逻辑值0)到显性电平(逻辑值1)时间为上升沿,显性电平到隐性电平为下降沿。

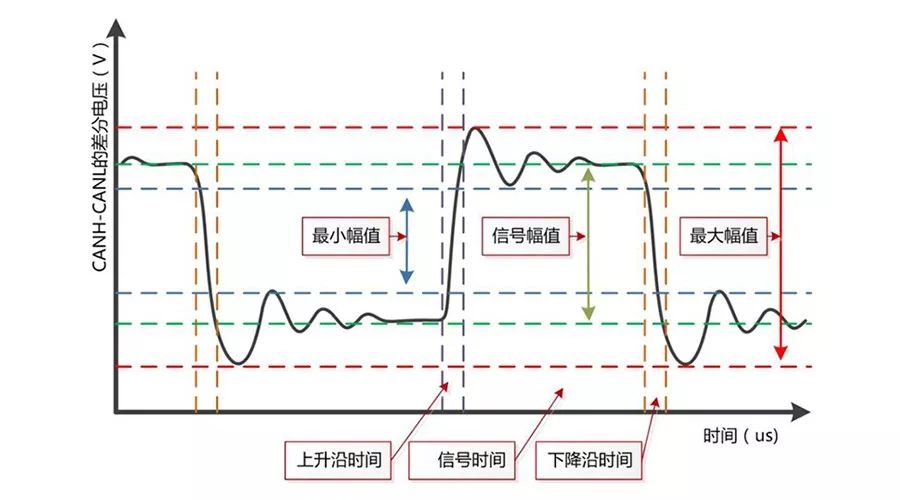

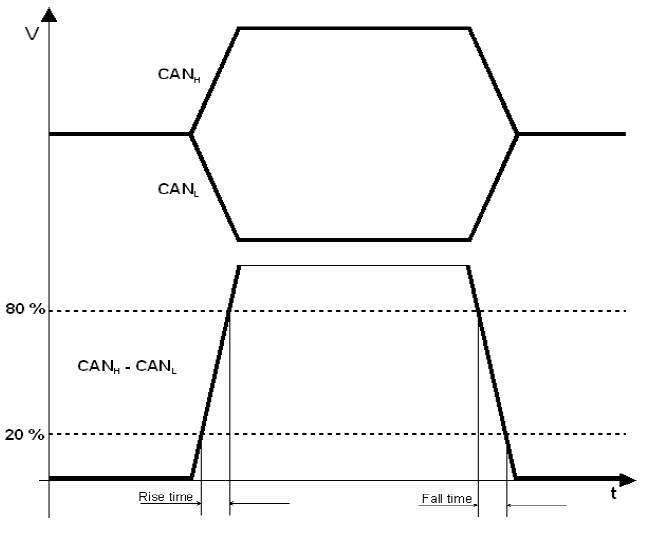

边沿时间分为上升沿时间、下降沿时间。下降沿时间是按照电压(20%~80%电压区间,有些按照10%~90%电压区间测量边沿时间,文中以20%~80%电压区间测量边沿时间)。表中给出时间范围,如果超出规定时间,会造成波形位宽增加,采样点取值不准确,波特率异常,出现大量错误帧,一直重发数据帧也会造成CAN总线通信瘫痪。

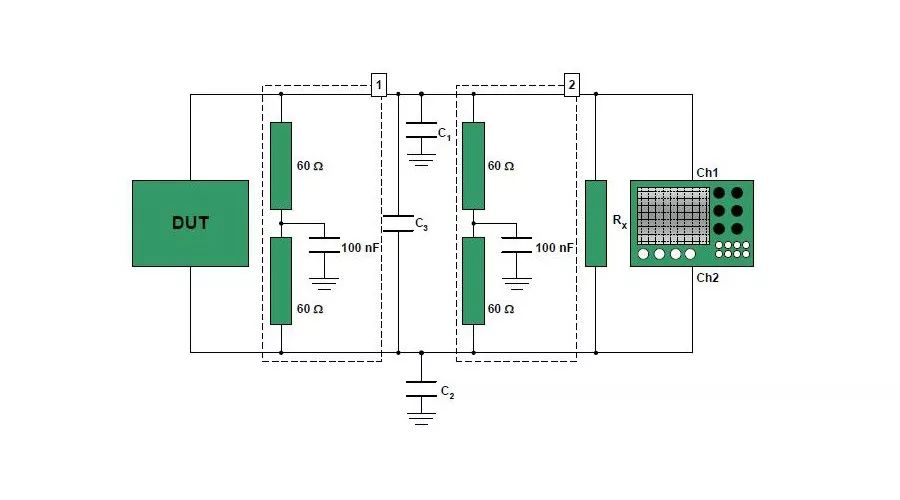

由于现场总线过长,导致总线上挂载电容增加,从而导致线路阻抗增加。在边沿时间测试需要考虑电阻与电容匹配。模拟测试线路短,需要人为添加电容来模拟现场存在实际情况。在上表中典型值是根据现场电容、电阻得出的常用值。

CAN边沿时间测试步骤

1、示波器测试CAN波形

用示波器采集CAN总线波形,设置幅值光标为20%~80%,记录上升沿的时间、下降沿时间;

记录多次数据,确认每次求得上升沿、下降沿时间都在标准范围内。

2、CAN测试问题

只使用示波器测量CAN边沿时间,需要人为操作记录多次时间。整车CAN总线拥有多个零部件,测试CAN边沿时间需要花费大量时间以及人力,而这还只是整车CAN一致性测试的其中一项,完成全部测试要求,需要一个人测试三天。随着效率要求越来越高,整车厂更希望将时间花费在研发汽车应用新技术。

CANDT

基于汽车行业对CAN总线测试手段繁杂,ZLG致远电子自主研发的CANDT一致性测试系统,可构建CAN总线安全保障体系,自动化完成CAN总线物理层、链路层及应用层自动化测试。保证整车安全三步曲如下:

步骤一:CAN一致性自动化测试

通过将汽车或节点零部件接入CAN一致性测试系统,可自动化完成CAN总线物理层、链路层等自动化测试,覆盖主流主机厂标准要求,保障整车CAN总线安全稳定。

步骤二:详细测试报表导出

单节点测试完成之后,可自动化到处详细CAN一致性测试报表,其包含测试标准引用,评判依据,判断结果等数据,准确判断节点工作情况,一目了然,可作为主机厂准入依据。

步骤三:CAN总线故障定位及排查解决

新能源汽车主机厂和零部件企业在CANDT一致性测试后,对于测试报告中显示测试不通过的问题,可以用CANScope进行故障定位和排查,加快CAN总线稳定的研发速度。

测试结果:保障整车CAN网络安全

新能源汽车CAN节点在通过一致性测试后,质量高度一致,避免了CAN节点良莠不齐带来的安全隐患问题,从而保证了整车CAN网络的安全统一。

-

新能源汽车

+关注

关注

141文章

10662浏览量

100383 -

CAN总线

+关注

关注

145文章

1958浏览量

131226

发布评论请先 登录

相关推荐

CAN总线信号传输的位定时与位同步理论

CAN总线冷知识-边沿台阶是怎么来的?

CAN信号不稳定?“罪魁祸首”边沿台阶不可忽视

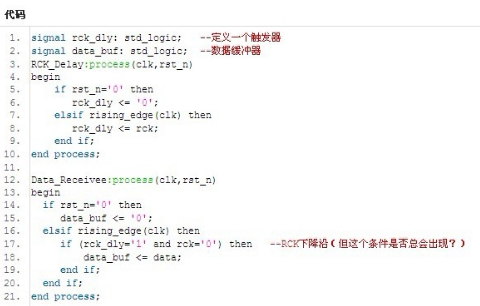

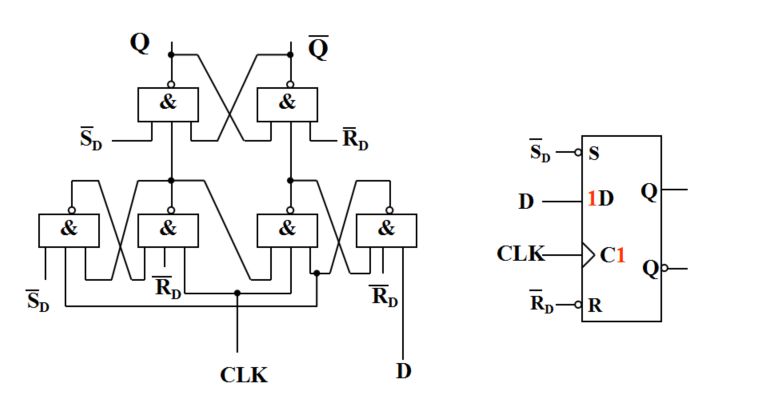

CMOS触发器在CP边沿的工作特性研究

边沿触发SR触发器

什么是边沿触发器_边沿D触发器介绍

基于CAN节点的信号边沿参数测量方案

CAN差分波形的边沿如此缓慢怎么办?

那么CAN总线边沿时间标准是什么 如何测量边沿时间

那么CAN总线边沿时间标准是什么 如何测量边沿时间

评论