在高速PCB设计流程里,叠层设计和阻抗计算是登顶的第一梯。阻抗计算方法很成熟,不同软件的计算差别不大,相对而言比较繁琐,阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到我们阻抗管控目的的同时,也能保证工艺加工的方便,以及尽量降低加工成本。

下面百能网小编总结了一些设计叠层算阻抗是的注意事项,帮助大家提高计算效率。

1,线宽宁愿宽,不要细。

因为制程里存在细的极限,宽是没有极限的,所以如果后期为了调阻抗把线宽调细而碰到极限时那就麻烦了,要么增加成本,要么放松阻抗管控。所以在计算时相对宽就意味着目标阻抗稍微偏低,比如单线阻抗50ohm,我们算到49ohm就可以了,尽量不要算到51ohm。

2,整体呈现一个趋势。

我们的设计中可能有多个阻抗管控目标,那么就整体偏大或偏小,不要出现类似100ohm的偏大,90ohm的偏小这种不同步偏大偏小的情况。

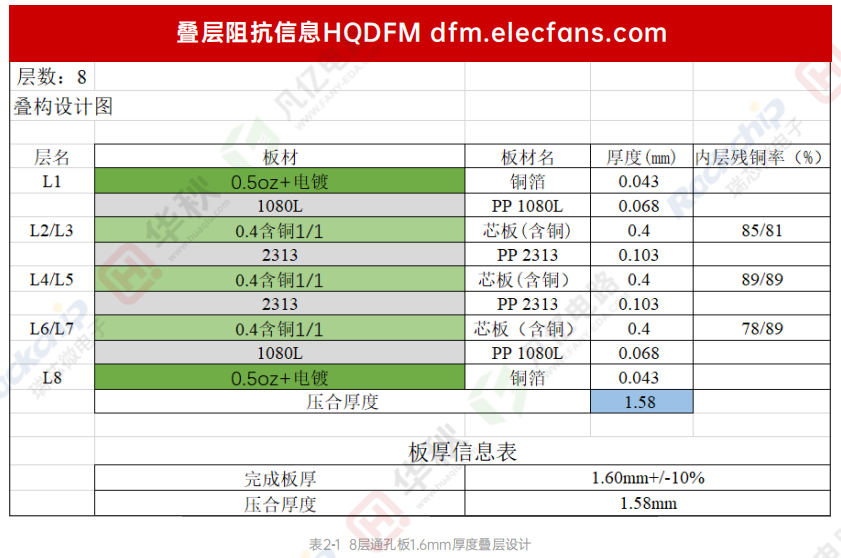

3,考虑残铜率和流胶量。

当半固化片一边或两边是蚀刻线路时,压合过程中胶会去填补蚀刻的空隙处,这样两层间的胶厚度时间会减小,残铜率越小,填的越多,剩下的越少。所以如果需要的两层间半固化片厚度是5mil,要根据残铜率选择稍厚的半固化片。

4,指定玻布和含胶量。

不同的玻布,不同的含胶量的半固化片或芯板的介电系数是不同的,即使是差不多高度的也可能是3.5和4的差别,这个差别可以引起单线阻抗3ohm左右的变化。另外玻纤效应和玻布开窗大小密切相关,如果是10Gbps或更高速的设计,而叠层又没有指定材料,板厂用了单张1080的材料,那就可能出现信号完整性问题。

当然残铜率流胶量计算不准,新材料的介电系数有时和标称不一致,有的玻布板厂没有备料等等都会造成设计的叠层实现不了或交期延后。那么最好的办法就是在设计之初让板厂按我们的要求,加上他们的经验设计叠层,这样最多几个来回就能得到理想又可实现的叠层了。

-

pcb

+关注

关注

4335文章

23247浏览量

402354 -

阻抗

+关注

关注

17文章

962浏览量

46502 -

可制造性设计

+关注

关注

10文章

2065浏览量

15804 -

华秋DFM

+关注

关注

20文章

3495浏览量

4908

原文标题:PCB设计中叠层算阻抗时需注意的四大事项

文章出处:【微信号:ruziniubbs,微信公众号:PCB行业工程师技术交流】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RK3588 PCB推荐叠层及阻抗设计

PCB设计中叠层设计和阻抗计算需要注意的4点

PCB设计中叠层设计和阻抗计算需要注意的4点

评论