本文主要参考自《MICROCONTROLLER DESIGN GUIDELINES FOR ELECTROMAGNETIC COMPATIBILITY》,此文虽然写在多年前,不过有很多很现实的参考意义。另外别的IC厂商也有很多的参考文档,如果大家有兴趣可以参考一下。 题外话,写这个话题主要是去剖析模块内部主要的干扰源和敏感器件,通过这些主要的东西的设计来慢慢体会模块的EMC设计,不过难免有些一鳞半爪之嫌,积累 多了可能未来在设计电路的时候在前期就很容易把问题考虑周到和细致。

1、单片机的工作频率

1.1单片机的设计应根据客户的需求来选择较低的工作频率

首先介绍一下这样做的优点:采用低的晶振和总线频率使得我们可以选择较小的单片机满足时序的要求,这样单片机的工作电流可以变得更低,最重要的是VDD到VSS的电流峰值会更小。

当然我们这里需要做一个妥协,因为客户的要求可能是兼容的和平台化的(目前汽车电子的发展趋势就是平台化),选择较高的工作频率可以兼容更多的平台,也方便以后升级和扩展,因此要选择一个较低的可以接受的工作频率。

2、恰当的输出驱动能力

在给定负载规范,上升和下降时间,选择适当的输出的上升时间,最大限度地降低输出和内部驱动器的峰值电流是减小EMI的最重要的设计考虑因素之一。驱动能 力不匹配或不控制输出电压变化率,可能会导致阻抗不匹配,更快的开关边沿,输出信号的上冲和下冲或电源和地弹噪声。

2.1设计单片机的输出驱动器,首先确定模块需求的负载,上升和下降的时间,输出电流等参数,根据以上的信息驱动能力,控制电压摆率,只有这样才能得到符合模块需求又能满足EMC要求。

驱动器能力比负载实际需要的充电速度高时,会产生的更高的边沿速率,这样会有两个缺点

1.信号的谐波成分增加了。

2.与负载电容和寄生内部bonding线,IC封装,PCB电感一起,会造成信号的上冲和下冲。

选择合适的的di/dt开关特性,可通过仔细选择驱动能力的大小和控制电压摆率来实现。最好的选择是使用一个与负载无关的恒定的电压摆率输出缓冲器。同样的 预驱动器输出的电压摆率可以减少(即上升和下降时间可以增加),但是相应的传播延迟将增加,我们需要控制总的开关时间)。

2.2使用单片机的可编程的输出口的驱动能力,满足模块实际负载要求。

可编程的输出口的驱动器的最简单是的并联的一对驱动器,他们的MOS的Rdson不能,能输出的电流能力也不相同。我们在测试和实际使用的时候可以选择不同的模式。实际上目前的单片机一般至少有两种模式可选择,有些甚至可以有三种(强,中等,弱)

2.3当时序约束有足够的余量的时候,通过降低输出能力来减缓内部时钟驱动的边沿。

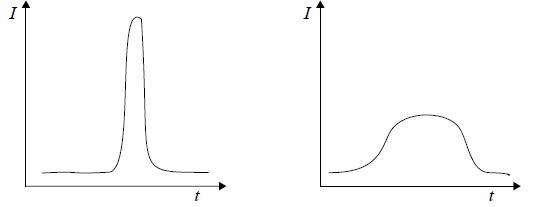

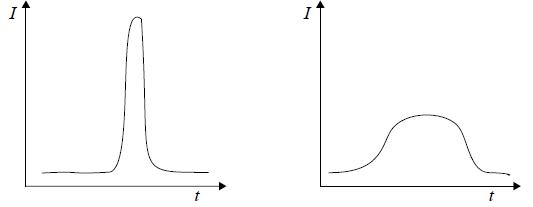

减少同步开关的峰值电流,和di/dt,一个重要的考虑因素就是降低内部时钟驱动的能力(其实就是放大倍数,穿通电流与之相关型很大)。降低时钟边沿的电 流,将显著改善EMI。当然这样做的缺点就是,由于时钟和负载的开通时间的变长使得单片机的平均电流可能增加。快速边沿和相对较高的峰值电流,时间更长边 沿较慢的电流脉冲这两者需要做一个妥协。

2.4晶振的内部驱动(反向器)最好不要超过实际的需求。

这个问题,实际上前面也谈过了,当增益过大的时候会带来更大的干扰。

3、设计最小穿通电流的驱动器

3.1 时钟,总线和输出驱动器应尽可能使得传统电流最小

穿通电流【重叠电流,短路电流】,是从单片机在切换过程中,PMOS和NMOS同时导通时候,电源到地线的电流,穿通电流直接影响了EMI和功耗。

这个内容实际上是在单片机内部的,时钟,总线和输出驱动器,消除或减少穿通电流的方法是尽量先关闭一个FET,然后再开通一个FET。当电流较大时,需要额外的预驱动电路或电压摆率。

4、时钟的生成和分配

4.1就单片机内部而言,我们宁可给每个部分分配时钟(尽可能小的高频时钟),当然我们需要额外的管理时钟偏移工作。这样做要比使用一个增益很大的的时钟缓冲器,驱动整个IC的时钟好很多

同步CMOS的设计,在时钟边沿产生很大的峰值电流。时钟树的结构使用(在系统时间允许的条件下),比起主时钟驱动器和时钟分配线路,将减少同步开关电流。【时钟树结构中固有的延迟时间使得开关在不同时间分离开来】

4.2使用电源管理技术。

把时钟源尽可能靠近需要的IC,如果在一个模块内需要分配时钟的话。在不需要时钟的时候,关闭时钟源。【睡眠模式的时候通常需要做时钟的切换】

4.3在系统的限制允许的条件下,尽量使用非重叠时钟。

非重叠时钟,是指没有同步边缘的时钟。从系统的角度来说,非重叠的时钟边沿有助于消除竞争冒险和亚稳态。从EMC的角度看,加入时钟边沿之间的过渡时间会降低峰值电流和谐波的峰值幅度。平均电流从时间跨度上来看将保持大致相同,但幅度和频谱形状会发生变化。

如果时钟间的过渡是接近的但不同步(假设边沿速度相对于时钟周期要快得多),电流波形会变平和持续时间会变长。随着过渡时间的增加,对每个边沿来说到电流波形会分离成若干个脉冲。较低的脉冲幅度相应降低了谐波的频谱幅度,电流脉冲边沿很可能依然大致相同(维持脉冲带宽)。理想情况下,两相系统中非重叠的占空比为33%,最大限度地加大时钟边沿之间的时间。然而,实际应用中不可能使用这种方式,必须做一些妥协,实际系统中不容许时钟边沿的有这么大的跨度。

4.4使时钟电路尽量远离I / O逻辑电路,减少共模辐射问题发生的可能性。

时钟信号需要远离I / O逻辑或平行的引线。时钟暂态边沿可以耦合到I / O逻辑,产生电压的噪声。

4.5 输入引脚同步器移动远离单片机引脚区域,进入单片机的核心模块。

这项方法可以减少所需的时钟驱动器的大小,

移动同步器靠近时钟源可减少时钟信号线路长度。时钟驱动器上的电容负载部分取决于引线的寄生电容的,时钟驱动充电负荷将变小。

-

单片机

+关注

关注

6036文章

44556浏览量

634990 -

VDD

+关注

关注

1文章

312浏览量

33211 -

VSS

+关注

关注

1文章

35浏览量

21445

原文标题:单片机设计初期EMC的一些建议!

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

技巧:对单片机EMC设计的几点建议

弱弱的小建议

51系列单片机设计实例下载

单片机EMC设计的几点建议

挑选伺服电机厂家的小建议

单片机设计初期EMC的一些建议!

提几点单片机设计初期EMC的小建议

提几点单片机设计初期EMC的小建议

评论