LLC的优势之一就是能够在比较宽的负载范围内实现原边MOSFET的零电压开通(ZVS),MOSFET的开通损耗理论上就降为零了。要保证LLC原边MOSFET的ZVS,需要满足以下三个基本条件:

1)上下开关管50%占空比,1800对称的驱动电压波形;

2)感性谐振腔并有足够的感性电流;

3)要有足够的死区时间维持ZVS。

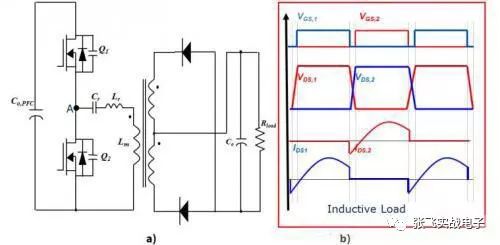

图a)是典型的LLC串联谐振电路。图b)是感性负载下MOSFET的工作波形。由于感性负载下,电流相位上会超前电压,因此保证了MOSFET运行的ZVS。要保证MOSFET运行在感性区,谐振电感上的谐振电流必须足够大,以确保MOSFET源漏间等效的寄生电容上存储的电荷可以在死区时间内被完全释放干净。

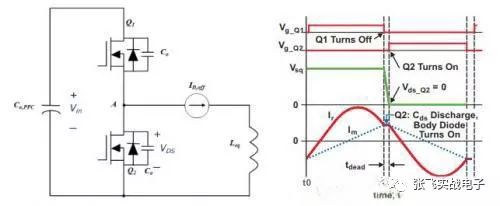

当原边的MOSFET都处于关断状态时,串联谐振电路中的谐振电流会对开关管MOSFET的等效输出电容进行充放电。MOSFET都关断时的等效电路如下图所示:

通过对上图的分析,可以得出需要满足ZVS的两个必要条件,如下:

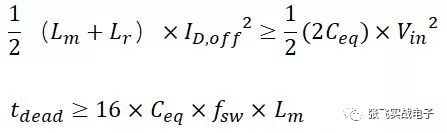

公式看上去虽然简单,然而一个关于MOSFET等效输出电容Ceq的实际情况,就是MOSFET的等效寄生电容是源漏极电压Vds的函数,之前的文章对于MOSFET的等效寄生电容进行过详细的理论和实际介绍。,也就是说,等效电容值的大小会随着Vds的变化而变化。如下图所示,以Infineon的IPP60R190P6为例:

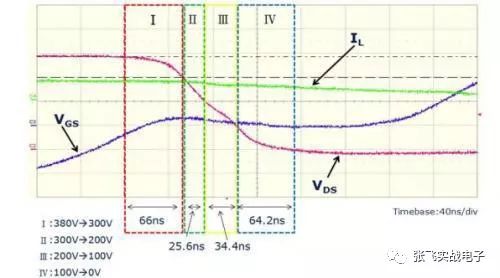

LLC串联谐振电路MOSFET的Vds放电过程分为四个阶段,如下图所示, (I) 380V-300V; (II) 300V-200V; (III) 200V-100V; (IV)100V-0V。

从图中可以看出,(I)和(IV)两部分占据了Vds放电时间的将近2/3,此时谐振腔的电感电流基本不变。这两部分之所以占据了Vds放电的大部分时间,主要原因在于当Vds下降到接近于0的时候,MOFET源漏间的寄生电容Coss会指数的增加。因此要完全释放掉这一部分的电荷,需要更长的LLC谐振周期和释放时间。

因此选择合适的MOSFET(足够小的等效寄生电容),对于ZVS的实现至关重要,尤其是当Vds接近于0的时候,等效输出电容要足够小,这样还可以进一步降低死区时间并提高LLC的工作效率。

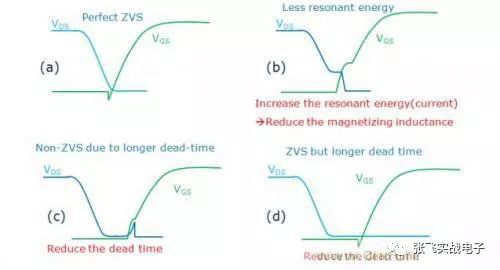

下图进一步说明如何选择合适的ZVS方案。

图(a):理想的ZVS波形;

图(b):Vds还没下降到0,Vgs已经出现。此种情况下,LLC串联谐振就会发生硬开关。应对之策需要减少变压器的励磁电流,或者适当增加死区时间(如果IC选定,死区时间一般就固定了);

图(c):实现了ZVS,但是谐振腔的电流不足以维持MOSFET体内二极管的持续导通。

图(d)死区时间过于长了,会降低整个LLC的工作效率。

总之,MOSFET的等效输出电容对于LLC原边MOSFET ZVS的实现是至关重要的。如果MOSFET已经选定,谐振腔需要仔细计算、调试和设定,并选取合适的死区时间,来覆盖所有负载的应用范围。实际应用中对于稳态运行的硬开关都可以通过设计进行修正从而达到稳定运行的设计目的。然而开机过程中的硬开关(软启高频到低频过程中),尤其是开机过程中的头几个开关周期,对于有些设计和方案,硬开关是避免不了的。

-

MOSFET

+关注

关注

147文章

7203浏览量

213686 -

谐振电路

+关注

关注

11文章

165浏览量

27001 -

LLC

+关注

关注

36文章

568浏览量

76867 -

张飞电子

+关注

关注

54文章

175浏览量

12606

原文标题:MOSFET电容对LLC串联谐振电路的作用

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

浅析基于碳化硅MOSFET的谐振LLC和移相电路在新能源汽车的应用

如何排除LLC谐振转换器中出现的MOSFET故障?

LLC电路中的MOSFET

MOSFET电容在LLC串联谐振电路中的作用

浅析MOSFET电容在LLC串联谐振电路中的应用

浅析MOSFET电容在LLC串联谐振电路中的应用

评论