在电机驱动的FOC控制开发过程中,您是否遇到过电机噪声过大、效率偏低甚至无法运转的情况?这一切有可能源于相电流的采样异常,从而导致FOC算法中无法重建正确的三相电流!小编这里给大家分析影响电流采样的一个因素——延迟源!1

引言

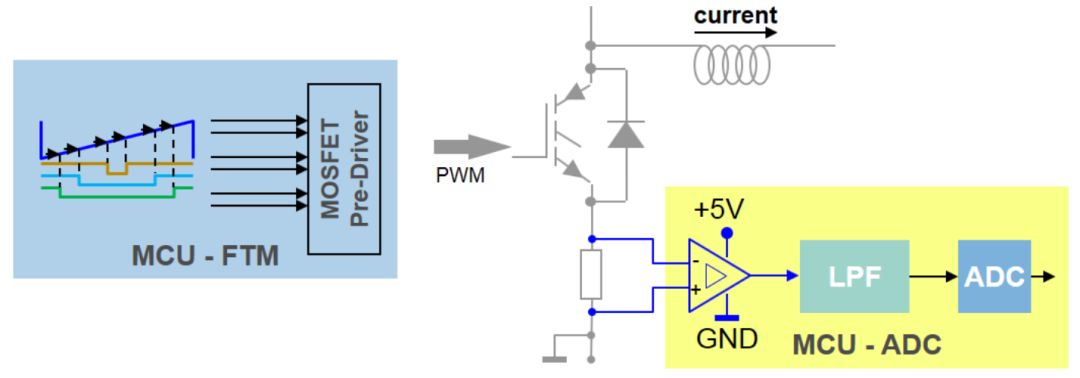

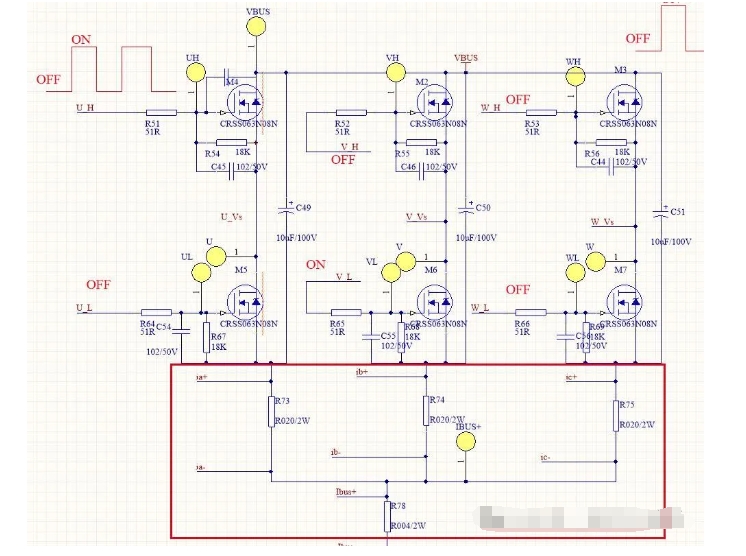

在双电阻采样的电机驱动FOC控制中,采样点设置为驱动桥下管打开的中间时刻。注意,这里是驱动桥下管打开的中间时刻,而不是MCU输出的PWM周期中间时刻。因为从MCU计算生成PWM到电流信号送入MCU的ADC模块,这个典型的驱动拓扑中,存在多达七个延迟源!

2

延迟类型及典型时间

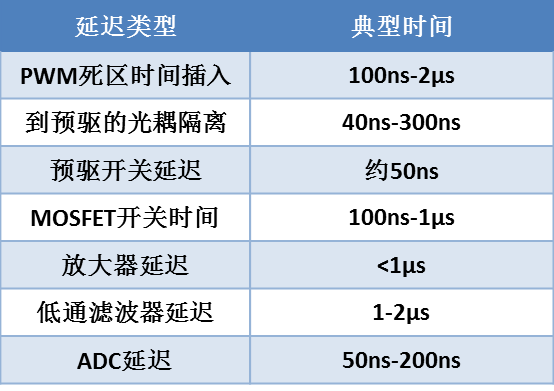

下面表格详细指明了电机驱动系统拓扑中存在的七个延迟源及其典型的时间。这些延迟将叠加在一起,产生的影响是:实际输出PWM波形滞后于MCU计算预期输出的PWM波形,按照这个计算,相电流采样点需要滞后于MCU计算预期输出的PWM波形的中间时刻。

3

延迟源详细分析

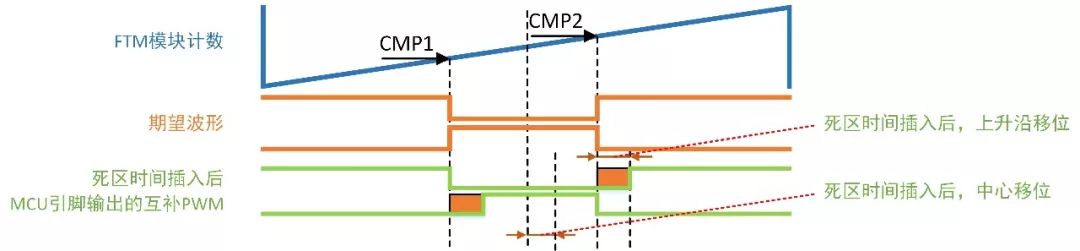

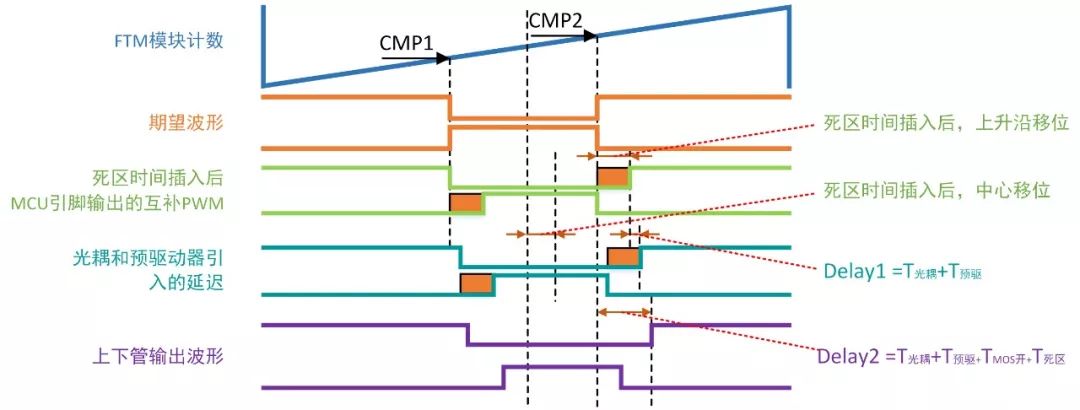

3.1PWM死区时间插入

在三相无刷电机驱动系统中,需要三个桥臂来控制相线电流流向,在每个桥臂上有两个功率器件,如MOSFET、IGBT。这一对功率器件不能同时导通,否则就会出现短路的情况。这里以MOSFET作为功率器件来说明。在控制中,必须插入死区时间以确保上部和下部MOSFET不会同时处于打开状态。死区时间的典型值可能在100ns到2μs之间,具体取决于系统中的各种因素,如MOSFET驱动电压、MOSFET型号。

在所需的PWM波形插入死区时间之后,我们得到的是PWM中点和上升沿都向右移动。因此,在FOC控制算法计算出适当的PWM之后,我们立即开始看到第一个延迟,即死区时间。

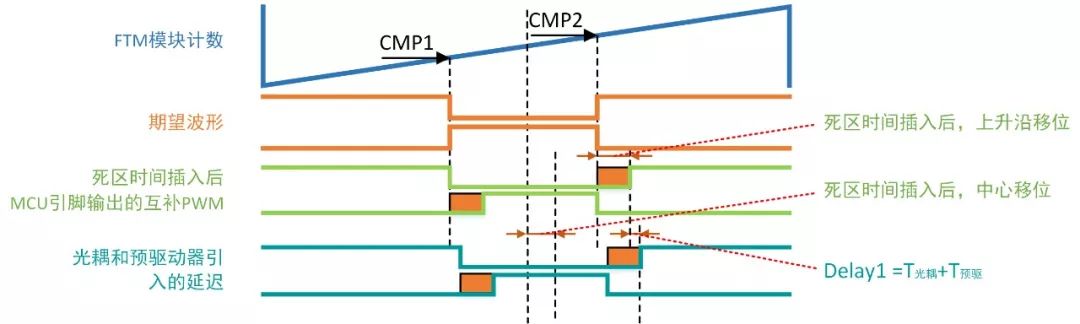

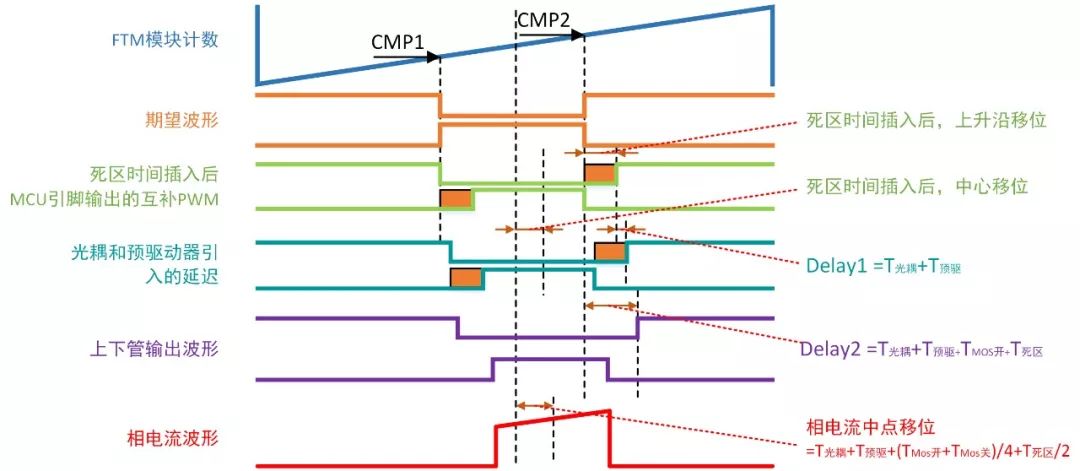

在MCU控制FTM模块输出PWM波形到MOSFET栅极受控制的那一刻之间,各种光电耦合器和预驱动器的信号响应导致了额外的延迟。

与MCU引脚输出的波形相比,预驱动器的输出延迟了一段时间(Delay1)。

3.3晶体管开关延迟

经过预驱动器后,PWM波形到达MOSFET晶体管,但由于其固有特性,所有晶体管都需要一定的时间导通和截止。根据晶体管类别及导通/截止之间切换所需要的电压电平,此延迟时间有所不同。

Delay2为相线电压理论切换点(CMP2)与实际切换点的时刻之间的整个延迟。

最后,栅极电压到达了能令晶体管导通的程度,电流通过相线和采样电阻,在采样电阻两端产生电压差,红色波形为理想状态下的相电流波形。此时与MCU计算生成的PWM周期中点存在延迟总时间如图中“相电流中点移位”。

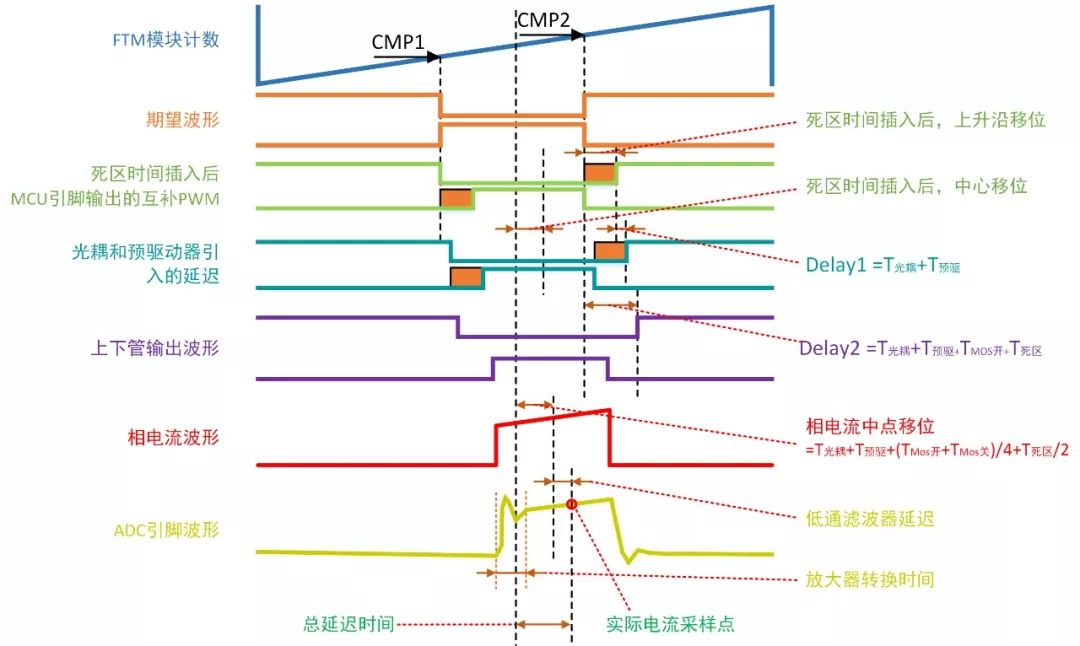

3.4其他延迟

如下图所示,影响电流采样的最后延迟链是由放大器转换速率、MCU引脚上的低通滤波器和ADC转换速率构成的。图中用红色圆圈标记的时刻为正确的电流采样时刻,可以看出,与FTM输出的PWM中点相比,相电流采样点大大延迟。

4

结语

所有的电子电路中,都会存在信号的延迟问题。信号延迟不可能被完全消除,但可通过选用低延迟的器件以减小影响。

在电机驱动中,除了选用合适的器件外,还需要对信号延迟进行软件补偿。文中提及的这些延迟源的精确延迟时间,我们可以通过示波器和计算得出,在软件上补偿这些延迟,才可得出正确的电流采样时刻。这样在正确的时刻采集到的数据才能作为FOC控制中重建电机三相电流的数据来源。

-

PWM

+关注

关注

114文章

5181浏览量

213810 -

电机驱动

+关注

关注

60文章

1216浏览量

86724

原文标题:FOC电流采样为什么不准?你忽略了这个细节

文章出处:【微信号:Zlgmcu7890,微信公众号:周立功单片机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

影响电流采样的一个因素——延迟源!

影响电流采样的一个因素——延迟源!

评论