自摩尔定律被提出到现在,它已经伴随着半导体产业走过了半个多世纪,这个规律揭示了信息技术进步的神速,它让人们相信,IC制程技术是可以呈现直线式的发展,通过先进的工艺能让IC产品持续地降低成本,同时提升产品性能。但在今年,这样的想法或许被打破,业界对摩尔定律的怀疑声连绵不断,先是格芯宣布放弃7nm FinFET项目,随后英特尔延缓7nm工艺的研究进程等等,这些动作凸显了企业对行业新的看法。未来几年,摩尔定律是否会真的消失?它是否会改变如今的产业格局?这个不好说,但是放缓的节奏是不可否认的,摩尔定律的变化,给半导体产业带来了很多的不确定性,这也给eFPGA带来了发展机遇。

eFPGA迎来了发展良机

对于业界而言,eFPGA并非一种新的技术,早在十多年前就已经出现过,它是嵌入式的FPGA技术。大家对FPGA技术更熟悉,FPGA和ASIC芯片都是应用非常广泛的,但一直以来,似乎ASIC芯片才是真正的市场主流,并非是FPGA技术的原因,而是它们的制造成本和应用场景所致,相对而言,FPGA或eFPGA的成本更高,除非有特定的场景需求,客户并不愿意采用价格更昂贵的技术。

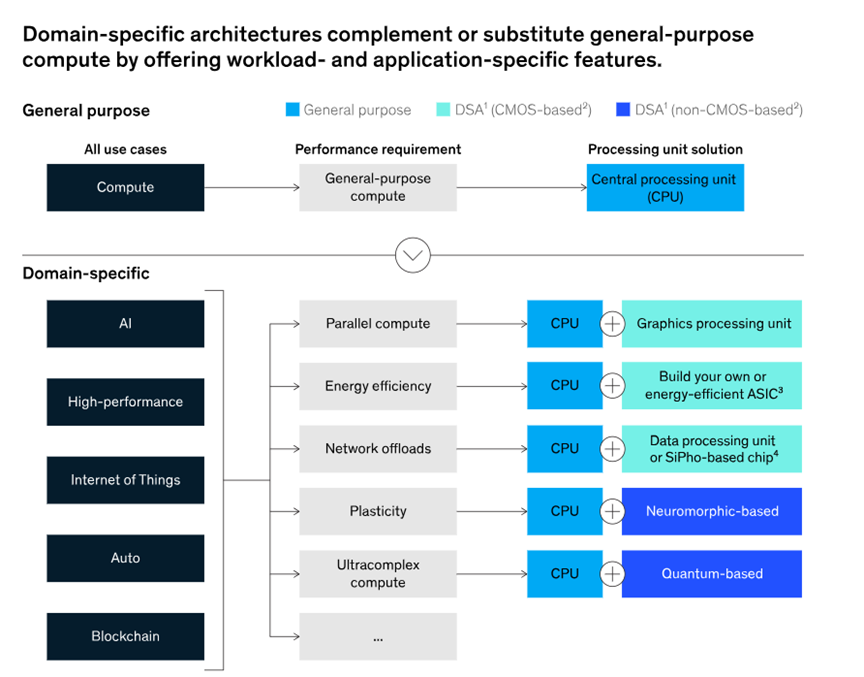

随着芯片技术的发展,ASIC芯片也出现了发展瓶颈,材料和架构的局限让它们很难满足某些场景,如AI带来的算力需求、机器学习应用以及云计算等,大数据和物联网的进步,带来了更大的运算需求,eFPGA重新成为市场的香饽饽,这种全新的、异构的、自带可编程硬件加速器的新技术成为推动半导体产业向前的关键驱动力。

据OFweek电子工程网获悉,目前市面上提供完整的eFPGA技术解决方案的公司并不多,Achronix是其中的佼佼者,它们刚刚入围全球半导体联盟2018年最受尊敬的私有半导体公司奖,具备将eFPGA技术嵌入到ASIC芯片中实现量产的能力,Achronix的Speedcore是业界首款向客户出货的eFPGA IP产品。

eFPGA技术的优势和应用

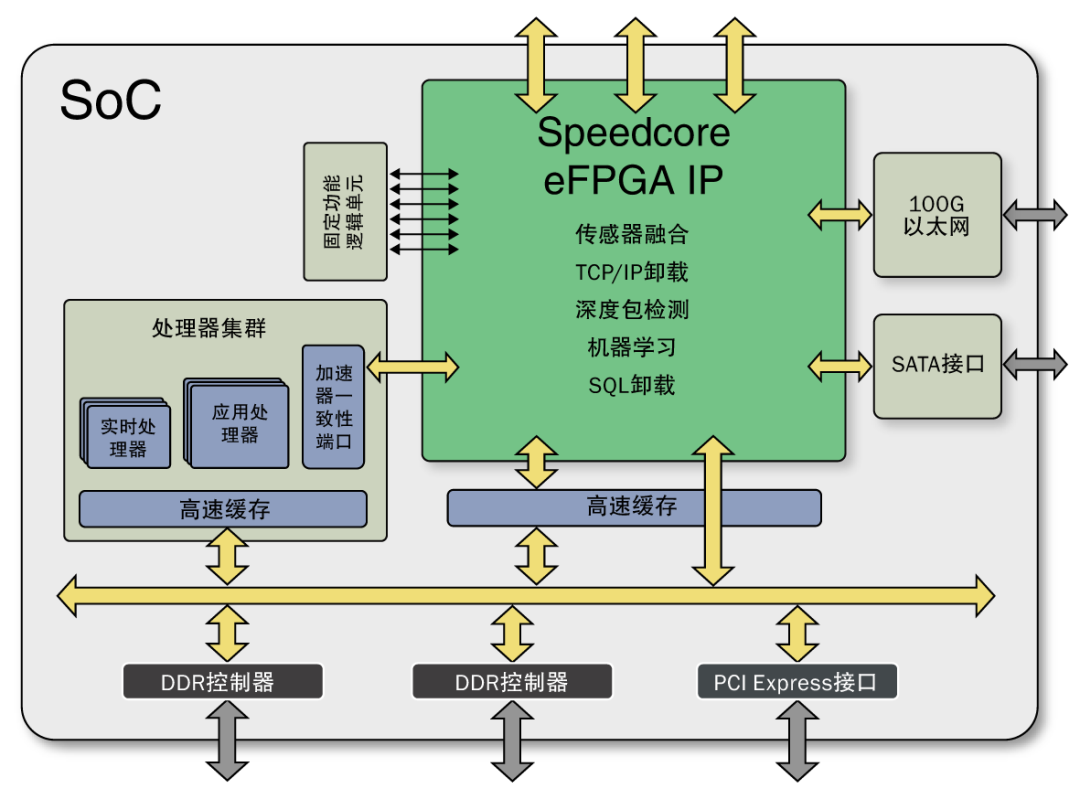

随着人工智能和机器学习等对大数据处理能力的更高要求,处理器核心数量的增加并不能带来计算能力的成倍增长,而eFPGA的SoC不仅可以更快速地进行数据处理,同时功耗也更低。但想把FPGA嵌入到SoC中并不是一件简单的事情,不仅需要拥有FPGA经验,更需要有IP集成的经验。Achronix是第一家提供带有嵌入式系统级别IP的高密度FPGA的供应商,因此使用相同的、经过验证的技术最终推出了eFPGA产品。

“Achronix很高兴能够走在嵌入式FPGA市场的最前沿,该技术正在迅速地成为许多需要硬件加速的应用的首要选择”,Achronix市场营销副总裁Steve Mensor说道。“这些全新的eFPGA Accelerator应用加速项目将使创新的公司和研究机构能够使用我们的IP和工具去构建下一代的可编程芯片,从而满足AI / ML和其他计算密集型应用不断增长的数据和计算量需求。”

人工智能和机器学习的加速器

针对人工智能的应用特点,eFPGA技术提供了一种新的解决方案,利用它在自定义处理器和内存管理技术的优点,嵌入式可编程逻辑通过消除对面积大、功耗高的I/ O电路的需求,缩减了芯片的总面积。Achronix亚太区总经理罗炜亮表示,Achronix的Speedster等许多FPGA架构提供了完全可自定义的逻辑和数字信号处理引擎的混合结构,它们可支持固定和浮点运算,DSP引擎可采用由8位或16位单元来组成一种构建模块,这种方法可以将它们组合起来以支持更高精度的数据类型,通过用逻辑阵列中的查找表来实现相关逻辑也能够适用于低精度。Achronix的Speedcore可集成在芯片上的嵌入式FPGA半导体知识产权模块。

除了计算和网络基础设施的通用要求之外,人工智能/机器学习还对高密度和针对性计算产生了显著增加的需求,MLP模块是一种高度灵活的计算引擎,它与存储器紧密耦合,从而为人工智能和机器学习应用提供了性能/功耗比最高和成本最低的解决方案。

Steve Mensor表示,与以前的Achronix FPGA产品相比,新的Achronix机器学习处理器利用了人工智能/机器学习处理的特定属性,并将这些应用的性能提高了300%。这是通过多种架构性创新来实现的,这些创新可以同时提高每个时钟周期的性能和操作次数。他提到,Achronix推出的用于人工智能、机器学习和网络硬件加速应用的第四代Speedcore eFPGA IP产品,与之前一代的Speedcore eFPGA产品相比,Speedcore Gen4的性能提速60%、功耗降低50%、芯片面积缩小65%;新的机器学习处理器单元模块为人工智能/机器学习应用提供高出300%的性能。这些机器学习处理器支持各种定点和浮点格式,包括Bfloat16、16位、半精度、24位和单元块浮点,用户可以通过为其应用选择最佳精度来实现精度和性能的均衡。

eFPGA技术被称为最佳的硬件加速器

大数据和网络带来巨大的数据处理需求,传统的多核CPU和SoC需要可编程硬件加速器来预处理和卸载数据,从而提升其计算性能,对于低至中容量应用,独立的FPGA芯片是一种方便且实际的解决方案,对于高容量应用,eFPGA是最佳解决方案。Steve Mensor表示,要将FPGA嵌入到SoC中首先需要解决FPGA芯片的面积问题,标准的FPGA内核与可编程IO、控制器等面积比接近1:1,Achronix的Speedcoree FPGA直接连接至SoC,不仅能够将FPGA芯片面积减少一半,使FPGA能够嵌入到SoC中,还能够减小CB的尺寸、减少PCB的层数以及提高信号完整性。

Achronix市场营销副总裁Steve Mensor

Steve Mensor继续说道,Speedcore以内部连线方式直接连接至SoC,省去了在外置独立FPGA中可见的大型可编程输入输出缓冲,能耗得到了降低。Speedcore省去了对独立FPGA周边所有支持性元器件的需求,这些元器件包括电源调节器、时钟发生器、电平位移器、无源元件和FPGA冷却器件,成本也就相应的降低。

对于FPGA开发者而言,软件工具的重要性不言而喻,Achronix为客户提供ACE设计工具。Steve Mensor表示,Achronix的研究类eFPGA Accelerator应用加速项目和测试芯片类eFPGA Accelerator应用加速项目,将支持研究机构和测试芯片开发人员轻松地获得Achronix的Speedcore eFPGA技术的许可授权,该项许可包括对接预先配置的、经过流片验证的Speedcore eFPGA IP以及该公司业内一流的ACE设计工具。

最后,Steve Mensor提到,Achronix已经可以提供基于台积电(TSMC)的16纳米FinFETPlus(16FF)工艺的SpeedcoreIP产品,并且正在开发基于台积电的7纳米工艺的IP。

总结:

随着机器学习和人工智能的发展,市场对芯片算力的要求与日俱增,厂商在架构和工艺上提升性能的瓶颈逐渐出现,新的FPGA技术可以帮助它们解决这些难题,Achronix的eFPGA技术在性能和功耗上找到了一个平衡点,解决了企业的难题。高性能计算将成为主流的应用,未来eFPGA技术定会在市场上大放异彩,市场份额逐渐增加。

-

摩尔定律

+关注

关注

4文章

634浏览量

79084 -

efpga

+关注

关注

1文章

33浏览量

15683

原文标题:摩尔定律放缓,eFPGA技术迎来了最好的发展时机

文章出处:【微信号:FPGAer_Club,微信公众号:FPGAer俱乐部】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

击碎摩尔定律!英伟达和AMD将一年一款新品,均提及HBM和先进封装

玻璃基板面临的四大核心技术攻关难点

后摩尔定律时代,提升集成芯片系统化能力的有效途径有哪些?

Achronix Speedcore eFPGA的特性和功能

奇异摩尔专用DSA加速解决方案重塑人工智能与高性能计算

Primemas选择Achronix eFPGA技术用于Chiplet平台

高算力AI芯片主张“超越摩尔”,Chiplet与先进封装技术迎百家争鸣时代

“自我实现的预言”摩尔定律,如何继续引领创新

摩尔定律的终结:芯片产业的下一个胜者法则是什么?

摩尔定律放缓的节奏给eFPGA带来了发展机遇

摩尔定律放缓的节奏给eFPGA带来了发展机遇

评论