上篇文章我们讲了时钟信号的几个重要参数,今天我们简单讲一下在设计中最常用到的几种时钟信号产生的方法,由于篇幅限制,我们不对具体的原理进行讲述,有兴趣的朋友可以在网上搜索相应的文章进行深入了解,另外对于简单的555、8038等振荡电路,以及复杂的通信中用到的时钟产生电路也不涉及。

石英晶体和石英晶振

毫无疑问,这是每个硬件工程师接触的最频繁的两种器件,几乎每个工程师的器件柜里都应该有的器件,只要你用处理器,无论是8位的8051还是32位的ARM器件,总有至少两个两个管脚等着你放一颗晶体(下图左侧的器件)和俩几十pF的电容,这样MCU的心脏才能跳动起来,也才能够在时钟脉冲(像人身体的脉搏)的驱动下去执行一条条的指令。

石英晶体(Crystal)和晶振(crystal oscillator)

大家要注意的是左侧的叫晶体(Crystal,也有人叫无源晶振,只有2个对称的管脚),里面的核心是一片薄薄的、具有压电效应的石英(比较便宜,且机械结构比较可靠)片,该石英片的厚度决定了振荡器的振荡频率,因此其厚度不可能无限制的薄,也就意味着石英晶体的振荡频率不可能无限制的高,一般在市场上很难买到30MHz以上的晶体,虽然有的公司能够提供到66MHz的晶体,但价格会非常的贵,因为要切割出如此高频率对应的薄石英片的成本会更高(良率比较低)。

但,你却很容易买到右侧的80MHz、100MHz的晶振(Crystal Oscillator,有人叫有源晶振,有4个管脚 - 电源、地、输出、输出使能或空),为何?因为有源晶振本质上是个内部封装了石英晶体、振荡电路、输出电平调节电路的模块,其振荡电路可以振荡在晶体的3x、5x乃至7x的谐波上,也被称为“泛音振荡器”,并能够满足你需要的电平。

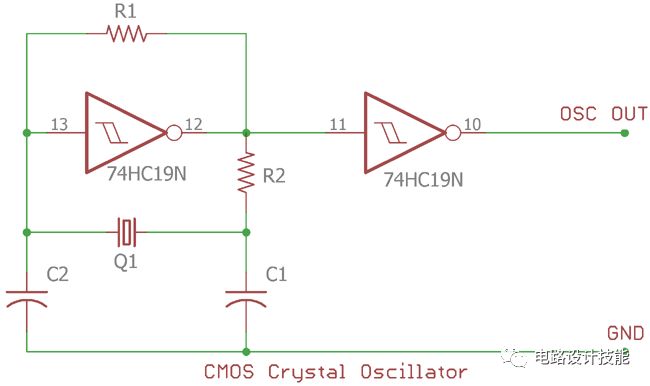

用晶体+反相器构成的振荡器电路

石英晶体/晶振相比LC、RC、RLC振荡电路具有非常高的Q值,也就是非常高的精度和频率稳定度。我们小时候家里墙上挂的表(以及带的手表)都是机械的,校准后跑几天能差出好几分钟去,后来有了“石英钟(以及石英表)”,跑一年依然误差在一分钟以内,当时觉得非常神奇。原因就是石英的精准度和稳定度非常之高,当然有的石英表买回来就不准,你可以直接扔掉,原因就是它用的晶振振荡电路的时钟频点偏移了,也就永远调整不回来了。

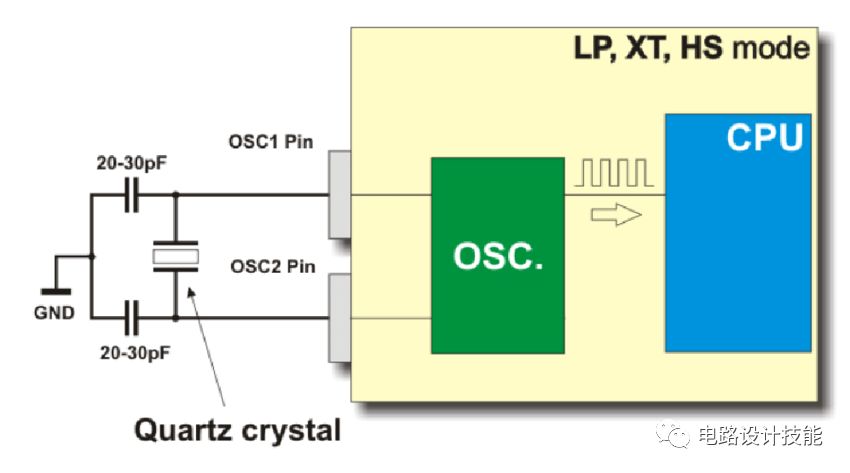

下图是最常见的MCU的时钟电路。

MCU、FPGA等数字器件振荡电路的典型工作方式

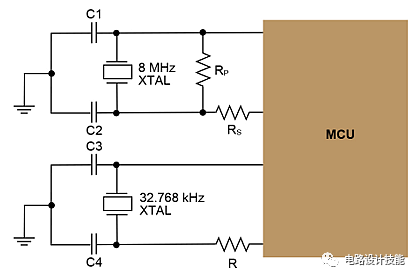

有的低功耗MCU器件除了正常工作需要的比较高的时钟外,还有一个很低频率的时钟电路(比如下图中用于实时时钟的32.768KHz),能够在系统休眠(主时钟驱动的电路不工作)的情况下保持局部电路的工作。

具有两个晶振时钟的MCU

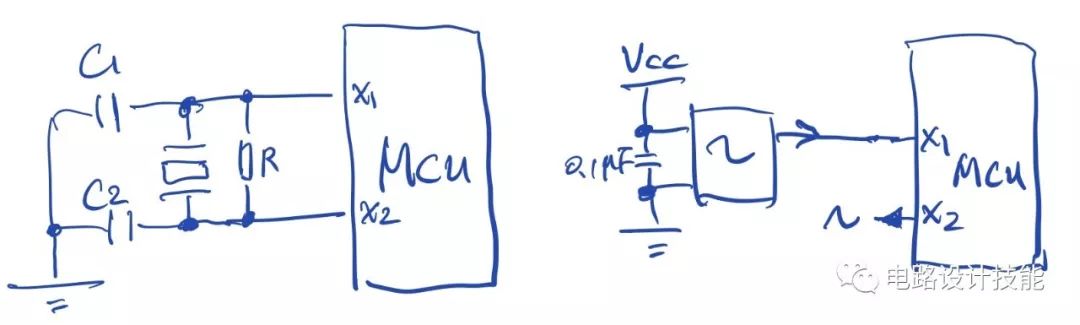

如果你电路板上有多个需要时钟的数字器件,有时候可以共享一个时钟源,例如MCU器件可以外部通过直接连接的晶体产生内部时钟,也可以将外部已经工作的时钟信号输入到X1(有的器件叫OSC1),在X2管脚上可以测量到反相的时钟输出,这个信号也可以用于其它器件的时钟源,前提是该时钟的频率满足其它器件的要求。

MCU可以使用无源的晶体也可以使用有源的晶振或其它外部时钟源

就如同电阻、电容一样,晶体、晶振也有各种不同但相对常用的一些频率的器件,比如用于实时时钟(通过分频)的32.768KHz、异步串行通信的11.0592MHz、用于USB的12MHz等。虽然很多系统对时钟的精确频率并没有要求,但选用的时候还是要根据系统中要支持的功能,尤其是一些外设来选择一个最合适的频率点,当然也要能够以正常的价格购买得到。

非精准时钟需求的RC振荡器

晶体、晶振具有高Q值和高输出能力,适用于抖动必须极低的应用,可以实现100飞秒的相位噪声(在传统的12kHz至20MHz带宽内测量),但其缺点就是它像电感一样不能够集成在器件的内部,在今天强调系统成本要低、PCB板上空间趋于越来越紧凑的情况下,器件内部集成非晶振的振荡电路在某些应用场景下就非常有意义。比如有的MCU、数字通信器件通常内置了RC相移振荡器用于非精密要求的时钟产生,生成的时钟频率取决于内部集成的R、C值,这种振荡器具有大约1%的精度而且抖动比较高,适用于转换时序不重要的应用,例如为MCU计时和驱动简单的七段LCD,也可以用于实现高达几Mbps、时序容差达到几百ns的UART通信、低速/全速的USB数据通信等。

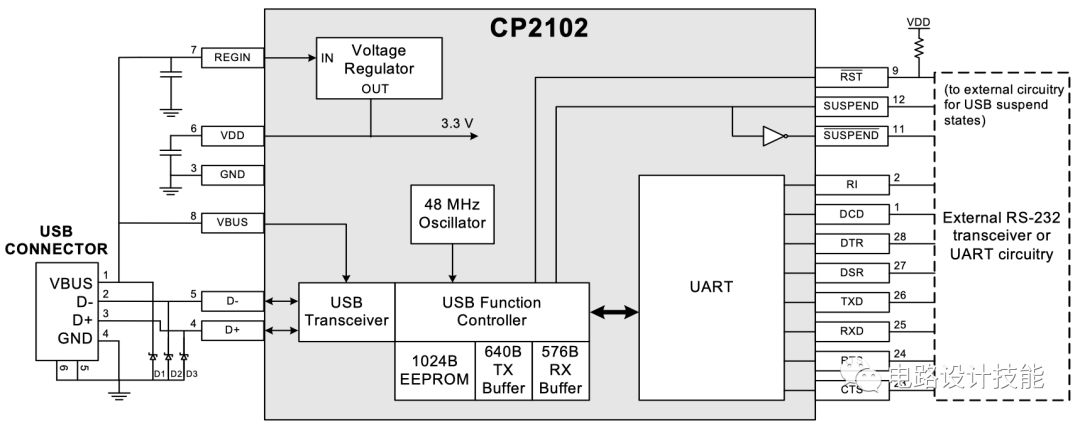

CP2102内部有48MHz振荡器,不需要外接时钟产生电路

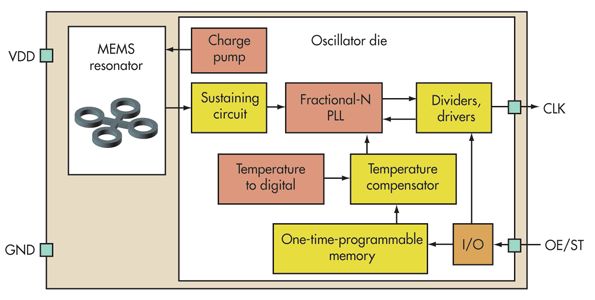

近几年还有一种替代石英晶体振荡器的器件 - MEMS(微机电)振荡器被广泛使用,它可以在扩展温度下工作,频率非常稳定,具有极高的可靠性,抗冲击和振动,体积也可以做的非常小,接近1平方毫米。由于其结构的不同,MEMS时钟可以在出厂的时候通过编程生成不同频率的器件,相对于晶振要灵活多了。MEMS振荡器具有高Q值,输出较低至500飞秒的相位噪声,它被广泛用于网络设备中。

MEMS振荡器内部构成

SiTime就是一家以生产MEMS时钟器件为主的高科技公司

用PLL+晶振产生更高频率的时钟信号

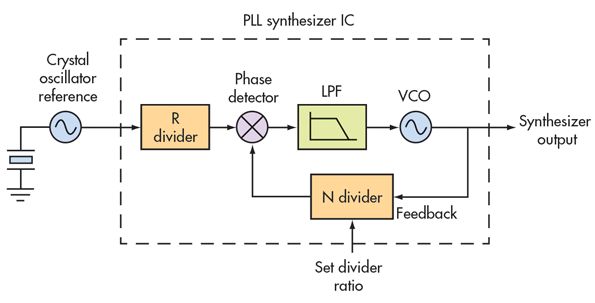

石英晶体、晶振能够产生的频率比较低(能到100MHz已经不错了),而且频率很固定,如果在系统中需要非常高的频率(今天我们通信中常用的5.8GHz、CPU常用的1.8GHz是如何实现的?)而且在满足信号精度、稳定性的情况下,频率还可以非常方便地调节,如何才能实现?-- 锁相环PLL。

下图是PLL的方框图,细节不讲,有兴趣的自己去补,在这里只是告诉大家,PLL是基于一个外部的晶振时钟,能够先对晶振进行整数倍R分频处理,作为PLL内部的基准时钟,内部的环路可以对这个基准时钟进行N倍的倍频,因此可以得到外接晶振频率F的N/R倍的频率。

锁相环PLL的工作原理框图

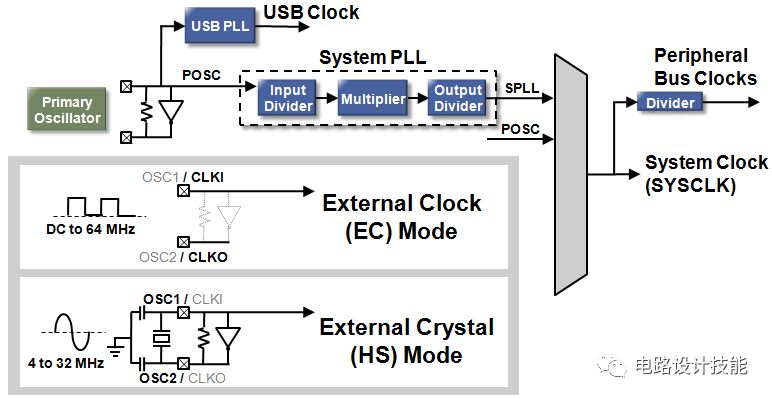

PLL不仅被广泛用在通信系统中产生方便调节的不同频点的高频率本振信号(LO),还被广泛用在处理器、FPGA、通信器件中用于生成器件内部的高速时钟。

DDS生成任意频率的时钟信号

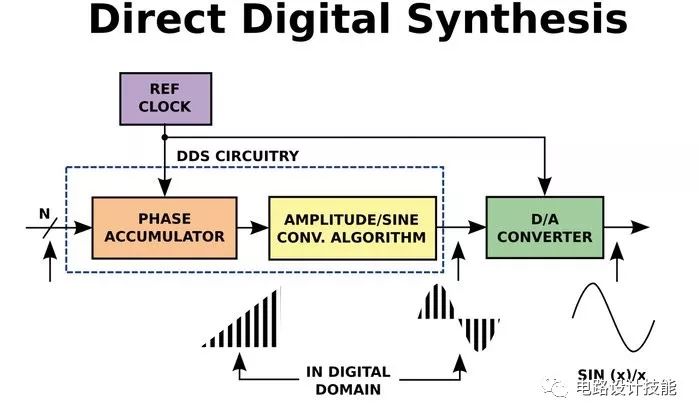

如果你不需要非常高的频率,要求频率灵活可调,而且调节精度需要非常的高(比如数字收音机中),如何实现实现?有一种方法叫DDS(直接数字合成)可以来帮到你,它的优点就是只要你有一个主时钟,就可以产生任意频率点的时钟信号,而且频率点可以非常高精度地调节。

DDS工作原理框图

ADI公司(www.analog.com)有一系列的DDS芯片满足不同频率段的要求,如经典的AD9850(125MHz主时钟)、AD9832(25MHz主时钟)等等;如果你板子上有FPGA,也可以通过FPGA的逻辑来自己实现。再配合FPGA内部的PLL(小脚丫FPGA用的器件可以工作在内部400MHz主时钟)就可以实现更高频任意频率时钟的产生了。(我们春节后会在摩尔吧上线一个专门讲述通过DDS生成任意信号的在线课程,敬请大家关注)

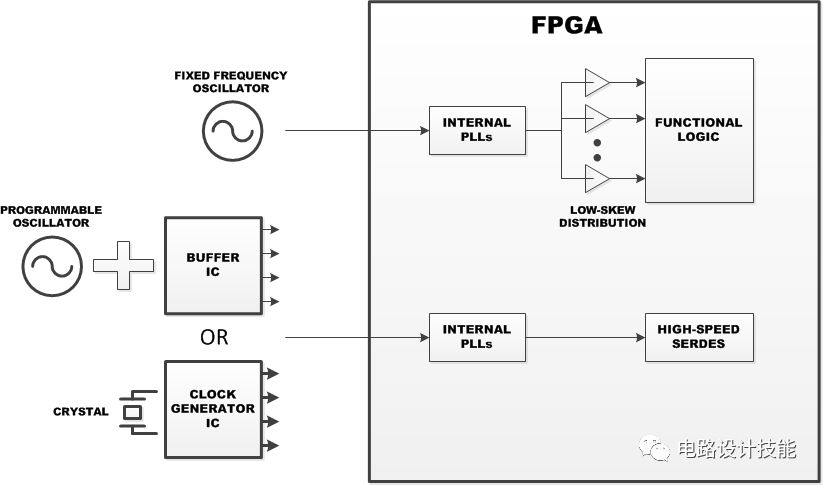

下图是目前的FPGA器件常用的时钟产生方式,外部提供低速的晶振时钟(如果是全局时钟,需要连接到指定的几根管脚上),内部的PLL就可以通过配置参数得到不同频率的高频率时钟。

FPGA内部高频率时钟的生成

通过可编程逻辑实现整数倍分频

在可编程逻辑/FPGA中会用到各种频率的时钟,而这些时钟都来自一个祖宗 - 主时钟,如何通过简单的逻辑得到不同频率的时钟信号,并且满足需要的相位关系是FPGA学习者必须要掌握的一项基本技能。在我们小脚丫FPGA的公众号文章中有专门的介绍并附有Verilog的源代码,可以自己去查阅。也可以点击左下角的阅读原文,到小脚丫FPGA的Wiki系统中去查找。

Enjoy!

-

处理器

+关注

关注

68文章

19461浏览量

231424 -

ARM

+关注

关注

134文章

9184浏览量

369747 -

石英晶体

+关注

关注

0文章

173浏览量

38659

原文标题:电子产品的心脏-时钟—— 时钟信号的产生

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

设计中最常用到的几种时钟信号产生的方法

设计中最常用到的几种时钟信号产生的方法

评论