自己动手做一个信号发生器和示波器非常重要,不仅可以深刻理解测量仪器的工作原理、关键技术指标,还可以将书本上学过的模拟电路、数字逻辑乃至嵌入式系统全部串起来,从系统层面对各个部分的功能以及构成有更真切的认识,因此苏老师觉得这两个项目应该是所有电子工程师都要动手做一遍的基础入门项目。

高速ADC是数字示波器的核心部件,今天关于ADC应用的文章就结合我们摩尔吧/硬禾实战营的一个实际项目 - 100Msps的数字示波器的制作来做一个简单的案例分析,数字和处理部分将在将来的文章中具体分析,今天集中在模拟部分:

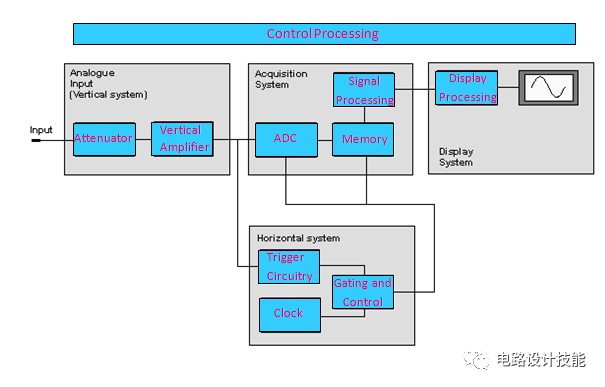

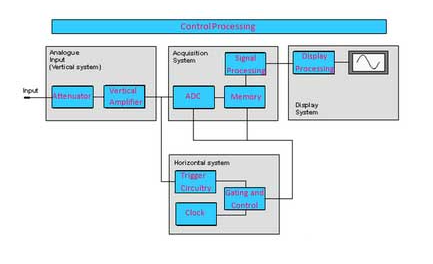

数字示波器的构成框图

我们的项目对模拟部分的主要指标要求如下:

单通道、100Msps采样率

模拟带宽20MHz,输入电压的范围 - -10V ~ +10V

最小分辨电压 10mV

经过高速ADC以后的数据通过FPGA(当时就用Lattice的FPGA)进行处理以后送到后面的Cortex M4控制器,再在LCD显示屏上显示出来,触发、测量电压、频率等参数都在FPGA内实现。

用Lattice FPGA + NXP的M4开发板以及自制的模拟链路/ADC构建的数字示波器

今天我们就以这个项目为例,简单分析一下数字示波器模拟链路部分的设计要点。

首先我们基于给出的指标需求分析一下:

单通道- 需要一颗单路的ADC

100Msps- 需要一颗采样率在100Msps以上的ADC

20MHz的模拟带宽 -意味着最高频率20MHz的模拟信号,如果用100Msps的采样率,每个周期会有5个采样点,留给学员通过FPGA逻辑进行内插的空间

+/-10V的最大输入电压范围和最小10mV的电压分辨率意味着整个模拟链路以及ADC能够处理的信号的动态范围为20Vpp/10mV ~ 2000 ~ 63dB

第一个问题:选用多少位数的ADC?8、10、12、14、16位?ADC的精度的选用要和前面的模拟信号调理电路共同对付63dB的动态范围。理想状态下8位的ADC可以提供48dB的动态范围、10bit ~ 60dB、12bits ~ 72dB,14bits ~ 84dB,但由于存在着量化噪声,导致ADC的有效位数要低于实际使用的位数,也就是12位的ADC,有效的位数小于12(数据手册显示 - AD9628在采集20MHz的模拟信号的时候相当于11.6bits). 从这个分析上看,选用一颗12bits/100Msps的ADC就可以满足系统对动态范围的要求。

但,ADC的精度越高,意味着器件内部的资源大幅增加,器件的成本以及价格也就大幅增加,在同样的转换率的情况下,一颗12位的双通道ADC(AD9628-105)的价格比10位的双通道ADC(AD9608-105)要高出一倍(以其官网上1000+片的价格做参考),见下面的表格。这多花的十几美元是否可以通过10bit ADC + 可变增益运放甚至8bit ADC +可变增益运放来实现呢?

ADI公司的高速ADC,可以通过参数过滤选用最适合自己的器件

这就需要权衡,需要从系统层面来综合考虑,引入可变增益放大器可以提供几十个dB的可调增益范围,带来的挑战就是:

运放器件本身的价钱、多出来的电路板空间的成本

运放电路设计(需要仿真)和调试的难度 - 可调增益、要保证线性范围工作、周边器件的合理选用

最难的可能是运放电路的供电 - 一般都是双轨、低噪声的电压,比如+/-5v或+/-10V,模拟电路的双轨供电可是难煞了很多工程师,做不好性能会达不到要求。

放大电路的增益要可调节,如何调节?总不能用手拧电位计调节吧?需要VGA(电压控制增益)或模拟开关切换。电可调的电路会带来额外的复杂度以及成本。

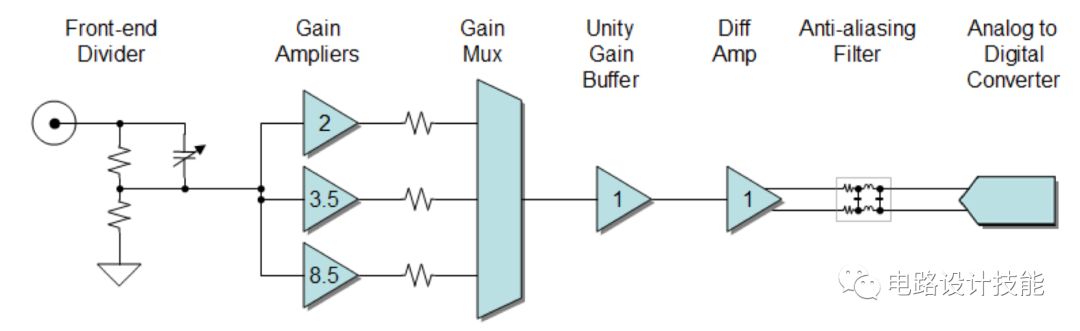

实现数字示波器模拟前端的方式之一,通过模拟开关来实现链路增益的调节

说到这里是不是觉得头大了?是不是觉得自己的知识量不够了?这还仅仅是信号的幅度方面的要求,信号的频率呢,也就是对频带的要求呢?即便20MHz以内的模拟信号,你需要低通滤波器(防混叠),选用的模拟器件要考虑到增益带宽积是否满足要求、瞬间的响应速度是不是够、电压控制增益的范围内线性度如何?

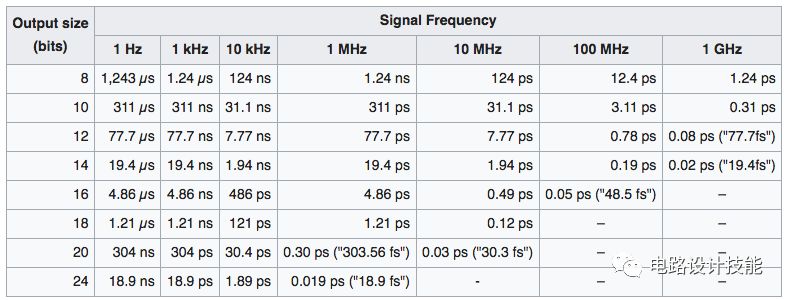

从降低系统复杂度的角度出发,我们希望用一颗高速的ADC,比如14、16bit全部搞定最好,但杀鸡用牛刀显然也是不对的,毕竟要考虑到系统的成本,更重要的是即便从理论分析上14bit的ADC能够满足你的要求,但实际的电路中会由于电源噪声、时钟抖动等使得你使用更高分辨率的ADC没有意义。上篇文章中我们讲过(下面的表格),即便对于10MHz的模拟信号,用14bit的ADC,采样时钟边沿的抖动必须小于2ps,100MHz(10ns周期)的时钟抖动要小于2ps,你自己测一下你自己板子上用FPGA产生的100MHz的时钟的边沿抖动有多大?是否能小于2ps?

针对不同的模拟信号,采用不同位数的ADC对时钟边沿抖动的要求

所以,如果你用14bits的ADC,那必须给你的ADC提供极小边沿抖动的采样时钟信号,意味着你的时钟源(一般PLL产生)要非常好,最好采用差分时钟信号传输、时钟以及ADC的电源去偶要格外注意、PCB的设计要很讲究。所以挑战会比较大。

越是采样频率高的示波器,高分辨率的ADC器件成本会更高,对时钟抖动的要求越高,成本也会大幅增加,比如500Msps的数字示波器,如果你做的产品不能卖到非常高的价格让你有足够的成本空间采用更好的器件,最好采用8bits的ADC。

因此在学员的实际项目制作中我们也尽量让学员选用8bit、10bit的ADC配合前端可调增益的放大器来实现63dB的动态范围,下面是几款当时我们推荐给学员选用的ADC的型号,具体型号的选用还要考虑到供电电压、功耗、数据接口方式、价格等要素。

几款可用于100Msps数字示波器的高速ADC

在我们100Msps的项目中我们选用8位的AD9283作为ADC,63dB-48dB ~ 15dB的动态范围就通过可控增益的运放来实现。

由于输入的信号是+/-10V,而ADC一般的输入电压范围是2Vpp,所以需要对输入的电压信号先进行10:1衰减(-20dB),得到+/-1V的模拟信号,再通过0-20dB的可变增益控制来满足ADC的输入电平要求。

在ADC之前有一个低通滤波器用于对20MHz以上的信号做过滤,主要目的是防止20MHz以上的噪声通过采样混叠在被测信号的采样结果中。关于这部分的理论分析大家可以看一下抗混叠采样相关的技术文章。

以上我们简单分析了一下如何根据被采集信号的幅度范围来选取适当分辨率的ADC + 可变增益调理电路的组合,原则是考虑到电路的性能、可实现性、设计难度、系统成本等各因素后的综合折衷。

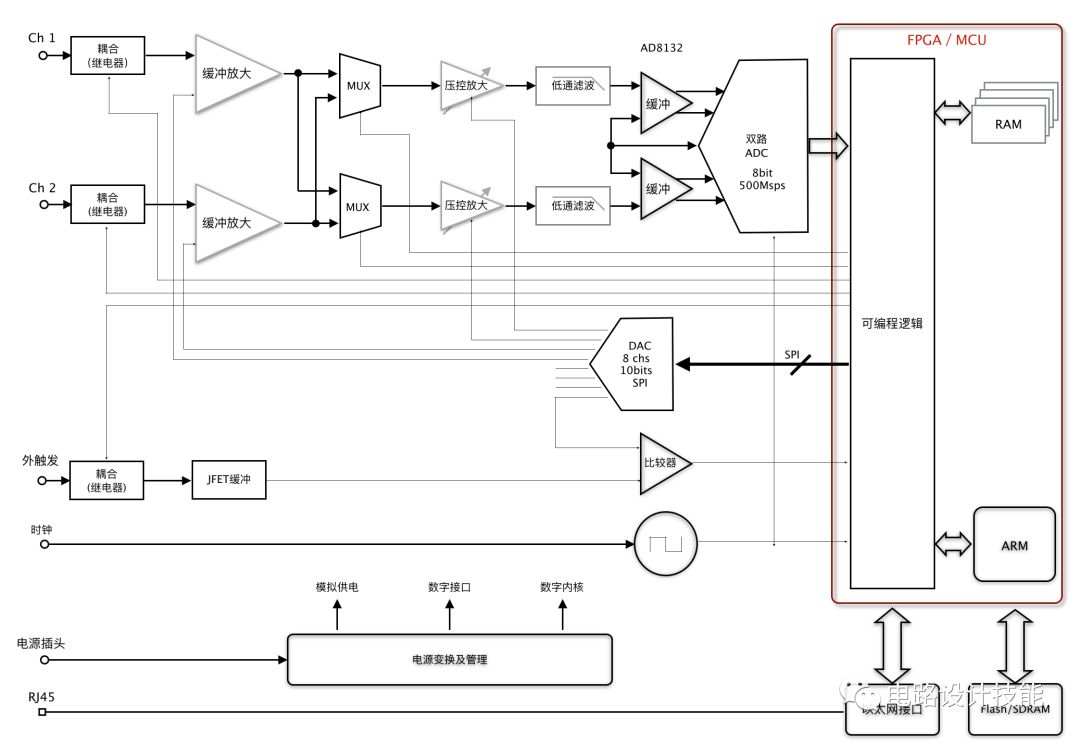

下面的这个图是我们设计的一款产品 - 500Msps的双通道高速数据采集系统的框图,使用的是8位、500Msps的ADC以及ZYNQ FPGA器件,可以通过以太网同上位机PC进行数据传输。压控放大器的增益控制电压是靠低速串行DAC实现。每一级电路的增益、带宽的设定原理同上。

限于篇幅,不能对细节做详细说明,如有对此有兴趣的朋友可以通过留言的方式做进一步的沟通。

-

模拟电路

+关注

关注

125文章

1577浏览量

102987 -

adc

+关注

关注

99文章

6546浏览量

546134 -

数字示波器

+关注

关注

6文章

531浏览量

33751

原文标题:ADC/DAC(3)- 数字示波器中ADC的选用

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

关于ADC应用100Msps的数字示波器的案例分析

ADC芯片的采样率为100MSPS,位宽16位,那么吞吐量是多少?

制做一个数字采样示波器

MAX19506 双通道、8位、100Msps ADC

面向医疗与工业,TI推出8通道100MSPS ADC

数字存储示波器制作参数

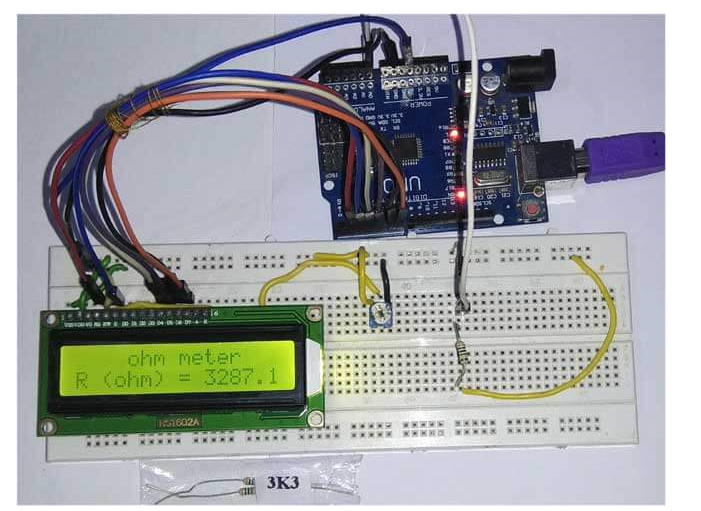

如何使用Arduino来制作一个简单的欧姆表

DS100 Mini数字示波器

ADS5263四通道、16位、100MSPS高SNR ADC数据表

ADS5295低功耗,12位,100MSPS,8通道模数转换器(ADC)数据表

100Msps的数字示波器的制作来做一个简单的案例分析

100Msps的数字示波器的制作来做一个简单的案例分析

评论