摩尔定律是指计算机芯片上的晶体管数量每隔2年左右会翻一番,并在过去数十年中成功验证。不过伴随着生产工艺要求的提升,越来越多的人质疑未来摩尔定律是否依然有效。

麻省理工学院和科罗拉多大学的工程师近日成功研发出新的微加工技术,可用于生产有史以来最小的3D晶体管,尺寸是目前主流商用产品的三分之一。

几年前,芯片行业的标准是14nm生产工艺,是指每个晶体管的宽度。目前在商业领域,iPhone XR、iPhone XS和iPhone XS Max上装备的A12 Bionic芯片就是7nm生产工艺,而且目前已经有生产厂商开始试验5nm生产工艺。

而研究人员开发的一些新晶体管再次将其减半,根据测量创纪录的达到2.5纳米宽。

为了制造它们,该团队在新进开发的微加工工艺热原子层蚀刻(thermal ALE)基础上进行了改进。首先他们将称之为铟镓砷(indium gallium arsenide)的合金半导体材料暴露于氟化氢(hydrogen fluoride)上,用于在基板表面上形成薄薄的金属氟化物层。

接下来该团队添加了一种名为二甲基氯化铝(DMAC)的有机化合物,用于触发配位体交换(ligand exchange)的化学反应。DMAC中名为“ligands”的离子和金属氟化物层中的原子结合,因此当DMAC被清除时,它将单个原子从金属表面上剥离。每次刻蚀仅0.2纳米,当重复数百次过程时,蚀刻精度可以达到令人惊叹的地步。

该研究的第一作者卢文杰说:“这就有点像是一层层的剥洋葱。在每个循环中,我们只能蚀刻掉2%的纳米材料。这使我们具有超高的精度和对过程的精确控制。”研究人员使用该技术制造了FinFET(鳍片场效应晶体管),通常情况下精度为5nm,而最高精度可以达到2.5纳米。

-

芯片

+关注

关注

458文章

51476浏览量

429154 -

计算机

+关注

关注

19文章

7571浏览量

88959 -

晶体管

+关注

关注

77文章

9823浏览量

139291

原文标题:麻省理工开发微加工技术 可将3D晶体管工艺缩小至2.5nm

文章出处:【微信号:IC-008,微信公众号:半导体那些事儿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高分子微纳米功能复合材料3D打印加工介绍

麻省理工科技评论:2025年AI领域突破性技术

微流控芯片中的CNC加工技术

3D打印技术,推动手板打样从概念到成品的高效转化

晶体管与场效应管的区别 晶体管的封装类型及其特点

麻省理工学院研发全新纳米级3D晶体管,突破性能极限

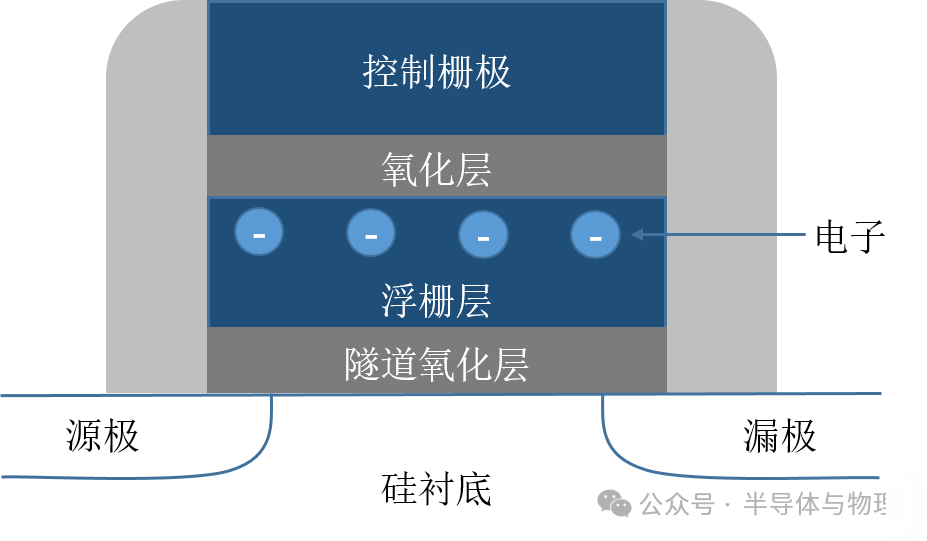

3D-NAND浮栅晶体管的结构解析

麻省理工学院推出新型机器人训练模型

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

PNP晶体管符号和结构 晶体管测试仪电路图

麻省理工开发微加工技术可生产最小的3D晶体管

麻省理工开发微加工技术可生产最小的3D晶体管

评论