前面简单介绍了ADC和DAC的基本结构,今天来看看ADC和DAC使用中要注意的要点:

根据项目需要的性能进行选型

选择适合你项目的器件是第一步,因此你首先要知道都有哪些可供选择,仅仅依赖搜索引擎是不够的,你必须对主要的器件结构、参数、厂商有全面的了解,一个简单的办法就是到www.mouser.cn或www.digikey.com.cn按照分类进行查看,如下图,可以看到Mouser官网上的主要ADC、DAC的类别、供应商以及按照关键参数进行过滤得到的主要的器件型号。通过折腾这个选型表,你可以快速了解到ADC、DAC的大致情况。

半导体行业做ADC、DAC比较强的几家公司的网站要经常去溜达一下,看看他们都有啥,有什么新的器件出现等等。幸运的是随着不断的收购、整合,现在已经没剩下几家了,但你至少应该知道ADI、TI、美信(Maxim Integrated)、ST、Microchip等。

选型的时候需要考虑的几个要点:

模拟带宽和采样率(ADC)或转换率(DAC),时钟的类型 - 单端、差分?

分辨率,也就是用多少位的转换器件。前面我专门讲述了根据系统的要求以及信噪比、失真等对ADC位数和前端模拟链路的综合平衡设计,DAC的位数选择也是一样的原则,不是位数越高性能就越好,到了一定的程度就受限于板子上的噪声和器件的失真了

数据接口方式 - 高速转换器才用并行接口还是串行接口?一般低速的转换器基本都采用SPI或I2C的串行接口方式,高速的器件采用并行接口以及高速串行接口

供电 - 5V?3.3V?1.8V?等,要根据自己系统的供电情况选用合适供电电压的器件

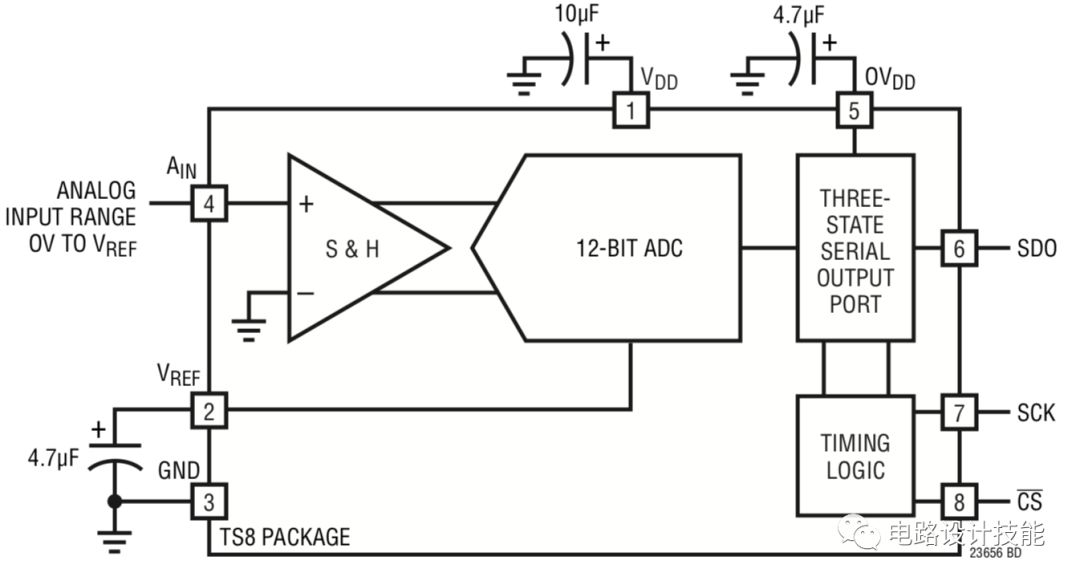

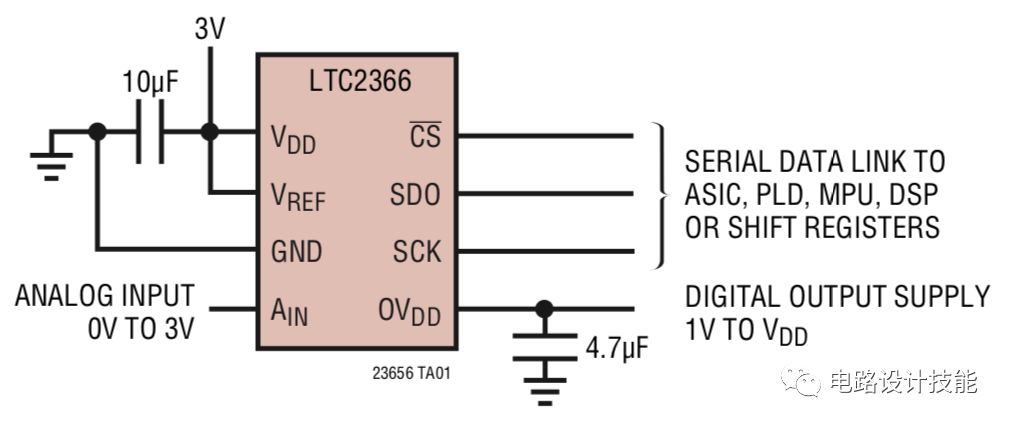

一旦选定了器件就进入了设计部分,我们以一颗串行的ADC(LTC2366)和一颗高速并行的DAC(AD9760)来简单看一下设计中要注意的一些事宜:

先通过框图阅读一下器件:

串行ADC - LTC2366:3Msps、12位取样ADC

单端模拟信号输入 - 输入电压范围为0-Vref(参考电压)

在简单的使用场景,参考电压管脚直接连接在器件的供电电压管脚上,当然也可以外接参考电压源 - 增加成本,但可以带来灵活性

SPI串行数据接口,要注意的是SPI的时钟频率和器件的转换率是两个概念,器件能够以3Msps的速率转换,SPI要把这3Msps、12bit的数据传输出来,至少要48MHz的时钟频率

供电电压范围比较宽,设计的从2.35V到3.6V之间都可以正常工作,也就是我们常用的2.5V、3V和3.3V供电系统都可以使用

关键的管脚上都要有去偶电容,由于模拟信号的频率比较低,使用的电容一般为4.7uF - 10uF的钽电容(注意是有极性的)

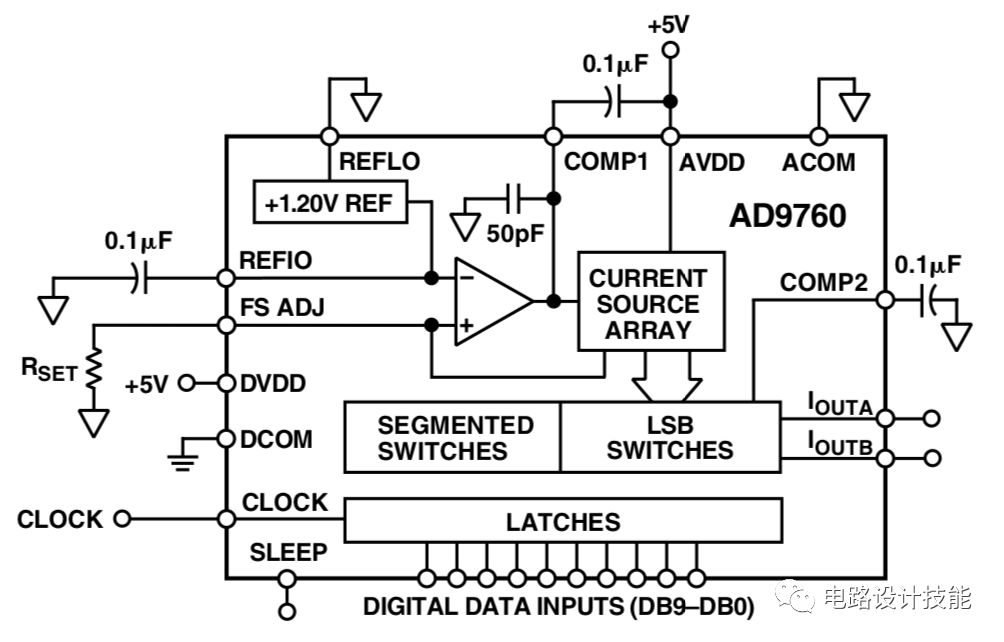

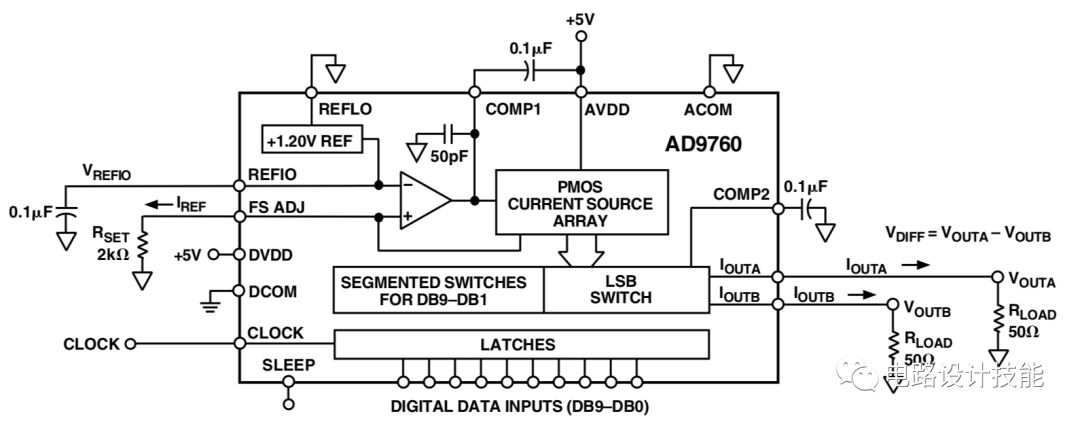

并行DAC - AD9760:

10位并行数据接口、时钟为单端输入

模拟信号为差分输出,在输出端需要差分转单端模拟电路

+5V电压供电 - 数字电源DVDD、模拟电源AVDD,数字地DCOM、模拟地ACOM

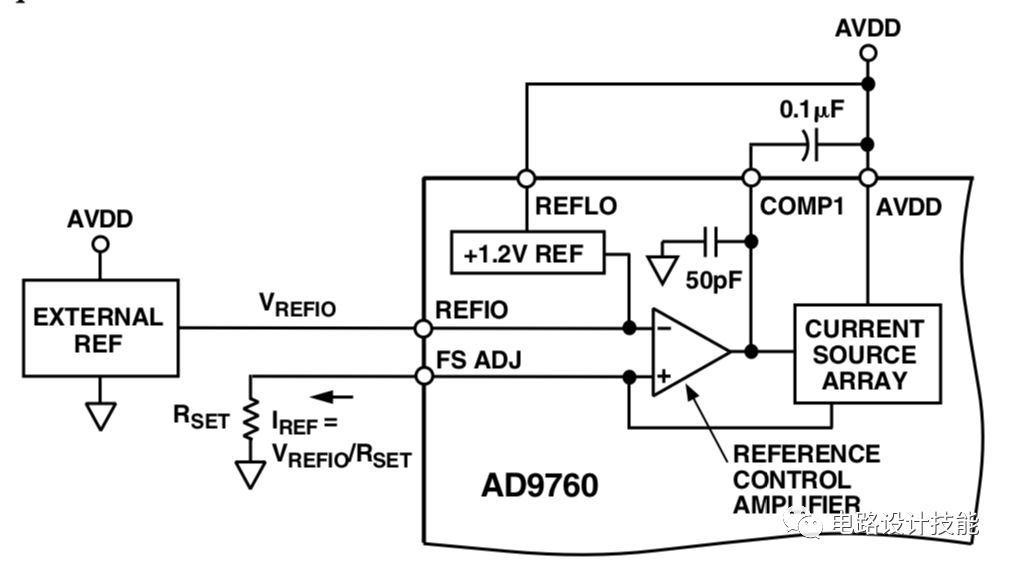

内部1.2V参考电压并通过外界的Rset来设定比较电流,可以通过改变Rset调节模拟输出的电流大小

几个重要的管脚接有0.1uF去偶电容,上面的低速串行ADC的去偶电容选用比较大的值,在这个高速的DAC电路里则选用0.1uF的陶瓷电容,最好是0603或更小的封装

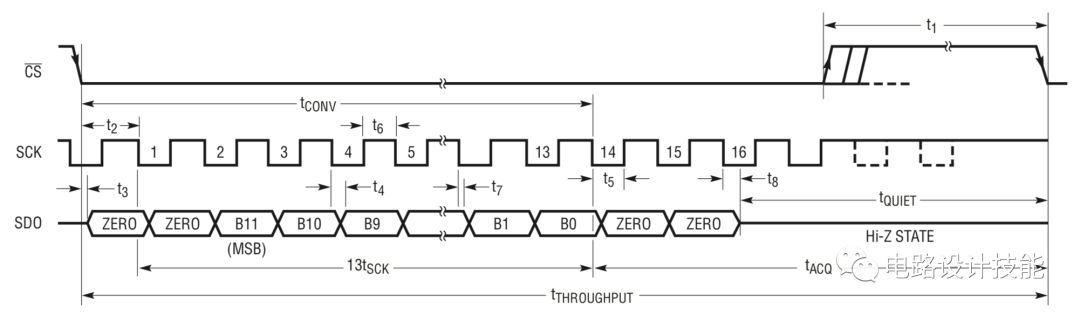

数据接口的时序以及时钟的选用:

前面我们讲过低速串行的器件一般采用I2C或SPI,在LTC2366中采用的是SPI接口,在数据手册中一定要查看其时序图,了解其SPI的工作模式 - 4种模式种的哪一种?从这个时序图可以看出传输一次取样的数据至少需要16个SPI的时钟周期,也就是如果你的ADC转换率为3Msps,SPI的时钟周期至少要在48MHz以上,要保留一定的保护时间,最好选择在50MHz以上,如果SPI的时钟受限,不能工作到较高的速率,比如最高只能到30MHz,那么ADC的采样率也就要相应降低,以确保转换完的数据都能够传递出来。

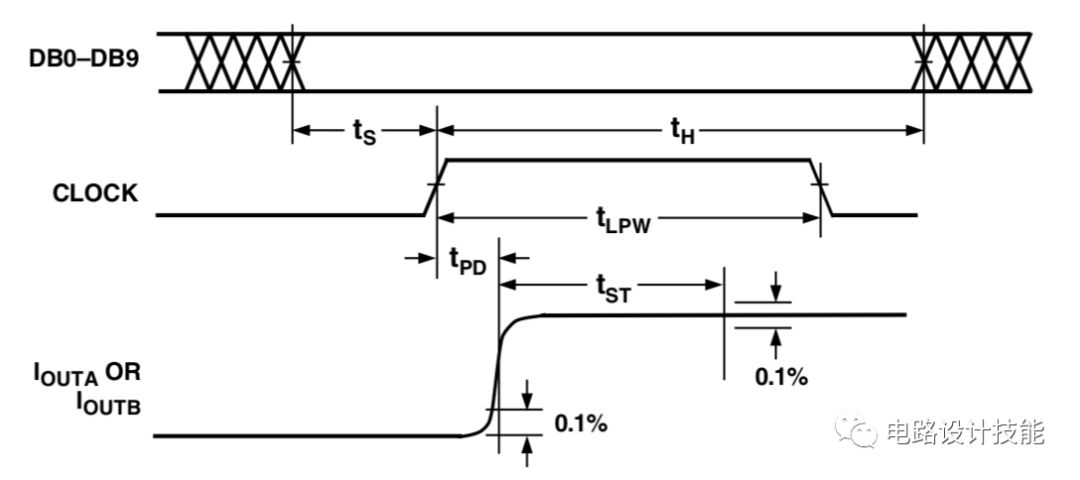

AD9760的时序图如下,可以看出数据的转换是由时钟的上升沿来驱动的,因此在连接AD9760的前方逻辑电路中一定要注意时钟上升沿的跳变要在10根数据稳定了以后才行,如果时钟的上升沿与数据的改变同时发生,DAC器件就会疯掉,出来的数据全部乱掉。ts是个很重要的指标,如果你前面的逻辑输出信号经过PCB上较长的走线到达DAC导致有的数据线和时钟之间的ts不能满足器件数据手册的要求,转换就会出现错误。因此并行传输的DAC在布线的时候数据、时钟线一定要满足时序的要求。

参考电压的使用

无论ADC还是DAC都是通过跟一个基准(电压或电流)进行比较而得到相应的结果的,如果基准发生了偏差,那结果自然也就是错误的,因此在电路中要确保你基准电压或电流的准确性、稳定性,转换的结果也要根据具体的基准值来进行标定。

如下图,LTC2366的Vref同3V的电源电压连接在一起,意味着能够转换的模拟电压满量程为3V(最小采样精度为3V/4096 ~ 0.73mV),因此可以通过改变Vref的值来改变被测模拟信号的精度,比如选用1.5V做Vref测量信号的精度将提高一倍(0.36mV),如果3V的供电电压上有1%的纹波,意味着ADC的参考电压也有这1%的波动,12位的ADC实际上还达到7位的准确度。要能够对0.73mV的电压都能分辨,要求3V上的纹波一定也要低于0.73mV。

AD9760的参考电压可以外接,也可以直接使用内部的1.2V的参考电压,DAC转换的时候是以Vref/Rset得到的电流为基准,因此在同样的数字值的情况下,通过调节Vref或Rset就可以改变转换后的模拟量。很多DDS任意信号发生器都通过调节这两个值来对输出电平进行程控调节,有些DAC器件还可以通过SPI接口配置内部的控制寄存器从而改变参考电流的大小,进而改变输出模拟信号的大小。

要注意的是参考电压管脚一定要加去偶电容电容,LTC2366加10uF的钽电容滤除比较低频率的电源噪声,AD9760则由0.1uF的陶瓷电容实现干扰噪声的高频旁路。

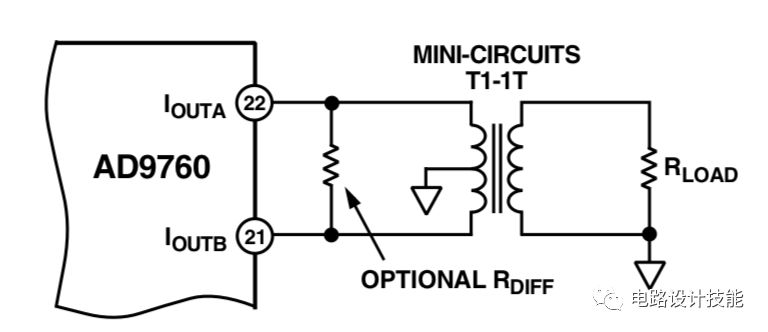

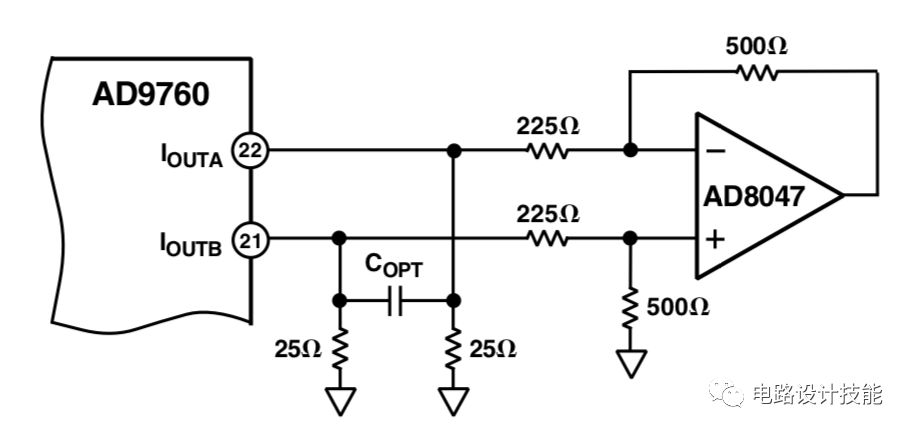

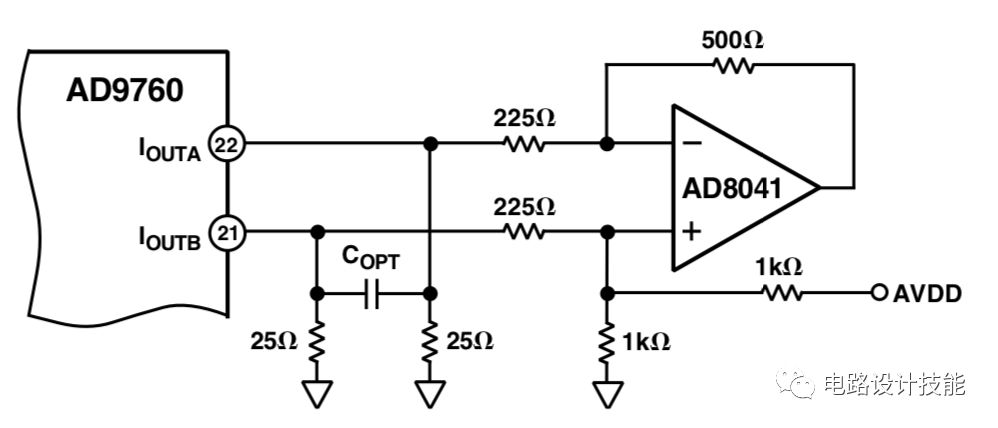

高速DAC的模拟差分输出:

就像其它高速DAC一样,AD9760转换后的模拟信号采用差分电流(IoutA、IoutB)输出的方式,因此在DAC之后需要由差分转换为单端的电路,有以下的方式可供选择:

通过1:1射频变压器实现,要注意的是一定要保证变压器的带宽满足输出模拟信号带宽的要求,变压器的有点是“无源”也就是不需要供电电压,结构非常简单,缺点就是体积比较大,尤其是高度,在有些场合使用起来比较突兀。

通过运算放大器 - 要注意运算放大器的模拟带宽、摆率能满足输出信号带宽的要求,运放的好处是体积比较小,缺点是必须提供非常低纹波的供电电压,尤其是双轨的电压,为此还要设计线性稳压的双路供电电路,电路变得复杂起来。

如果你实在不想在板子上折腾出一个负电压(比如-5V或-3V),只想使用板子上的单路正电压,可以使用下面的连接方式。

布局布线中的考虑

ADC和DAC都是连接模拟和数字的桥梁,注定了它们都是模数混合的器件,它们都分模拟部分和数字部分。

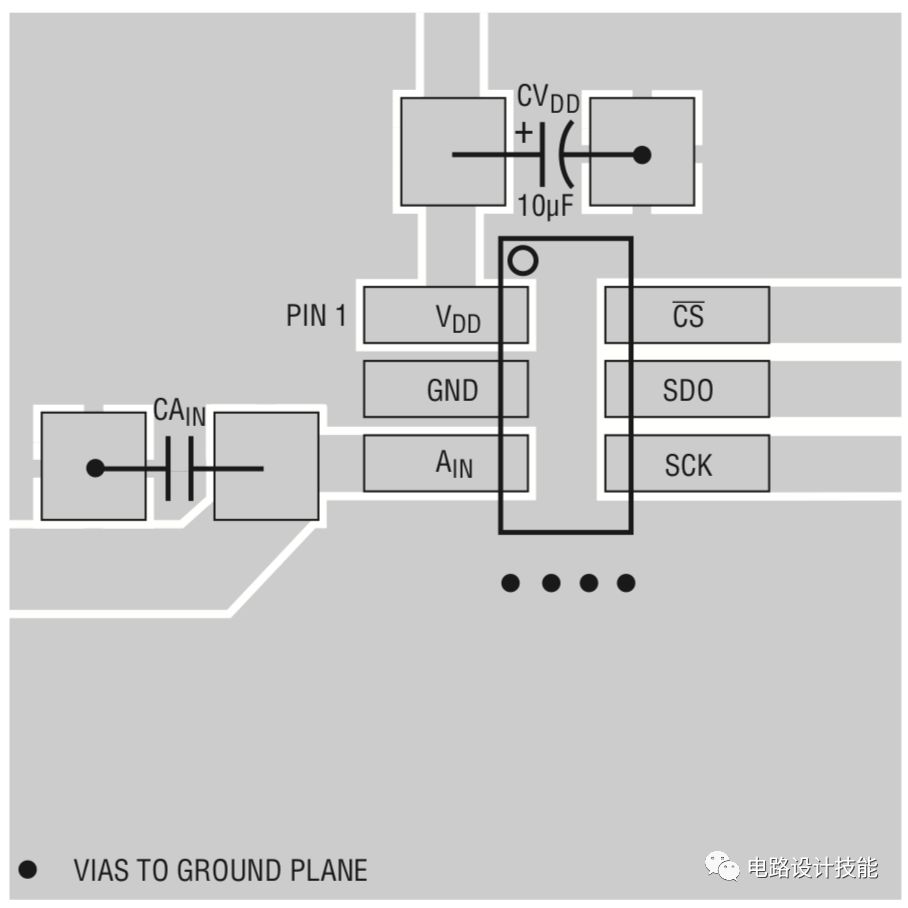

细心的工程师可能已经发现 - LTC2366的供电电压和地只有一个,也就是说没有区分模拟和数字,why?一个原因是这种器件定位的就是“小”,管脚尽可能“少”,只要不影响系统的性能,将模拟和数字合并在一起也没有问题。毕竟低速的ADC或DAC内部的转换逻辑速率都很低,由此产生的开关噪声也相对低很多,只要注意在电源上做比较好的去偶,也能够保证转换的性能。当然在布局布线的时候也是要尽可能注意去偶电容的摆放位置以及地平面的分割,参见下面的LTC2366的参考Layout图。

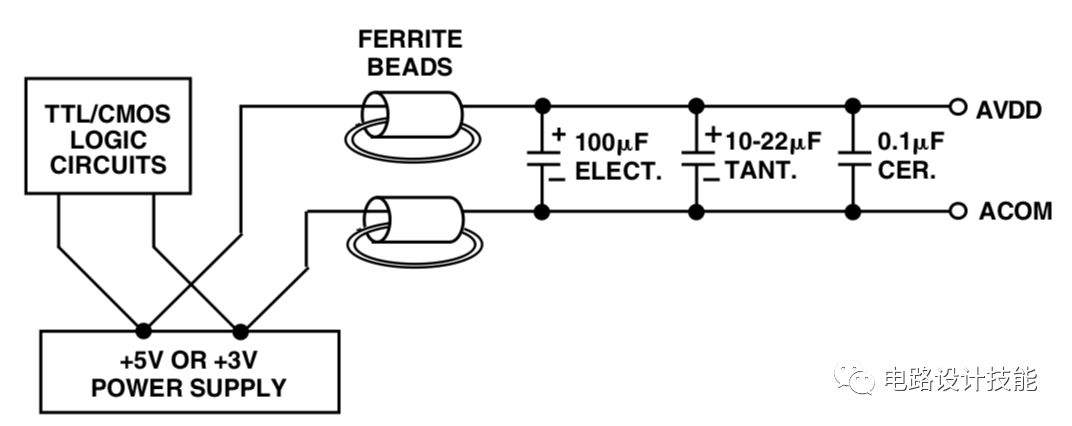

对于AD9760由于数据接口速率以及转换速率非常高,达到了100M,因此模拟电源、地和数字电源、地都是分隔开的,中间用磁珠进行了隔离,我们前面的文章中已经专门介绍过磁珠的应用。注意在模拟电源部分使用了3个容值不同的去偶电容

100uF的电解电容用于极低频率的噪声抑制

10~22uF的钽电容用于较低频率的开关噪声抑制,一般由板子上的开关电源噪声导致

0.1uF的陶瓷电容用于较高频率的噪声抑制,比如其它数字开关电路导致的噪声等

很多MCU内部都集成了ADC和DAC,使用起来更方便,但要注意的是虽然这些器件标称的转换率比较高,但由于MCU工作于多任务的情况下没有可能实时处理转换完的数据,因此需要内部有一定的存储,如果没有存储或者可供转换数据的存储RAM空间很小,实际的转换频率会大打折扣,比如ESP32这个器件其标称的ADC转换率和实际使用中能够真正达到的转换率相差好几个数量级,原因就是处理器的主营业务是做其它的调度,根本没有时间来理你,偶尔来让你查看一下外部的模拟电压值而已,即便你能跑的很快,但多数时间是让你在那里站着。

因此多数情况下就需要选用独立的ADC、DAC,并通过FPGA配以适当容量的RAM来进行存储,在MCU的眼里ADC、DAC永远都是偶尔处理一下的外设,给你一次被临幸的机会,你就要让它一次吞吐个够。

-

转换器

+关注

关注

27文章

8681浏览量

147066 -

adc

+关注

关注

98文章

6489浏览量

544418

原文标题:ADC/DAC(4)- 设计中须注意的要点

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

STM32cubeMX配置外接DAC,具体需要注意些什么呢?

双绞线布线要注意哪些要点

请问ADC或DAC和DSP相连接时要注意什么?

pcb设计中需要注意哪些问题?

经验总结:5个FPC设计中需要注意的事项

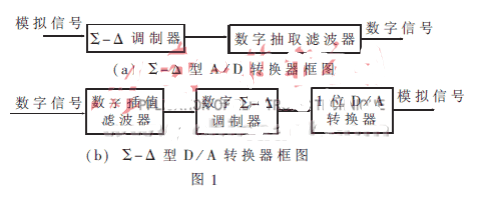

Σ-Δ型ADC和DAC的特点和使用注意事项

使用威格士叶片泵时需要注意什么

AVR单片机ADC采样编程需要注意的问题

ADC和DAC使用中要注意的要点

ADC和DAC使用中要注意的要点

评论