PCB布线方法在不断进步,灵活的布线技术可以缩短导线长度,释放更多的PCB空间。传统PCB布线受到导线坐标固定和缺少任意角度导线的限制。去除这些限制可以显著改善布线的质量。

背景

我们首先来介绍一些术语。我们将任意角度布线定义为使用任意角度的线段和弧度进行的导线布线。它是一种导线布线,但不限于只能使用90度和45度角度的线段。拓扑式布线是不粘附栅格和坐标的导线布线,不使用像基于形状的布线器那样的规则或不规则栅格。让我们把术语灵活布线定义为没有形状固定的导线布线,能够通过实时导线形状再计算实现下文的转变可能性。只有来自障碍物的圆弧和它们的公切线被用来形成走线形状。(障碍物包括引脚、铜箔、禁布区、过孔和其它物体)

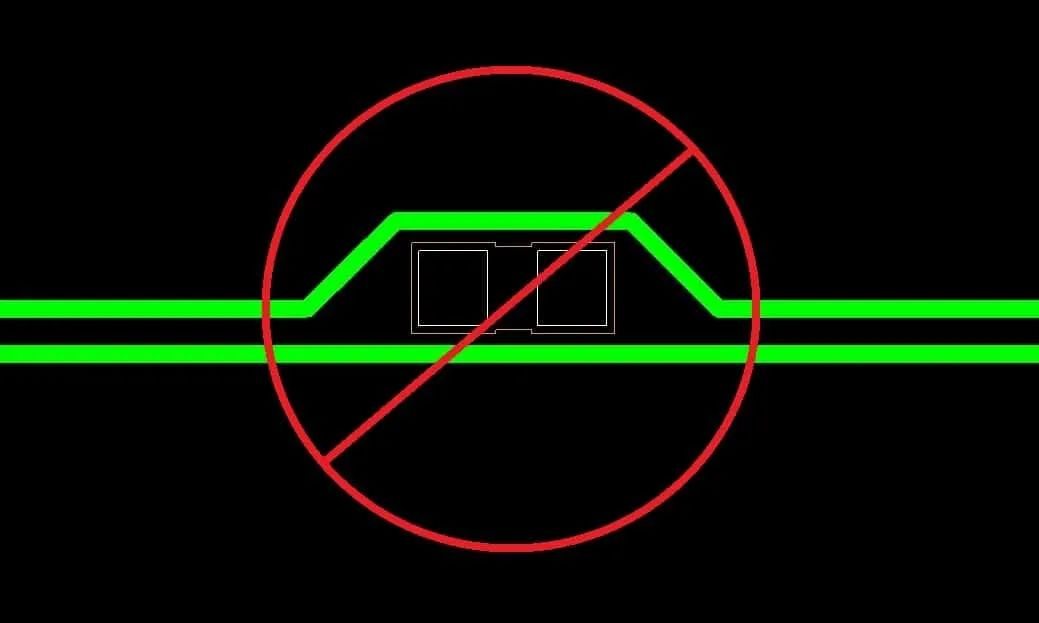

图1显示了两种PCB模型的部分电路。其中的绿色导线和红线导线分别走在pcb模型的不同层上。蓝色圆圈是过孔。红色元件被高亮显示。另外有一些红色的圆形引脚。图1a是只使用线段和线段间夹角为90度的模型。图1b是使用弧和任意角度的PCB模型。也许任意角度布线看起来很奇怪,但它确实有许多优势。它的这种布线方式与半个世纪前工程师的手工布线方式非常类似。

图1:两种PCB模型的部分电路

顶图:传统设计版本

底图:同样的设计但采用了任意角度的布线

图2显示了一家名为Digibarn的美国公司在1972年开发的完全手工布线的真实PCB。这是一块基于Intel 8008的计算机内的PCB板。图2所示的任意角度布线事实上与图1b很相似。为何他们会使用任意角度的布线呢?因为这种布线方式有许多优势。

图2

(资源来源:DigiBarn计算机博物馆)

任意角度布线的优势

任意角度布线有许多优势。首先,不使用线段间的角度可以节省PCB空间(多边形所占的空间总是要大于内切圆)。

传统的自动布线器在紧邻元件之间只能布3根线(见图3中的左边和中间)。而任意角度布线时的空间足以在相同路径上布4根线而不违反设计规则检查(DRC),见图3右边。

图3

假设我们有一个正方式芯片,想把芯片引脚连接到另外两列引脚(见图4)。只使用90度夹角要占很大的面积(见图4顶部)。

图4

使用任意角度布线可以缩短芯片和其它引脚之间的距离(图4中间),同时减小占用面积。在本例中,面积从30平方厘米缩小到了23平方厘米。

任意角度旋转芯片还可以提供更好的效果。在本例中,面积从23平方厘米缩小到了10平方厘米(图4底部)。图5显示了一块真实的PCB。带旋转芯片功能的任意角度布线是这种电路板的唯一布线方法。这不仅是一个理论,也是得到实际应用的解决方案(有时是唯一可行的解决方案)。

图5

图6显示了一个简单PCB的例子。拓扑布线器结果如图6a所示,而基于最佳形状的自动布线器结果如图6b所示。图6c是实际pcb的照片。基于最佳形状的自动布线器无法完成这种电路板的布线,因为元件被旋转成任意角度放置。你需要更多的面积,如果不旋转元件,设备必须做得更大。

图6

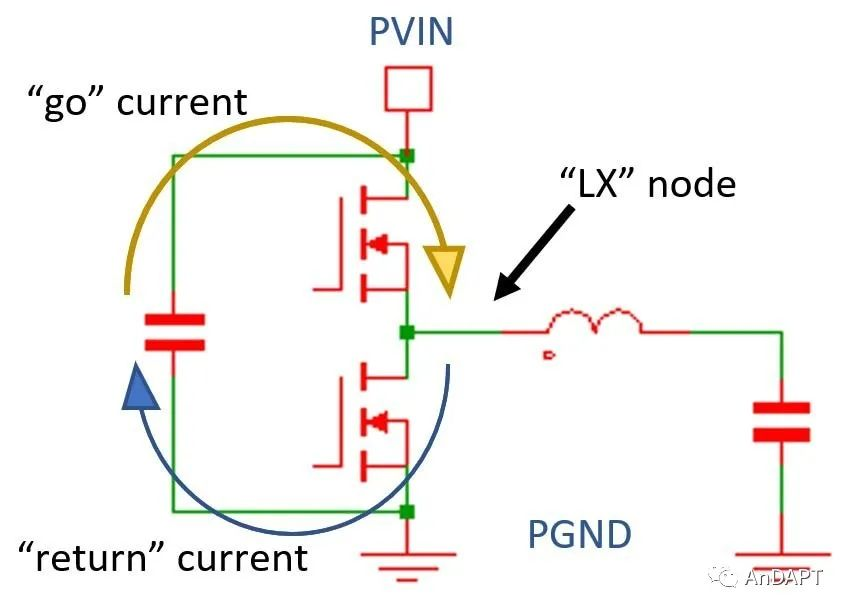

电磁干扰(EMI)

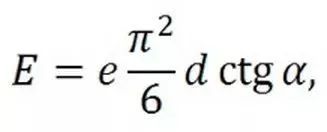

如果没有并行导线段,版图性能将得到很大的提升,因为并行导线段经常是串扰的来源。随着并行导线长度的增长,串扰等级将呈线性增加。当并行导线之间的间距增加时,串扰则呈二次方减小。让我们把两条并行的1mm长导线在间距为d时所产生的串扰等级设为e(见图7)。

如果导线段之间有个夹角,那么当这个夹角增加时,串扰等级将下降。这时的串扰不取决于导线长度,仅受限于夹角值:

其中α代表导线段之间的夹角。

图7

下面考虑三种导线布线方式。在图8中的左边(90度布局),由于并行线段而存在最大的导线长度和最大的电磁干扰值。在图8的中间(45度布局),导线长度和电磁干扰值都减小了。在图8的右边(任意角度),导线长度最短,也没有并行的导线段,因此干扰值可以忽略不计。

图8:三种导线布线方式

因此任意角度布线有助于减小总的导线长度,并显著减少电磁干扰。另外你应该还记得对信号延时的影响吧(导线方向不应该并行,并且不应该垂直于PCB玻璃纤维方向)。

灵活布线的优势

元件的人工和自动移动不会破坏灵活布线中的走线。布线器会自动计算导线的最佳形状(考虑必要的安全间隙)。因此灵活布线可以极大地减少编辑拓扑所需的时间,很好地支持因为要满足限制条件而做的多次重新布线。图9a显示的是一个PCB设计,移动过孔和分支点后的结果如图9b所示。

图9

在自动移动过程中,导线分支点和过孔被调整到最佳位置(如图9c所示)。

在大多数计算机辅助设计(CAD)系统中,布线互连问题被简化为在焊盘、禁布区和已布好的导线形成的迷宫中按顺序寻找成对点之间的路径问题。当找到一条路径时,它就被固定下来,并成为迷宫的一部分。顺序布线的缺点是布线结果可能与布线的顺序有关。

当拓扑质量仍然离完美很远时,在局部很小的区域将发生“被困住”的问题。但不管你重新布线哪根导线,都无法改善布线的质量。这是在使用顺序优化的所有CAD系统中都存在的很严重的问题。

这时应用打弯消除过程就很有用了。导线打弯是指某条网络中的导线想要接入某个物体时必须围着另一条网络上的物体四周行走的现象。重新布线一条导线并不能纠正这种现象。

图10a显示了一个打弯的例子。一条点亮的红色导线围绕另一条网络的一个引脚行走,一条未点亮的红色导线接入这个引脚。图10b显示了自动处理结果。在第2种情况中(另一层上),一条点亮的绿色导线通过改变布线层得到了自动调整(重新布线)(从绿色层到红色层)。

图10

通过自动优化导线形状消除导线打弯(用线段近似弧线只是为了显示没有弧线的任何角度例子)。(顶部)原始设计,(底部)消除打弯后的设计。红色打弯导线被高亮显示,如图10所示。

在Steiner树中,所有连线都必须以线段方式连接到顶点(终点和新增点)。在每个新增顶点的顶部,三个线段必须汇聚在一起,终点的线段不得超过3个。集中到顶点的线段之间的夹角不得小于120度。构造具有这些充足条件性能的Steiner不是很困难,但没有必要是最小的。图11中的灰色Steiner树不是最优的,但黑色Steiner树是最优的。

图11

在实际通信设计中,必须考虑到存在不同种类的障碍物。它们会限制使用两种算法构造最小生成树(图12a)的能力和使用几何方法构造Steiner树(图12b)的能力。图中用灰色表示障碍物。

图12

我们建议从任意一个终结顶点开始。如果有超过一个的相邻终结顶点,你应该选择一个允许你继续使用第二个顶点的那个顶点。这是由角度决定的。

这里的主要机制是一种基于力的算法,它会计算作用在新增顶点上的力,并反复移动它们到一个平衡点(力的幅度和方向取决于邻近分支点的导线)。如果接入某个顶点(终点或新增点)的一对线段之间的角度小于120度(图13a和图13b),可以再增加一个分支点(图13b和图13d),然后使用力学算法优化顶点的位置(图13c和图13d)。最终结果如图13e所示。

图13

值得注意的是,只是按降序排序所有角度然后按这个顺序增加新的顶点是行不通的,结果会更糟。在新加一个节点之后,你应该检查由4个引脚组成的子网的最小性:

1.如果顶点增加到其它新增顶点的邻近位置,要检查最小的四引脚网络(图14a)。

2.如果四引脚网络不是最小的,选择一对“对角”(属于四边形对角线)终点或虚拟的终端节点(虚拟终端节点-导线弯曲)。

3.连接终点(虚拟终点)到最近的新增顶点的线段被连接终点(虚拟终点)到远处的新增顶点的线段所代替(图14b)。

4.使用力学算法优化顶点的位置(图14c)。

图14

这种方法并不保证构建最小的网络,但相比其它方法,它不用牧举就能实现最小的网络长度。它还考虑到了终点连接被禁止的区域,并且终端节点数量可以是任意的。

其它优势

任何角度灵活布线还有其它一些有趣的优势。例如,如果你能借助自动的实时导线形状重新计算功能自动移动许多物体,你可以创建并行的蛇形线。这种布线方式能够更好的利用空间,最大限度地减小反复次数,并且允许灵活地使用容差(见图15)。如果有两条蛇形线相互交织在一起,自动布线器会减小其中一条或同时减小两条的长度,具体取决于规则优先级。

图15

BGA元件的布线

下面考虑BGA元件的布线。在传统的“从外围到中心”方法中,到外围的通道数量将随着每个连续层而逐层减8(由于周长的减小)。例如,具有784个引脚、尺寸为28x28mm的元件需要10层。在图中有些层存在逃逸布线。图16显示了一个BGA的四分之一部分。

图16

与此同时,当采用“从中心到外围”的布线方法时,退出到外围所要求的通道数量不会随着层的改变而改变。这将极大地减少层的数量。对于尺寸为28x28mm的元件来说,7层就足够了。对于尺寸更大的元件,还可以取得双赢。图17显示了BGA的四分之一部分。

图17

图18显示了一个BGA布线的例子。当采用“从中心到外围”的布线方法时,我们可以完成所有网络的布线(图18b)。任意角度的拓扑式自动布线器就可以做到这一点。传统的自动布线器则无法布线这个例子(图18a)。

图18

真实PCB例子

图19显示了一个真实PCB的例子,工程师将信号层数从6层减少到了4层(与规格相比)。另外,工程师只花了半天时间就完成了这块PCB的布线。

图19:一个真实pcb例子。

-

pcb

+关注

关注

4329文章

23194浏览量

400763 -

布线

+关注

关注

9文章

780浏览量

84475

原文标题:实例详解加速和改进PCB布线的方法

文章出处:【微信号:pcbems,微信公众号:PCB商情】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速PCB布线实践指南

加速和改进PCB布线指南

加速和改进PCB布线指南

评论