顾名思义,锁相环(PLL)使用鉴相器比较反馈信号与参考信号, 将两个信号的相位锁定在一起。虽然这种特性有许多用武之地,但是 PLL 如今最常用于频率合成,通常充当上变频器/下变 频器中的本振(LO),或者充当高速 ADC 或 DAC 的时钟。

或许,我们很少注意这些电路中的相位行为。但随着对效率、带宽和性能的需求日益增长,RF 工程师必须推出新技术来提高频谱和功率效率。信号相位的重复性、可预测性和可调性在现代通信和仪器仪表应用中均起到日益重要的作用。

一切都是相对的

关于相位测量,如果不是相对于另一个信号或相对于原始相位则毫无意义。例如,使用矢量网络分析仪(VNA)对放大器之类的两端口网络进行相位测量,就是相对于输入相位ANG(S21)测量输出相位的。单输入相位指相对于入射相位ANG(S11)的反射相位。在 PLL 合成器上,相位测量指的是相对于输入参考相位的测量或 信号间的相位测量。任何相位测量的理想状态就是测得与原始相位相比的精确期望值,但是非线性、非理想性、温差和电路板迹线以及其他制造差异都会使得相位在信号生成中更容易发生改变。对于本文而言,“同相”是指幅度和时序特性相同的信号;确定性相位是指信号之间的相移是已知和可预测的。

示波器测量相位

为了比较两个不同频率的相位,可以使用高速示波器比较输出相位与参考相位,这是一种相对直观的方法。为了直观可见, 输入相位和输出相位通常必须是彼此的整数倍。这在许多时钟电路中相对比较常见。对于整数N分频PLL,输入频率(REFIN)和 输出频率(RFOUT)之间的关系通常是确定和可重复的。只需将示波器探头放在REFIN和RFOUT上,但注意仅捕获确定已建立相位时 的信号。像RTO1044这样的高级示波器,只有在满足某些条件时才允许事件触发激活:比如将特定的数字模式写入PLL器件以及已知信号的上升沿出现时。鉴于数字模式的写入与最终信号稳定之间可能会有一些延迟,因此在这两个事件之间插入一些延迟至关重要,这种特定型号的仪器就可以实现这一功能。

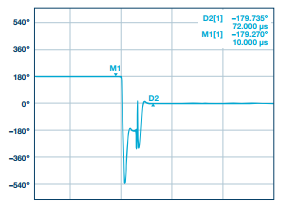

图1的测量是为了确认ADF4356 PLL相对于已知参考信号(在这种情况下,另一个ADF4356设定相同的输出频率)的相位延迟在上电时是否恒定和可重复。为了正确设置仪器,将两个低速 探头连接到 ADF4356 SPI 接口的 CLK 线路和 DATA 线路。若要将数字模式写入特定频率,则必须等待1秒钟,仪器才能捕获显示两 个PLL输出的时域图。

图1. 整数N分频设置

对于此测量,两个ADF4356 PLL锁定在4 GHz的VCO频率并在8 MHz 至500 MHz的范围内分频,其中一个PLL使用软件掉电功能反复 开启和关闭。示波器采用无限持续模式进行119次采集,两个 PLL之间的相位差恒定且可重复。为了确保相位差可重复,需 遵循许多注意事项。相比较而言,低的R分频值比高的R分频值 带来的不确定性较少,而且将来自VCO输出的分频反馈馈送到 N计数器输入至关重要。鉴于ADF4356 PLL和VCO包含1024个不同 的VCO频段,务必使用手动校准覆盖程序来消除此不确定性。

相位再同步定义

相位再同步是指小数N分频PLL在每个给定频率下返回相同相移的能力。也就是说,相位为P1的频率A在改为频率B后,当频率重新设定为回到F1时,观察到仍具有相同的原始相位P1。该定义忽略了由VCO漂移、漏电流、温度变化等因素引起的变化。

再同步将复位脉冲发送到小数N分频∑-∆调制器,从而使其处于 已知的可重复状态。在完成VCO频段选择和环路滤波器建立时 间等频率建立机制之后,需要施加此复位脉冲。其值由寄存 器12中的超时计数器控制。新近的PLL能够调整此复位脉冲的 时序,实现了一定程度的输出信号可调性。此外,它还能以 360°/225步进改变时序,比大多数仪器更轻松地完成测量。

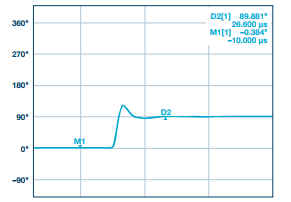

图2. 进行小数N分频再同步,频率范围4694 MHz至4002.5 MHz

对于本实验,两个ADF4356 VCO的频率均设定为4002.5 MHz且采 用8分频。第二个PLL的VCO频率设定为4694 MHz,然后设定为回 到4002.5 MHz。通过使用示波器检查PLL行为可以看出,在1700 次频率变化后,PLL每次都稳定在同一相位。

为了表征不同的相移特性,相位字设定为4194304/225(相当于 90°)。设定90°、180°、270°和0°的相应类似值,再次查看示波 图(图3)。

图3. 具有可变相移的相位再同步

相对于通道1上的原始信号,观察到四个间隔相等的信号,从 而确认了具有可编程偏移的相位再同步的准确性。

该功能非常有用,意味着可以为每个用户频率创建相位值查找 表,在每次使用时记录相位值。在需要组合四个同相LO频率的 应用中,相位再同步和偏移功能用于调整输出相位,从而共同 提供低6 dB的相位噪声。如果用作可调LO(可能在信号分析仪 的第一级上),再同步和相移功能允许用户在上电时执行一次 性校准以确定每个LO的精确相位值。在用作LO时,可以根据需 要按照每个LO设定相位值,从而无需在每个频率下执行校准。

图4. 需要精确控制PLL输出相位的相位关键型应用

对于像网络分析仪这样的相位关键型应用,该电路可以在上电 时测量每个频率下的相位值,然后根据需要设定,因为LO会作 用于整个目标范围。

测量相位、矢量信号和网络分析仪

矢量信号和网络分析仪也可用于表征相位行为,尽管其仅限用 于比较器件的相位与其初始值。可以将FSWP等高级分析仪置于 FM解调模式并选择相位输出。

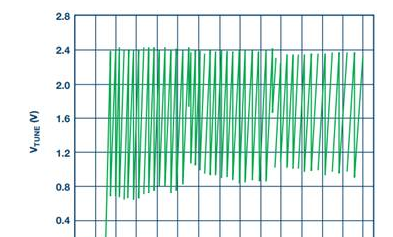

这对于评估ADF4356 PLL上的相位再同步功能非常有用。下面的 迹线(图5)表示ADF4356相位在5025 MHz的输出频率下变化了 180°。

图5. 180°相移时的FSUP FM解调器输出

相位调整

相位调整功能可避免∑-∆调制器复位,只需为现有相位添加一 个0°至360°之间的相位字即可。在不希望相位复位的应用中, 这一操作非常有用。它可以用于动态调整相位字以补偿由于温 度等影响而产生的相位差。

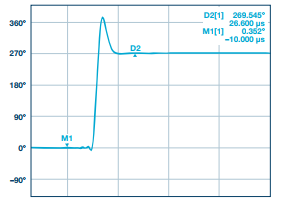

相位调整在R0每次更新(采用寄存器3的编程值)时为现有信 号添加相位。它不包含相位再同步等复位脉冲。以下来自FSWP 的测量结果表示的是原始信号增加90°(图6)和270°(图7)的 情况。在这两种情况下,ADF4356的输出频率在相位更改之前 都设置为5025 MHz。

图6. 90°变化

图7. 270°变化

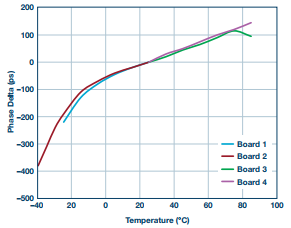

整个温度范围内的行为

电感器的物理参数随温度而变化,其电特性也一样,表现为相 位变化。为了减少这种相位变化,用户可以设定所需的相移以 保持相同的相位。输出频率设定为4 GHz的两个ADF4356 PLL,以 相同相位放置在同一炉室中,密切跟踪彼此的相位(图2), 从而证明用户可以根据温度调整相位。

图8. ADF4356在整个温度范围内的相位漂移,测量时的VCO频率为4 GHz。

波束成形是实现5G网络架构的一种关键技术。这些网络中使用 个天线阵列元件,每个元件具有不同的相位和幅度,将天线 能量直接传导到最终用户。对于该应用,相位重复性是关键。 波束成形需要LO相位具有可重复性,并且如果该相位具有不确 定性,则需要波束成形电路进行额外校准。

图9所示为相隔四分之一波长并由同相驱动的两个半波单元的 方向图。天线辐射图几乎是全向的,观察不到波束成形。

图9. 无波束成形

图10 显示了由90°异相信号驱动的两个元件,得到的辐射图显示辐 射图更加集中。随着元件阵列数量的增加,朝向最终用户的辐 射图的准确度也有所提升,进一步提高了光谱效率。

图10. 波束成形

相位再同步功能确保消除了LO相位特性的不确定性。此外,还 能够调整此相位,为用户提供了另一种方法来克服存在于电路 中而波束成形器或基带电路难以调整的任何其他相位延迟。

所以,相位再同步将ADF4356以及类似的PLL器件置于已知相位,这样可以实现许多应用并大大简化校准程序。你get到了吗?

-

ADI

+关注

关注

146文章

45834浏览量

250899 -

合成器

+关注

关注

0文章

273浏览量

25398

原文标题:ADI 深度丨RF合成器的相位校准和控制

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

合成器

详解频率合成器高性能架构的实现

基于DDS的频率合成器设计介绍

什么是宽带频率合成器件的相位校准和控制?

什么是频率合成器

ΣΔ技术在锁相环频率合成器中的应用

PLL频率合成器的噪声基底测量

频率合成器,频率合成器原理及作用是什么?

面向 RF 应用的低相位噪声频率合成器

pll频率合成器工作原理与pll频率合成器的原理图解释

RF合成器的相位校准和控制

RF合成器的相位校准和控制

评论