FPGA的设计就是将自己想要实现的逻辑通过计算机能够理解的语言描述出来,并让计算机根据FPGA内部的资源生成可以进行资源配置并在加电以后能够执行的过程。

人的逻辑和计算机之间的桥梁就是HDL - 硬件描述语言,目前有两个比较流行的语言Verilog和VHDL,其中Verilog用的更多,在我们的小脚丫FPGA平台上也选用了Verilog。

语言就是一个工具,不同的语言只是语法、规则不同而已,稍加了解这些语法、规则应该就可以方便地切换到不同语言上。因此在FPGA设计时,无论是Verilog、VHDL还是其它更高级的语言,这都不是FPGA的实质,我们在使用的时候也没有必要纠结用的是何种语言。

很多做FPGA设计的工程师都买过某著名教授的Verilog的教程,非常厚,但普遍反应看不懂,从头到尾看了好几遍,仍然不会做FPGA设计。

我翻看过基本英文版的FPGA设计的教程,没有一本是专门讲Verilog的语言的,多数是将Verilog的语法和规则作为附录放在书的后面供查阅。

因为Verilog实在太简单,所有的语法和规则汇总起来也就两个页面,对于学习FPGA的初学者来讲了解这些已经足够,更重要的是在实际的项目中通过具体的使用和调试来深刻掌握。

Verilog看起来跟C++比较像,但由于它是一门用于描述硬件的语言,因此它跟MCU上运行的程序不同,它有一些跟硬件高度相关的特性需要格外注意。如果把FPGA的逻辑用MCU程序的思路去写,那就大错特错了。

下面是我们www.stepfpga.com的Wiki系统里对Verilog的简要介绍(详细的语法和规则可以点击左下角的“阅读原文”指向的页面):

Verilog 是 Verilog HDL 的简称,Verilog HDL 是一种硬件描述语言(HDL:Hardware Description Language),硬件描述语言是电子系统硬件行为描述、结构描述、数据流描述的语言。利用这种语言,数字电路系统的设计可以从顶层到底层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化(EDA)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路 ASIC 或现场可编程门阵列 FPGA 自动布局布线工具,把网表转换为要实现的具体电路布线结构。

在 FPGA 的设计中,我们有多种设计方式,如绘制原理图、编写描述语言代码等。早期的工程师对原理图的设计方式情有独钟,这种输入方式能够很直观的看出电路的结构并快速理解电路。随着逻辑规模的不断攀升,逻辑电路也越来越复杂,这种输入方式就会显得力不从心,应付简单的逻辑电路还算实用,应付起复杂的逻辑电路就不行了。因此取而代之的便是编写描述语言代码的方式,现今的绝大多数设计都是采用代码来完成的。

简单地讲在Verilog编程中需要注意以下几点:

所有的Verilog程序都以Module(模块、组件)的方式存在,一个简单的逻辑可以由一个Module组成,复杂的逻辑可以包含多个Modules,每个Module有独立的功能,并由输入、输出端口被其它module调用。通过Module的方式可以将一些比较独立、可以复用的功能进行模块化,代码阅读起来也比较直观;

Verilog的信号分为wire和register两种类型,wire可以看成直接的连接,而register具有对某一个时间点状态进行保持的功能,因此在设计逻辑的时候要明确定义每个信号是wire还是reg属性;

并行执行:Verilog描述的主要是硬件而不是软件,因此也就意味着其描述的各个功能之间可以并行执行,比如在你的设计中你有3个计数器,每一个计数器都连接到不同的时钟上,这是没有问题的,每一个时钟都干自己的事。不像MCU,只有一个线程按照顺序执行。

由于篇幅所限,我们就不对这个语言的具体语法、规则进行展开,在此借用Stanford大学的Paul Hartke教授的Verilog课程的PPT页面来对Verilog的语法和规则做个简单的介绍(正好可以借此提升一下自己的专业英语阅读能力),可以看到斯坦福大学的学生学习Verilog也就十几个页面的内容。

使用Verilog设计FPGA的流程

Module是Verilog最基本构成方式

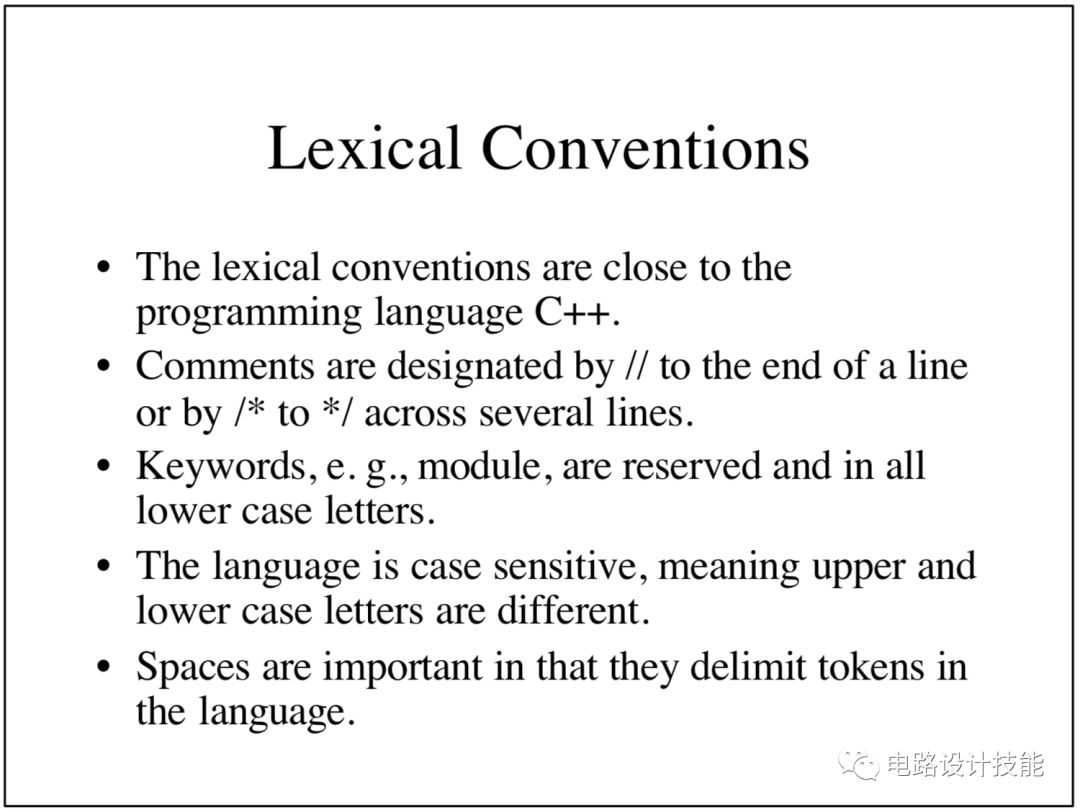

Verilog的语法规定跟C++比较接近

数值规范

按位/逻辑操作符

混合操作符

一元减数操作符(教授说它从来没有在实际的应用中看到过、用过)

连续赋值

过程赋值

if-else条件过程赋值

逻辑操作符

关系操作符

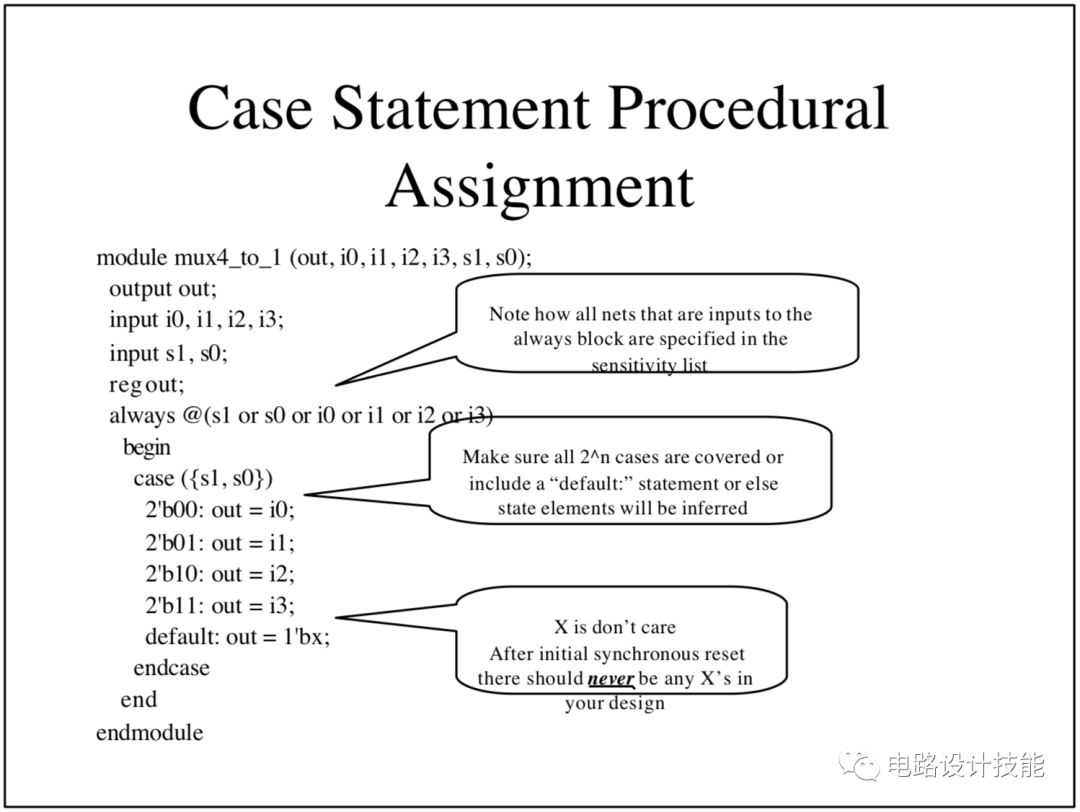

Case Statement过程赋值

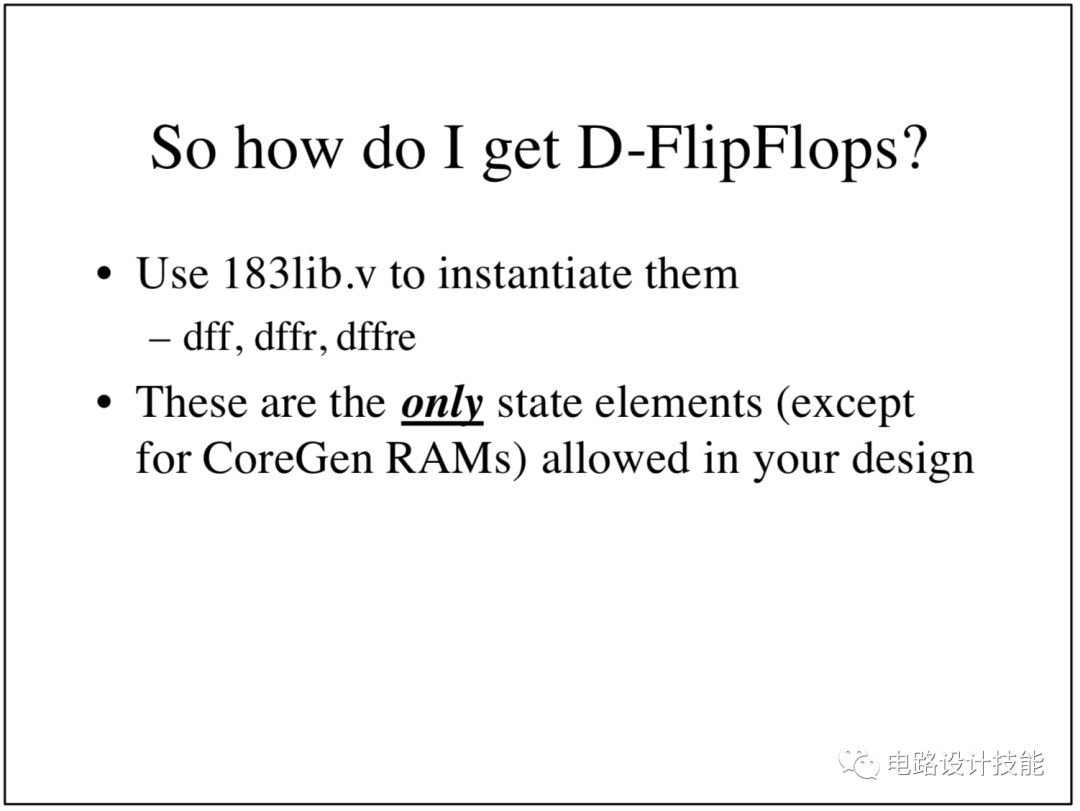

如何得到一个D触发器?

在有限状态机(FSM)中使用Case Statement

-

FPGA

+关注

关注

1631文章

21808浏览量

606807 -

Verilog

+关注

关注

28文章

1355浏览量

110544 -

编程

+关注

关注

88文章

3643浏览量

94128

原文标题:Verilog编程的要点

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【信盈达】C语言知识点的总结

《Verilog HDL数字系统设计教程》(第四版)学习笔记 part1 Verilog数字设计基础——第一章知识点总结

Verilog编程语言界面入门知识简介

使用C语言进行单片机编程的基本知识点和编程规范资料总结

Verilog是编程语言吗

开关电源模块知识点总结

Verilog设计过程中的一些经验与知识点

Verilog系统函数和边沿检测

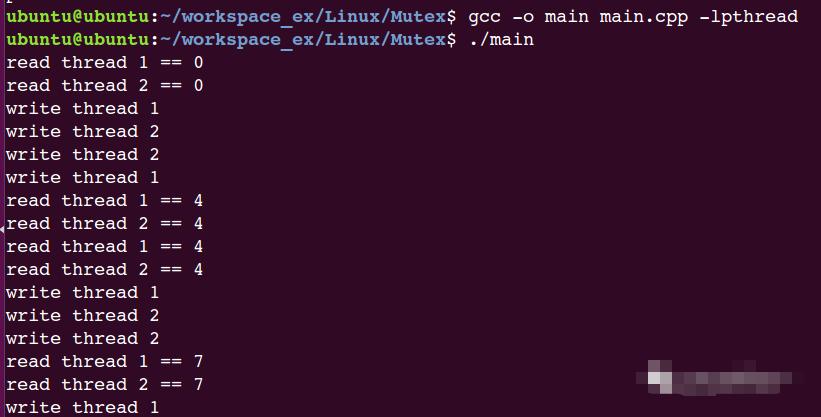

Linux中多线程编程的知识点

Verilog如何编程?Verilog编程知识点总结

Verilog如何编程?Verilog编程知识点总结

评论