这两天嵌入式领域最大新闻就是MIPS架构宣布开源了!昨天:曾经收购MIPS公司的美国AI公司Wave Computing宣布了一则重磅消息:正式启动MIPS Open项目,MIPS架构完全开源,免费提供给全球的开发者、合作伙伴、高校研究机构、客户。

MIPS开源社区将在2019年第一季度上线,届时会免费提供的MIPS IP和技术资源包括:32/64位指令集Releas 6版本、SIMD扩展、DSP扩展、MT多线程、MCU微控制器、VZ虚拟化、microMIPS架构。

未来,任何人都可以自由获得以上资源,无需任何授权费、版权费,并能在全球范围内得到几百项专利的保护。Wave Computing表示,更多的开源计划细节将在明年第一季度公布。

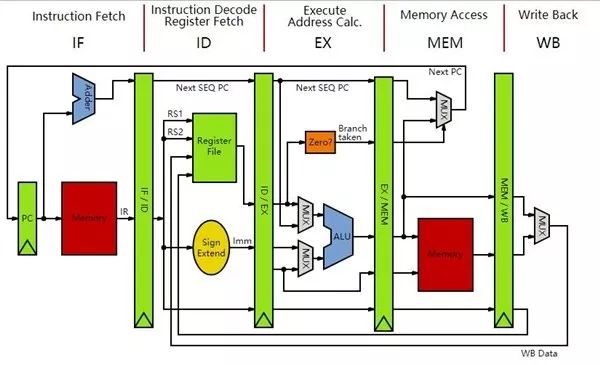

MIPS架构流水线简图

虽然之前的授权和新的开源计划并不能完全混合,但是Wave Comuting已经明确表示,会向授权客户提供开发工具、第三方IP资源,以构建更强壮、更完整的生态系统,再加上开源的丰富资源和全世界的努力。

01

MIPS指令集历史沿革

此次开源的是 MIPS 32/64位指令集Releas 6版本,MIPS指令集架构自上世纪80年代出现已经有35年历史了,其指令集一直在更新换代,从最初的MIPS I到MIPS V,发展到可支持扩展模块的MIPS32、MIPS64系列,再到集成代码压缩技术的microMIPS32、microMIPS64。每一个MIPS ISA都是其前一个的超集,没有不论什么遗漏,仅仅有添加新的功能。

1、MIPS Ⅰ

提供载入/存储、计算、跳转、分支、协处理及其他特殊指令。该指令集架构用于最初的MIPS处理器R2000/R3000。R2000是1985年推出的首款MIPS CPU,由110000个晶体管组成,是一个8MHz的32位处理器。R3000是R2000的下一代产品。与前者相比不过时钟频率不同。

2、MIPS Ⅱ

添加了自陷指令、链接载入指令、条件存储指令、同步指令、可能分支指令、平方根指令。最初计划用在MIPS 处理器R6000上,但因为工艺选择的问题,R6000从1988年開始设计后,就一直问题不断,终于未能大规模生产。但MIPSⅡ指令集架构是后期MIPS32指令集架构的直接先驱。

3、MIPS Ⅲ

提供了32位指令集,同一时候支持64位指令集。最初用于MIPS处理器R4000。R4000是于1991年推出的64位处理器,首次增加了浮点处理器单元,主时钟频率提高到了100MHz。后来出现了一系列的R4000处理器。

4、MIPS Ⅳ

在MIPS III基础上添加了条件移动指令、预取指令以及一些浮点指令。最初用于MIPS处理器R8000,后来应用于R5000/R10000。R5000与R10000尽管使用同样的指令集架构。可是两者微架构的设计理念全然不同。R5000于1995年推出。採用的是经典的五级流水线、顺序运行。R10000于1996年推出,採用的是乱序运行。

MIPS IV是该架构的第四个版本。它是MIPS III的超集,与所有现有版本的MIPS兼容。 MIPS IV旨在主要改善浮点(FP)性能。为了改善对操作数的访问,添加了用于FP加载和存储的索引寻址模式(base + index,均来自GPR),以及用于执行内存预取和指定缓存提示的预取指令(这些指令支持基数+偏移量和基数) +索引寻址模式)。

MIPS IV增加了几个功能来改善指令级并行性。为了缓解由单个条件位引起的瓶颈,将七个条件码位添加到浮点控制和状态寄存器,使总数达到8。重新定义FP比较和分支指令,以便它们可以指定分别写入或读取哪个条件位;并且去除了读取通过先前FP比较写入的条件位的FP分支之间的延迟时隙。对GPR和FPR的条件移动指令形式增加了对部分预测的支持;并且实现可以选择具有IEEE 754陷阱的精确或不精确的异常。

MIPS IV为单精度和双精度FPN添加了几个新的FP算术指令:融合乘法加法或减法,倒数和倒数平方根。 FP融合乘法加或减指令执行一个或两个舍入(它是实现定义的),以超过或满足IEEE 754精度要求(分别)。 FP倒数和倒数平方根指令不符合IEEE 754精度要求,并且产生的结果与最后一个位置的一个或两个单位(所实现定义)的要求精度不同。这些指令适用于指令延迟比准确性更重要的应用。

第一个MIPS IV实施是MIPS科技R8000微处理器芯片组(1994)。 R8000的设计始于Silicon Graphics,Inc。,它仅用于高端工作站和服务器,用于科学和技术应用,其中大型浮点工作负载的高性能非常重要。后来的实施是MIPS Technologies R10000(1996)和Quantum Effect Devices R5000(1996)和RM7000(1998)。由NEC电子和东芝制造和销售的R10000及其衍生产品被NEC,Pyramid Technology,Silicon Graphics,Inc。和Tandem Computers(以及其他公司)用于工作站,服务器和超级计算机。 R5000和R7000可用于高端嵌入式系统,个人计算机以及低端工作站和服务器。东芝R5000的衍生产品R5900用于索尼电脑娱乐公司的Emotion Engine,后者为其PlayStation 2游戏机提供动力。

5、MIPS Ⅴ

在MIPS IV的基础上添加了能够提高代码生产效率和数据转移效率的指令。可是没有不论什么一个处理器基于该架构。MIPS V指令集架构是后期MIPS64指令集架构的直接先驱。

6、MIPS32/64

MIPS32/64于1998年提出,MIPS32以MIPS II架构为基础,选择性地增加了MIPS III、MIPS IV、MIPS V,提高了代码生成和数据移动的效率。

MIPS64以MIPS V架构为基础,同一时候兼容MIPS32。

该架构第一次包括了被称为协处理器0的“CPU控制”功能。1999年以后设计的大多数MIPS处理器都与该标准兼容。2003年。公布了MIPS32/64指令集架构的第二版(Release 2),也称为MIPS32/64 R2。最新的是第六版(Release 6),也称为MIPS32/64R6。

而广泛使用的是第二版。很成功的MIPS 4K、24K系列处理器遵循的就是MIPS32 R2架构。MIPS32/64在基本指令的基础上,还提供了一些面向特定应用的指令。这些指令採用特定应用扩展(ASE:Application-SpecificExtensions)的形式。

一种处理器是否实现了某种扩展。能够通过设置标准的配置寄存器指明。基本的扩展列举例如以下。

MIPS 16e:是专门为嵌入式系统及存储空间有限情况下的应用而设计的,能够在一个程序中运行16位和32位两种混合长度的指令,能使终于代码长度降低40%。MIPS32、MIPS64都支持MIPS 16e。

SmartMIPS:是为了满足智能卡和灵活小系统的市场须要而设计的。是一套能高效节省存储空间的扩展指令集,此外还能提高智能卡领域很关键的加密运算的性能。MIPS32支持SmartMIPS。

MIPS-3D:提供了更好的几何运算处理,具有成对单精度数据类型,还提供专用指令来加快对该类型数据的处理。MIPS64支持MIPS-3D, MIPS32第二版也支持MIPS-3D。

MCU:Micro-Control Unit微控制单元,增强了内存映射I/O的处理、提供了更低的中断延迟。MIPS32、MIPS64都支持MCU。

7、microMIPS32/64

microMIPS32/64指令集架构集成了16位和32位优化指令的高性能代码压缩技术,保持了98%的MIPS32性能,同一时候减少了至少30%的代码体积,从而减少芯片成本,也有助于减少系统功耗。MIPS M14K内核是MIPS科技于2009年公布的首款遵循microMIPS指令集架构的MIPS32兼容内核。

注意其序列中没有Release 4,这是由于对于非常多人来说。4是个不吉利的数字。所以MIPS没有公布Release 4,而是直接公布Release 5。

MIPS32 / MIPS64R6

2014年MIPS32 / MIPS64第6版增加了以下内容:

一个没有延迟槽的新分支系列:

具有26位偏移的无条件分支(BC)和分支链接(BALC),

具有21位偏移的零/非零条件分支,

两组寄存器(例如BGTUC)或零寄存器(例如BGTZC)之间的全套有符号和无符号条件分支比较,

全套分支和链接,将寄存器与零进行比较(例如BGTZALC)。

索引跳转指令没有延迟槽,旨在支持大的绝对地址。

指令在位位置16,32或48处加载16位立即数,允许轻松生成大常量。

PC相对负载指令,以及具有大(PC相对)偏移的地址生成。

位反转和字节对齐指令(以前仅适用于DSP扩展)。

乘法和除法指令重新定义,以便他们使用单个寄存器作为结果)。

生成真值的指令现在生成全零或全1,而不是仅清除/设置0位,

使用真值的指令现在只将全零解释为假而不是仅仅查看0位。

删除了不经常使用的说明:

一些有条件的举动

分支可能的指令(在以前的版本中已弃用)。

16位立即数的整数溢出陷阱指令

整数累加器指令(一起HI / LO寄存器,移动到DSP应用专用扩展)

未对齐的加载指令(LWL和LWR),(要求大多数普通的加载和存储支持未对齐的访问,可能通过陷阱和添加新指令(BALIGN))

重新组织指令编码,为将来的扩展释放空间。

02

MIPS CPU架构开源打击了谁?

在业界,虽然MIPS架构的生态系统成熟度比不过ARM,但超过RISC-V是绰绰有余了,作为一种全新的、简且开源的指令集架构,RISC-V 因开源且没有版税而被众多企业、研究机构所采纳,2018堪称RISC-V爆发的元年,各种有关RISC-V的研讨会不断,同时,中国RISC-V产业联盟也宣告成立,为RISC-V在中国的全面应用打下了基础。

SiFive CEO NaveedSherwani在近日ICCAD2018上接受采访时表示RISC-V生态趋于成熟和完善,并透露许多半导体厂家发布了产品或者宣布了产品推出的计划,比如西部数据,高通,英伟达,FADU,以及国内的华米,比特大陆,嘉楠耘智等。Naveed Sherwani还指出今年10月份微软就只花费两个月时间便开发出了一款芯片,未来几年RISC-V的发展将会不断的提速,将有更多的公司更快地发布他们的芯片。详见《目前形势下本土IC该如何做强做大?》但即便如此,RISC-V的IP积累还是不够。

另外,可能大家对RISC-V的free有点误解,其实这里的free不是免费是自由的意思,对于RISC-V指令集,如果你是个人或者科研机构可以下载其源代码用于研究,如果要进行商业化操作比如大批量的量产,这就需要SiFive的授权了,只是RISC-V指令集的授权费要比ARM低很多而起不收芯片版税。所以RISC-V并不是一个完全免费的指令集。

还有,有本土IC设计公司老大提出了不同意见,他认为纵观CPU技术发展历史任何一款CPU的走热或者存在都是因为以大量应用为基础 ,对于RISC-V 目前至今还未看到有爆量的单一产品出现,另外,RISC-V虽然免费降低了IC开发者的难度,提升了最终系统开发者的难度,而一些商用CPU已经很好的开发基础和生态,例如X86只要简单的编程就可以开发应用,对此,RISC-V还没有形成自己的成熟的开发环境,如果单纯让应用端的开发人员去买单花时间去学习开发这不符合商业规律。

他认为应用的碎片化不能代表参与者的碎片化,对于很多中小公司来说如果盲目跟进RISC-V则可能遭遇很大风险,他算了一笔账一款芯片从定义到应用走量至少5年时间,如果一个20人的团队要开发一款RISC-V应用则至少需要投入近一个亿的资金,“谁愿意一次性给你一个亿让你来烧?”他表示。所以他认为RISC-V最终是一场开源闹剧,不看好其未来。详见《RISC-V是振兴中国芯CPU的一剂良药吗?》

而现在随着MIPS宣布开源,ARM Cortex-M0免费(1000颗以内免费),RISC-V的生存环境可能遭遇进一步挤压,所以有业者戏称:“RISC-V使命完成了。”大家咋么看?

-

微控制器

+关注

关注

49文章

8906浏览量

166005 -

cpu

+关注

关注

68文章

11364浏览量

226319 -

mips

+关注

关注

1文章

245浏览量

49668

原文标题:MIPS CPU架构宣布开源,RISC-V使命完成了?

文章出处:【微信号:mcuworld,微信公众号:嵌入式资讯精选】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Arteris 与 MIPS 达成合作,携手加速物理 AI 平台开发

物理AI落地:为何选择MIPS Atlas RISC‑V IP?

MIPS 推出软件优先的 S8200 RISC-V NPU,赋能自主边缘物理 AI

Wave Computing宣布了一则重磅消息:正式启动MIPS Open项目,MIPS架构完全开源

Wave Computing宣布了一则重磅消息:正式启动MIPS Open项目,MIPS架构完全开源

评论