比如覆铜间距16mil,其他安全间距8mil,过孔到过孔间距100mil,焊盘到过孔间距100mil,顶层地覆铜0.8mm,顶层VCC3.3与VCC1.8覆铜间距0.5mm等。

Altium Designer的间距规则默认为一个1Omil间距,没有区分焊盘到焊盘,过孔至挝孔,走线到覆铜等的间距,想要高级规则,必须自己建立。

在PCB设讹不境下Design>Rules>Elecvical>Clearance,同样右键新建一个间距规则并重命名为Poly, Where The First Object Matche选Adcanced (Query), Full Query输入in polygpon, Constraints 把默认的1Omil修改为2Omil,优先级 Poly 比默认的Clearance 的10mil高,这2个间距规则共同构成覆铜间距为20mil,其他间距,例如走线到走线,走线到焊盘过孔间距为10mil的规则,如下图:

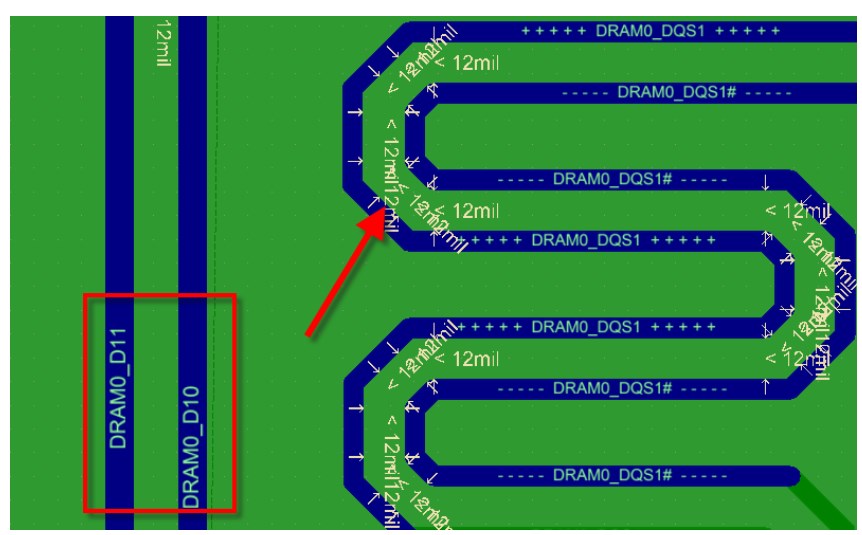

下2图是过孔覆铜全连接 viaconnect,默认安全间距clearance 8mil,覆铜间距16mil 规则的覆铜,inpolygon是所有的覆铜,如果想要其他覆铜间距,则需要在新建覆铜规则,比如VCC3.3 覆铜0.5mm,VCC1.8 覆铜间距0.6mm,其他覆铜0.4mm;优先级16mil的最低;覆一片铜到VCC3.3网络同时起名该覆铜为VCC3.3-ALL; 覆一片铜到VCC1.8网络同时起名该覆铜为VCC1.8-ALL;同样要兴建间距规则,见下面第3-6张图:

下图是过孔到过子幽间距规则, Where The First Object Matches Where The Second Object Match的Full Query,只有这2个参数一个是is via,另一个是is pad即可;如果一个是is pad另一个是isvia,那就是过孔到焊盘的间距;如果一个是is pad另一个是is pad,那就his焊盘到焊盘的间距;随后填入具体的数据就可以了。Where The Second Object Match的默认是All,修改它就是第一个和第二个间距规则,is via和All就是via到其他的间距规则,is via 和is via 就是过孔到过孔的间距规则。

过孔到过孔间距没有到2.54mm的在线DRC检查出来绿色显示;

注:设置小间距管脚间距:一些FPGA芯片等很多焊盘间距多达到了0.2mm,默认的10mil(0.254mm)间距显然是冲突的,上述问题可以通过HasFootprint('PQ208')或IsPad and InComponent('U1'); (IsPad and InComponent('JP4')) or(IsPad and InComponent('JP3')) HasFootprint('PQ208'),封装为PQ208的元件;sPad and InComponent('U1'),元件U1的管脚间的间距;

如果你想了解更全面的pcb规则设置,

可查看我们的实战124讲视频

上面2个规则只是管脚间距,从上面拉出来的线的间距是其他的规则值.当然不能太大:比如上面的P0208 焊盘0.3mm. 焊盘间距 0.2mm.布线0.2mm。那拉出来的间距就是0.4mm,如果把布线的间距设置为0.5mm,1mm,要么拉布出来。要么绿色。

{IsPad and InComponent('JP4')} Or{IsPad and InComponent('JP3')}元件JP3, JP4的间距规则:见下面3张图:

下图是一个定位孔间距为3mm的间距规则:常用一个内孔=等于外孔的焊盘做定位孔。该孔不连接到任何网络(不进行电气连接),只拧螺丝用。我们在PCB上4个脚上放4个定位孔不连接到任何网络,焊盘名称起为HOLE,内孔=外孔大小;free-hole含义free不连接到任何网络,Hole焊盘名称;可以是free-0,fret-1, free-2等等;

下图为一个在toplaye层覆铜名为SVANA 的间距规则,当然Toplayer可以换成其他层,SVANA可以换成其他覆铜的名称:

下图为DM到DP网络间距为20mil的间距规则:

下图为MSCLKI网络到其他间距为16mil的间距规则;

-

pcb

+关注

关注

4329文章

23196浏览量

400831 -

AD

+关注

关注

27文章

870浏览量

150665

原文标题:PCB规则 —— AD高级间距规则

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AD_PCB高级规则 altium designer pcb advance rule

Altium Designer高级规则语法参考PCB查询功能的详细资料说明

PCB设计之电气(Electrical)规则设置

PCB规则之AD高级间距规则

PCB规则之AD高级间距规则

评论