据麦姆斯咨询介绍,为了降低成本,半导体行业一直在致力于开发创新的解决方案。而终端客户则一直在寻求具有更高性能的低成本封装解决方案。

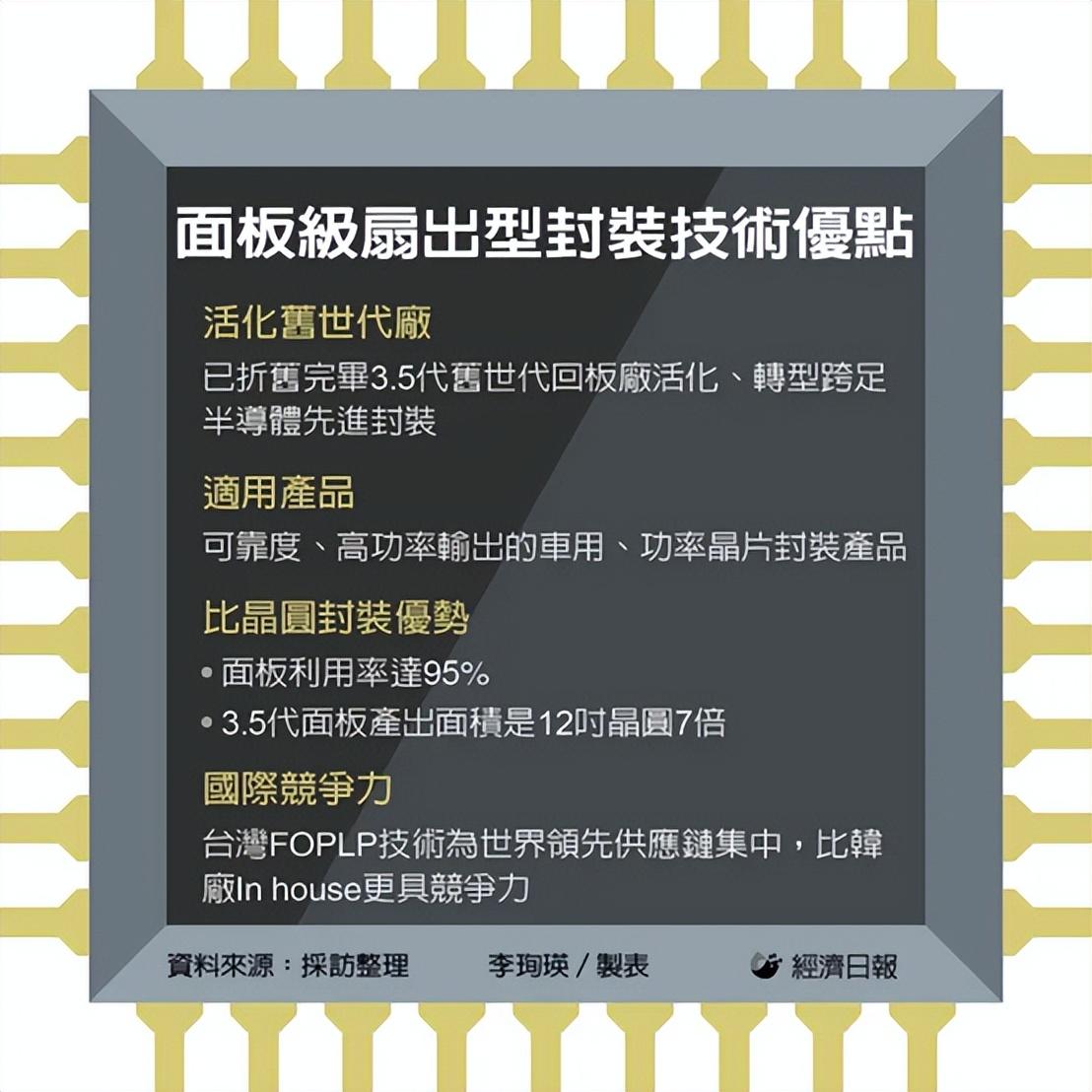

面板级封装(PLP)就是一种从晶圆和条带级向更大尺寸面板级转换的方案。由于其潜在的成本效益和更高的制造效率,吸引了市场的广泛关注。由于面板的大尺寸和更高的载具使用率(95%),它还带来了远高于晶圆级尺寸扇出型晶圆级封装(FOWLP)的规模经济效益,并且能够实现大型封装的批量生产。

在应用和市场方面,许多封装技术可以被视为PLP,但由于FOWLP的成功和市场认识,使FOPLP吸引了更多关注,包括许多不同商业模式的厂商,例如外包半导体组装和测试厂商(OSAT)、集成器件制造商(IDM)、代工厂、基板制造商和平板显示(FPD)厂商。它们感觉有机会通过扇出型技术涉足先进封装业务。

经过多年的发展,FOPLP已经成功开发,2018年至2020年期间将有多家厂商开始量产。FOPLP将成为增长最快的封装平台之一:根据Yole在2018年发布的《板级封装(PLP)技术及市场趋势-2018版》报告,FOPLP市场将在2017~2023年期间以惊人的79%复合年增长率(CAGR)在2023年增长至约2.79亿美元。

板级封装平台的市场驱动因素

众多涉足FOPLP业务的厂商中,三星电机(SEMCO)可能是最激进的:这家领先的公司过去两年来在该领域投资超过4亿美元,并最终利用该技术为其新款消费类产品——Galaxy Watch智能手表生产集成应用处理器单元(APU)。

凭借这一高密度FOPLP的首次亮相,SEMCO率先宣布了FOPLP的到来。利用这项技术,三星Galaxy Watch将电源管理集成电路(PMIC)、应用处理器和动态随机存取存储(DRAM)都集成在了同一个大型封装中(称为SiP-ePoP)。PMIC和应用处理器芯片并排放置,利用一个嵌入式PCB基板实现封装中顶部/底部的连接。

针对这款产品,麦姆斯咨询合作伙伴——System Plus Consulting近期发布了一份题为《Exynos 9110:三星第一代扇出型面板级封装(FOPLP)》的报告。

随着FOPLP在智能手表中的应用,三星显然正准备在消费领域大展拳脚。除了智能手表,移动市场应该很快会受到FOPLP应用的影响。凭借这一战略性技术选择,SEMCO明确瞄准了台积电(TSMC)在高密度扇出封装领域的领导地位,并为FOPLP的技术开发制定了积极的发展路线图。现在,巨头之间在高端扇出型封装领域的较量即将上演。

在此背景下,Yole韩国分部负责人兼首席分析师Santosh Kumar最近采访了SEMCO副总裁兼企业战略与规划团队负责人Richard(KwangWook)Bae,了解了SEMCO近期的FOPLP发展情况,以及他们对FOPLP业务的愿景和未来趋势的看法。

Santosh Kumar(以下简称SK):请您简要介绍一下SEMCO及其业务。

Richard(KwangWook)Bae(以下简称RB):SEMCO成立于1973年,是三星集团的附属子公司。SEMCO的全称是Samsung Electro-Mechanics,是电子元件行业的领导者之一。

我们的总部位于韩国水原。海外工厂位于中国、泰国、菲律宾和越南。我们还在美国、欧洲、日本、中国和东南亚设有销售办事处。

SEMCO现在主要由三个业务部门组成:

元件解决方案,生产无源元件,如多层陶瓷电容(MLCC)和电感;

基板解决方案,生产高密度互连板(HDI)、封装基板和RFPCB;

模组解决方案,生产摄像头模组、WiFi模组。

2016年,我们成立了新的FOPLP部门,并建设了生产线。我们开始为2018年8月发布的Galaxy Watch制造用于应用处理器(AP)的FOPLP产品。

SK:恭喜你们成为第一家FOPLP进入量产的厂商。您能否介绍一下SEMCO的FOPLP技术,包括面板尺寸和技术规格。

RB:我们使用510 x 415mm尺寸的面板制造FOPLP,但我们已经开发出了高达800 x 600mm规格的面板。因此,面板尺寸可以根据客户要求更改。

我们用于Galaxy Watch的FOPLP有3个重布线层(RDL)和1个背面RDL(Backside RDL)。我们将标准的层叠(PoP)结构应用于AP和PMIC的多芯片封装。通过应用FOPLP,我们可以将封装的厚度减少20%以上,从而提高了电气和热性能,并有助于扩大产品的电池容量。

SK:涉足扇出型封装业务,SEMCO进入了由OSAT和一家大型代工厂主导的领域。您如何看待面临的挑战?您认为谁将是你们在扇出型封装领域更大的竞争对手:代工厂还是OSAT?未来,你们是否计划扩展封装服务组合?

RB:我认为半导体行业未来将划分为两大板块:

独特的业务仍然存在:代工厂、OSAT、基板公司将维持自己的业务;

供应链的分工将逐渐变得模糊,前端和后端之间的边界将不再那么分明。

从根本上来说,我们认为未来代工厂、OSAT、基板公司自己的业务将继续维持。但是,在前端和后端整合的部分,我认为需要三个条件:

1、大规模投资;

2、克服技术障碍;

3、克服先进节点晶圆的供应问题。

SK:从经济角度来看,产业对于面板级扇出封装的可行性存在一些疑虑。大多数厂商认为,由于市场规模还不足以满足产线的满产运行,因此,行业仍然没有做好迎接扇出型面板级封装的准备。您对这种观点有什么看法?

RB:首先,AP、PMIC等单芯片封装需要大规模生产,因此需求量预计已经足够了。我们正在与客户合作以响应它们的要求。此外,对于异构集成和扇出型系统级封装(FOSiP),多个芯片将被封装到一个大型封装中。

面板级比晶圆级更具竞争力。随着封装尺寸的增长,晶圆面积的利用率正在降低。因此,对于FOSiP,来自面板的封装数量多于来自晶圆的封装数量。由于这些原因,FOPLP应该有利于异构集成或FOSiP。此外,各种应用的市场需求也将继续增长。

SK:就芯片/封装尺寸方面,扇出型面板封装的优势在哪里体现?对于此类封装尺寸,转换到面板级封装,您预计可以降低多少成本?

RB:目前FOPLP主要用于移动应用。但在不久的将来,FOPLP将扩展到尺寸超过15 x 15的异构集成。

到2020年或2021年,由于5G、人工智能(AI)、自动驾驶和服务器需求,对模块化和高速数据处理的需求将急剧增长。FOPLP可以满足这些需求,因此在多芯片封装方面,FOPLP将成为主流。

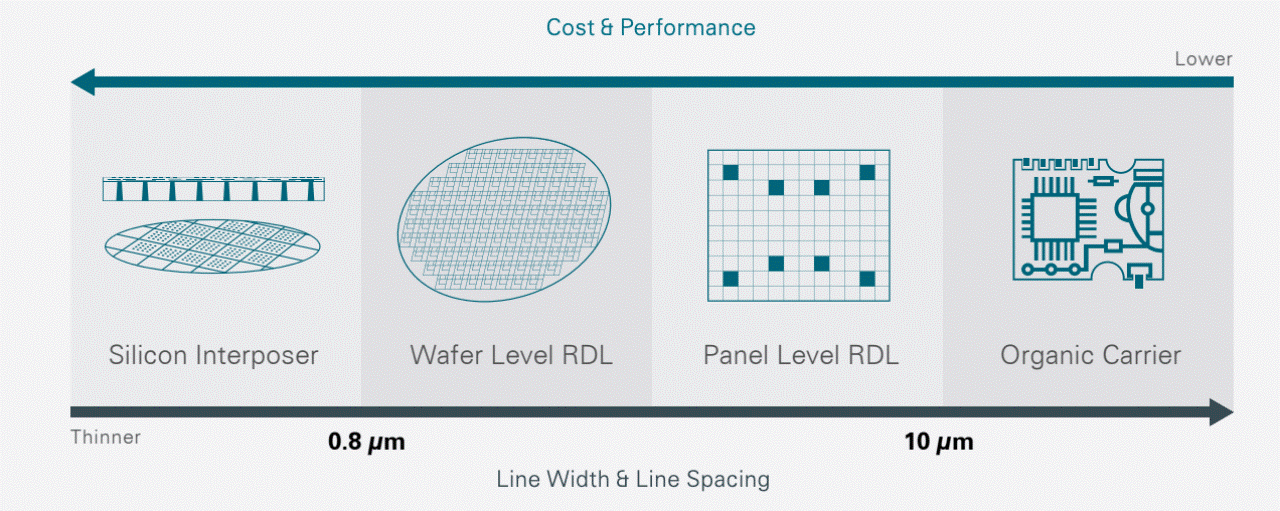

FOPLP和FOWLP之间的比较,仅在成本方面进行了讨论。但是,我认为FOPLP有两种类型的应用,一种是成本驱动型,另一种是性能驱动型。在成本驱动的领域,FOPLP在生产方面具有优势。然而,就性能驱动的应用而言,由于SEMCO设计的架构,FOPLP在精细间距方面更胜一筹,同时改善了热性能和电气性能。因此,对于扇出系统级封装和异构集成它都能胜任。

Galaxy手表及Exynos 9110拆解与逆向分析

SK:SEMCO是主要的基板供应商之一。您如何看待扇出型封装的广泛应用对基板业务产生的不利影响?SEMCO的应对策略是什么?

RB:SEMCO已经为无源和有源器件的嵌入技术准备了10余年。由于半导体节点在不断缩小,我们认为封装基板应该做出改变。

基于这些准备,我们及时开发出了FOPLP,并积极响应需要扇出封装的市场,例如高阶AP、内存和小型IC等。

我们专注于无源元件(包括MLCC、基板和模组)等电子元件。因此,我们可以通过其他组件的定制化来优化FOSiP。

此外,还有一些应用需要继续使用现有的封装基板。并非所有应用都会从基板转向PLP。因此,这不是一场零和游戏。此外,基板业务将支持FOPLP业务。

基于基板和PLP技术,我们可以更好地响应客户需求和技术的变化。

SK:你们的FOPLP面向哪些细分应用和器件?

RB:SEMCO为Galaxy Watch实现了FOPLP的全球首次量产。此外,我们期望将FOPLP不仅应用于小型IC,还包括AI、5G、汽车和服务器等高性能计算(HPC)应用。特别是,我们为各种应用开发了下一代扇出型系统级封装模组(FOSiP)。

SK:许多设备供应商已经开发了应用于面板级扇出技术的机台。在您看来,设备供应链中存在哪些差距需要解决?

RB:SEMCO自2015年以来一直与全球设备公司共同开发FOPLP。我们得到了这些公司的充分支持,因此未来不会出现问题。

SK:面板尺寸的标准化是面板级扇出应用的瓶颈之一。许多厂商正在研究不同的面板尺寸。您认为这个问题将如何解决?

RB:我们使用415 x 510面板,因为它是我们当前应用的最高效的尺寸。此外,在市场上,我们的面板尺寸被认为足以满足当前的应用。

由于SEMCO拥有基板业务,我们已经拥有更大面板的批量生产经验。我们可以将这些积累用于FOPLP业务。我们可以灵活地响应面板尺寸的变化,不会有任何问题。

对于成本驱动的应用,目前有几家供应商正在开发FOPLP。在这种情况下,如果面板尺寸、载具和材料是标准化的,我认为这对FOPLP生态系统是有利的。

SK:与FOWLP相比,您是否看到FOPLP对模塑料、介电材料、电镀化学等材料的特殊要求?

RB:基本上,FOWLP和FOPLP使用类似的PID材料、设备和条件。不同之处在于形状和材料不同的载具类型。

SK:FOPLP面临的主要技术挑战是什么?你们如何应对这些挑战?

RB:FOPLP中的技术问题主要包括大面积RDL形成、焦深裕度(DoF margin)、芯片位移、翘曲处理和微粒控制。SEMCO已经解决了这些挑战,掌握了控制技术。

SK:您认为FOPLP市场将如何发展?更广泛应用的主要障碍是什么?

RB:到2020年或2021年,由于5G、AI、自动驾驶和服务器等高性能计算需求,半导体器件将变得更加复杂。同时,还将需要在存储器和逻辑芯片之间进行高速数据传输。由于FOPLP能够通过多芯片封装实现高速数据传输,因而将促进FOPLP的更广泛应用。

SK:对于异构集成和2/2 L/S或以下的封装能力,您是否认为面板级扇出路线图和晶圆级扇出路线图一致(甚至超过)?SEMCO未来5年的FOPLP路线图(在封装设计参数方面,如RDL L / S和层数、间距、厚度、尺寸等)将如何规划?

RB:如前所述,FOWLP和FOPLP是类似的技术。所以路线图和目标应用基本相似。

不过,PoP堆叠的间距规格有差异。由于结构上的差异,我们的PLP可以获得更好的间距。此外,PLP具有不需要芯片凸点的优势。

作为电子器件工程联合委员会(JEDEC)标准, 2/2 L/S足以满足未来高性能计算或FOSiP等高端应用的需求。很少需要低于2/2的L/S,那些仅是一些特殊产品的利基市场。

-

三星电子

+关注

关注

34文章

15859浏览量

180973 -

封装

+关注

关注

126文章

7865浏览量

142879

原文标题:三星先进封装战略:扇出型面板级封装(FOPLP)

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

三星电容的封装形式有哪些选择?

整合为王,先进封装「面板化」!台积电、日月光、群创抢攻FOPLP,如何重塑封装新格局?

三星扇出型面板级封装FOPLP战略性技术选择

三星扇出型面板级封装FOPLP战略性技术选择

评论