一

仿真是指使用设计软件包对已实现的设计进行完整的测试,并模拟实际物理环境下的工作情况。FPGA设计验证包括功能仿真、时序仿真和电路验证,它们分别对应整个开发流程的每一个步骤。

功能仿真是指仅对逻辑功能进行模拟测试,以了解其实现的功能是否满足原设计的要求,仿真过程没有加入时序信息,不涉及具体器件的硬件特性,如延时特性等,因此又叫前仿真,它是对HDL硬件描述语言的功能实现情况进行仿真,以确保HDL语言描述能够满足设计者的最初意图。

时序仿真则是在HDL可以满足设计者功能要求的基础上,在布局布线后,提取有关的器件延迟、连线延时等时序参数信息,并在此基础上进行的仿真,也成为后仿真,它是接近于器件真实运行状态的一种仿真。

二

仿真软件ModelSim及其应用

HDL的仿真软件有很多种,如VCS、VSS、NC-Verilog、NC-VHDL、ModelSim等,对于开发FPGA来说,一般是使用FPGA厂家提供的集成开发环境,他们都有自己的仿真器,如Xilinx公司的ISE,Altera公司的Quartus II等,但是这些厂家开发的仿真器的仿真功能往往比不上专业的EDA公司的仿真工具,如ModelSim AE(Altera Edition)、ModelSim XE(Xilinx Edition)等。Quartus II设有第三方仿真工具的接口,可以直接调用其他EDA公司的仿真工具,这极大地提高了EDA设计的水平和质量。

ModelSim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述语言的仿真软件,该软件可以用来实现对设计的VHDL、Verilog HDL或是两种语言混合的程序进行仿真,同时也支持IEEE常见的各种硬件描述语言标准。

无论是从使用界面和调试环境,还是从仿真速度和效果上看,ModelSim都可以算的上是业界比较优秀的HDL语言仿真软件。它是唯一的单内核支持VHDL和Verilog HDL混合仿真的仿真器,是做FPGA/ASIC设计的RTL级和门级电路仿真的好选择,它采用直接优化的编译技术,Tcl/Tk技术和单一内核仿真技术,具有仿真速度快,编译的代码与仿真平台无关,便于IP核的保护和加快错误程序定位等优点。

ModelSim分几种不同的版本:ModelSim SE、ModelSim PE、ModelSim LE和ModelSim OEM,其中的SE、PE、LE是其最高版本,编译速度是所有版本中最快的,而OEM版本就是集成在FPGA厂家设计工具中的版本,它们专门和某个厂家的FPGA配套来使用,如后面使用到的ModelSim AE就是专门针对Altera公司QuartusII的配套的OEM产品。

三

ModelSim的仿真流程

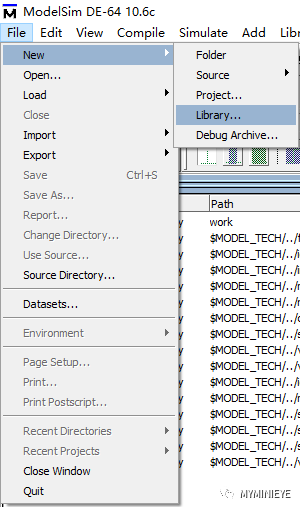

ModelSim不仅可以用于数字电路系统设计的功能仿真,还可以应用于数字电路系统设计的时序仿真。ModelSim的使用中,最基本的步骤包括创建工程、编写源代码、编译、启动仿真器和运行仿真五个步骤,仿真流程如图1所示:

图1 ModelSim仿真的基本流程(基于工程的)

这个是基于工程的流程,还有一种是基于库文件的,和基于工程的相比,它需要自己创建工作库,另外关闭ModelSim软件后,下次还得自己手动打开设计文件,而基于工程的就不会这样,工程是一直保持的状态,不用每次启动软件后再手工加载,除非我们自己关掉这个工程。

四

仿真测试文件程序的设计方法

随着设计量和复杂度的不断增加,数字验证变得越来越难,所消耗的成本也越来越高,面对这种挑战,验证工程师必须依靠相应的验证工具和方法。对于大型的设计,比如上百万门的设计验证,工程师必须使用一整套规范的验证工具,而对于较小的设计,使用具有HDL Test Bench的仿真器是一个不错的选择。

一般来说,Test Bench使用工业标准VHDL或者Verilog HDL语言来描述,简单的Test Bench通过调用用户设计的功能模块,然后进行仿真,较为复杂的Test Bench还包括一些其他的功能,比如包含特定的激励向量或者进行实际输出与期望的比较等。

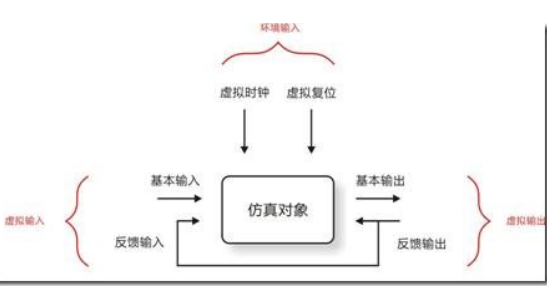

在开始写Test Bench之前,很重要的一点就是要设计实例化DUT(Design Under Test,即就是被测元件),还要详细了解整个的测试计划和测试案例。整个的测试Test Bench环境如图2所示:

图2 Test Bench的测试环境

从图中可以看见,Test Bench和被测对象Counter构成了一个封闭的循环,Test Bench负责向被测元器件的输入端口提供激励(时钟)和一些控制信号(复位和置位信号),另外Test Bench还监测被测元器件的输出端口所输出的信号值是否和我们的设计预期相符,并把监测的情况显示给我们。

由于Test Bench程序和被测对象构成了一个封闭的循环,因此Test Bench的输入端口需要与被测对象的输出端口连接,Test Bench的输出端口则要与被测对象的输入端口相连接。所以在端口的定义上,Test Bench程序需要和被测对象相对应。

被测元器件是一个已经设计好的电路或系统,Test Bench是用元件例化语句将其嵌入程序中。VerilogHDL测试平台是一个设有输入输出端口的设计模块,被测元器件的输入端定义为reg(寄存器)型变量,在always块或initial块中赋值(产生测试条件),被测元器件的输出端定义为wire(线网)型变量,产生相应输入变化的输出结果(波形)。

4.1

组合逻辑电路Test Bench的设计

组合逻辑的设计验证,主要就是检查设计结果是不是符合该电路的真值表功能,因此在编写组合逻辑Test Bench时,用initial块把被测电路的输入按照真值表提供的数据变化作为测试条件,就能实现Test Bench的设计。

例1.编写一位全加器的Test Bench程序

全加器的A和B两个是1位二进制加数的输入端,CI是低位来的进位输入端,CO是向高位进位的输出端,SO是全加器的本位和值。

用Verilog HDL语言编写的全加器程序adder.v如下:

moduleadder1(

a ,

b ,

ci ,

so ,

co

);

// Portdeclarations

input a ;

input b ;

input ci;

output so;

output co;

//InternalVariables

wire a;

wire b;

wire ci;

wire so;

wire co;

//CodeStarts Here

assign {co, so} = a + b + ci;

endmodule

根据全加器的真值表写的全加器的Test Bench程序test_adder1.v如下:

//test_adder1.v

`timescale1ns/1ns

moduletest_adder1;

wire so;

wire co;

reg a;

reg b;

reg ci ;

adder1 U(

.a(a),

.b(b),

.ci(ci),

.so(so),

.co(co)

);

initial

begin

#20 a = 0; b = 0; c = 0;

#20 a = 0; b = 0; c = 1;

#20 a = 0; b = 1; c = 0;

#20 a = 0; b = 1; c = 1;

#20 a = 1; b = 0; c = 0;

#20 a = 1; b = 0; c = 1;

#20 a = 1; b = 1; c = 0;

#20 a = 1; b = 1; c = 1;

#200 $stop;

end

endmodule

下面我们就以ModelSim为EDA平台,仿真上面的程序。这一讲先暂时不讲仿真测试的方法,留到下一讲再来详述,这一讲主要讲述的内容是Test Bench程序的编写方法,故现在仅仅给出仿真的波形图,全加器的仿真波形如图3所示:

图3一位全加器的仿真波形图

现在对着这个图,我们返回来再来看看我们编写的test_adder1.v这个Test Bench程序究竟完成了哪些工作,是不是按照我们的要求来工作的:

01

首先看程序第二行的`timescale1ns/1ns这句代码,这个是时间尺度指令,它是用来定义模块的仿真时间单位和时间精度的,其使用格式为:`timescale仿真时间单位/时间精度,用于说明仿真时间单位和时间精度的数字只能是1、10或100,不能为其它的数字,单位可以是s、ms、us、ns、ps和fs。仿真时间单位是指的模块仿真时间和延时的基准单位,也就是说只有定义了仿真时间单位,程序中的延时符号"#"才有意义,如程序中的一行#20 a = 0; b = 0; c = 0;前面的#20就是延时20个时间基准单位,按照程序中的1ns这个基准,就延时了20个ns。需要说明的是该行程序的下一行#20 a =0; b = 0; c = 1;前面的延时20个ns是相对于前一个的延时来说的,也就是第二行在第一行完了之后延时20ns执行。这时候再看看仿真的波形图就不难理解最开始的线为什么是红色而不是正常的绿色的原因了,因为我们在程序中begin的下一行就是#20 a =0; b = 0; c = 0;它前面的延时20个ns是相对于begin的延时,也就是说程序开始的时候是什么都不做的,输出为不确定的值,过了20个ns才将全0赋给了a、b和ci,这个时候才是最开始的绿线的部分。

02

在Test Bench程序中,把全加器的输入a、b和ci定义为了reg型变量,把输出so和co定义为了wire型变量,这个和被测元件的定义情况刚好是反的,这样也说明了TestBench程序和被测元件是封闭的一个循环。用元件例化语句adder1U( .a(a), .b(b), .ci(ci), .so(so), .co(co) ) ;把全加器设计电路嵌入到Test Bench程序中。

03

程序的后面有一句#200 $stop;这个是一个系统任务,用来暂停仿真过程的,将控制权交还给用户,用户在取得控制权以后可以输入其它的控制命令或者查看仿真结果等,之后可以从暂停的地方恢复仿真过程。$stop有两种表达形式,带参数的和不带参数的:

$stop;

$stop(n); //n可以取0、1或2

不带参数的$stop等同于$stop(0),在暂停时不输出任何信息;$stop(1)在暂停时输出当前仿真时刻和暂停处在程序中的位置;$stop(2)不仅有$stop(1)的作用,还能输出仿真时占用内存大小和CPU时间。

而用于退出仿真过程的系统任务是$finish,我们在点击Run(开始运行)的时候,系统会询问我们是否要结束仿真,假如我们选"是",这个系统任务会把ModelSim软件在完成仿真后关闭,假如我们选"否",则可以继续留在仿真界面。

和一位全加器的真值表进行全部的对比后发现和该仿真波形完全一致,仿真结束。

4.2

时序逻辑电路Test Bench的设计

时序逻辑电路Test Bench的设计要求和组合逻辑电路基本相同,主要区别在于时序逻辑电路Test Bench软件中,需要用always块语句生成时钟信号。

例2所编写的程序,就是在下一讲当中的实例,利用这个实例来讲解软件的全部操作流程和使用方法,这一讲先来分析这个程序以及和它相配套的Test Bench程序,看看它们是否能够按照我们设计期望的那样输出仿真结果。

例2.编写8位加法器的Test Bench程序

第一个文件,源程序:

modulecounter8(

clk ,

aclr ,

load,

load_din ,

dout

);

// Portdeclarations

input clk;

input aclr;

input load;

input [7:0] load_din;

output [7:0] dout;

//InternalVariables

wire clk;

wire aclr;

wire load;

wire [7:0] load_din;

wire [7:0] dout;

reg [7:0] counter = 0 ;

//CodeStarts Here

always @(posedge clk or negedge aclr)

if(!aclr)

counter <= 0;

else if(load == 1)

counter <= load_din;

else

counter <= counter + 1;

assigndout = counter;

endmodule

第二个文件,Test Bench仿真测试程序:

`timescale1ns/1ns //注意最前面的符号是数字键"1"左边的那个符号,不是单引号

//test_counter8.v

`timescale1ns/1ns //注意最前面的符号是数字键"1"左边的那个符号,不是单引号

moduletest_counter8;

reg clk;

reg aclr;

reg load;

reg [7:0] load_din;

wire [7:0] dout;

initial

begin

clk = 0;

aclr = 1;

load = 0;

load_din = 0;

#120 aclr = 0;

#40 aclr = 1;

#20 load = 1;

load_din = 100;

#20 load = 0;

#100 $stop;

end

always#10 clk = ~clk;

counter8U(

.clk(clk),

.aclr(aclr),

.load(load),

.load_din(load_din),

.dout(dout)

);

endmodule

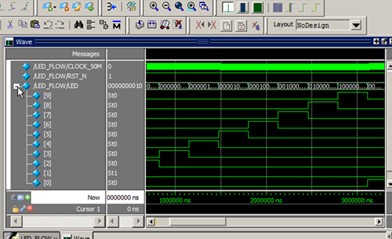

图4 八位加法器仿真波形图

现在就对着这个图,来看看我们编写的test_counter8.v文件是不是按照我们的设计要求的那样来工作的:

01

和组合逻辑的设计一样,我们要在test_counter8 .v中例化被测元件counter8,把八位加法器元件嵌入到test_counter8.v这个Test Bench中来。

02

和组合逻辑不同的是,我们要利用always #10 clk = ~clk;这个语句来产生周期为20个时间基准单位(1ns)的时钟(方波),即就是20ns的时钟信号。注意:时钟只能用always块才能生成,但要在initial块中赋给时钟的初始值(如clk=0或clk=1),如果不设置时钟初始值,则在仿真的时钟输出端是一个未知x(不变,就是例1中的那段红线了)。

03

在initial块中生成复位信号和加载信号,注意:一定要给复位信号和加载信号赋给初始值,否则和不设置时钟初始值一样会出现问题的。

04

在initial块的begin语句一开始就设置相关的初始值是一个好习惯。

和test_counter8.v进行全部的对比后发现和该仿真波形完全一致,仿真结束。

至此,第一讲全部内容结束,主要是讲了Test Bench程序的编写方法,下一讲我们将介绍ModelSim软件的使用方法。

-

FPGA

+关注

关注

1629文章

21729浏览量

602969 -

仿真器

+关注

关注

14文章

1017浏览量

83720 -

PCB设计

+关注

关注

394文章

4683浏览量

85539 -

ModelSim

+关注

关注

5文章

174浏览量

47162 -

可制造性设计

+关注

关注

10文章

2065浏览量

15529 -

华秋DFM

+关注

关注

20文章

3494浏览量

4455

原文标题:ModelSim仿真软件介绍(一)

文章出处:【微信号:gh_873435264fd4,微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA开发:modelsim仿真流程及波形

ModelSim,synplify,ISE后仿真流程

Altera ModelSim 6.5仿真入门教程

使用 ModelSim 进行设计仿真详解

Modelsim软件如何仿真,怎么能添加输入信号?

modelsim仿真详细过程(功能仿真与时序仿真)

Modelsim仿真教程Modelsim的基础入门基础教程免费下载

仿真软件ModelSim及其应用,ModelSim的仿真流程

仿真软件ModelSim及其应用,ModelSim的仿真流程

评论