碳化硅(SiC)MOSFET的优异技术功能必须搭配适合的成本定位、系统相容性功能、近似于硅的FIT率以及量产能力,才足以成为主流产品。电力系统制造商需在实际商业条件下符合所有上述多项要素,以开创功率转换的新局面,尤其是以能源效率以及「以更少投入获得更多产出」为目标的案例。

在未来,将有越来越多的功率电子应用无法仅倚赖硅(Si)装置满足目标需求。由于硅装置的高动态损耗,因此藉由硅装置提高功率密度、减少电路板空间、降低元件数量及系统成本,同时提高功率转换效能,即成为一个相互矛盾的挑战。为解决此问题,工程师们逐渐开始采用以碳化硅材料为基础的功率半导体来部署解决方案。

在这十多年来,诸如太阳能变频器中的MPP追踪或开关式电源供应器中的功率因数校正等应用中,使用Si IGBT加上SiC二极体或具有SiC二极体的超接面Si MOSFET已成为最先进的解决方案,可实现高转换效率及高可靠度的系统。市场报告甚至强调SiC二极体正进入生产率的平原期。SiC技术中的量产技术、生产品质监控以及具有优异FIT率的现场追踪记录,为采用包含SiC MOSFET之产品策略奠定了下一步基础。

SiC MOSFET/Si IGBT效能大有优势

SiC半导体材料中的晶体管功能,为整体电力供应链(从能源产生、传输及分配给消费者)的能源效率(以较少能源获得更多能源)提供了更大的潜力。

让我们仔细研究一下SiC MOSFET与Si IGBT的效能优势。图1显示了先进的硅解决方案范例:如果目标为高效率与高功率密度,具有650V与1200V Si IGBT的3-Level T类拓扑的一个相位脚通常会用于三相系统,例如光电变频器与UPS。采用此种解决方案,效率最高可达到20~25kHz的切换频率。由于装置电容较低、部分负载导通损耗较低,以及没有关断尾电流,因此1200V SiC MOSFET的电流损耗比1200V Si IGBT低约80%。在外部切换位置使用1200V SiC MOSFET可大幅提升效率,并在指定的框架尺寸中达到更高的输出功率。

图1 先进的硅解决方案范例

进一步提高切换频率会导致硅基解决方案效率与最大输出功率迅速降低,但SiC MOSFET的低切换损耗不会有此问题。透过此范例的证明,工作频率高达72kHz的三倍仍带来比24kHz运作之硅解决方案更高的效率。因此可缩减被动元件实体尺寸、减少冷却作业,并达到更低的系统重量与成本。

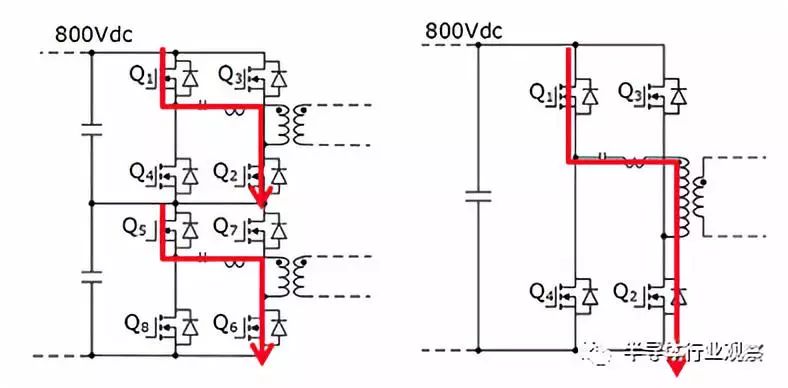

另一个三相电力转换范例是电动车的充电基础设施。1200V SiC MOSFET可为DC-DC转换级建构一个LLC全桥级,其中典型的硅解决方案倚赖650V Si超接面MOSFET,需要两个串联的LLC全桥来支援800V的DC链路。而四组SiC MOSFET加上驱动器IC即可取代八组Si超接面MOSFET加上驱动器IC,如图2所示。除了零件数量减少及电路板空间缩减之外,还可以使效率达到最佳化。在每个导通状态下,相较于Si解决方案中的四个切换位置,SiC MOSFET解决方案仅打开两个切换位置。在快速电池充电中使用SiC MOSFET,可实现高效率的充电周期。

图2 四组SiC MOSFET加上驱动器IC即可取代八组Si超接面MOSFET加上驱动器IC

由于动态损耗比1200V Si级低一个量级,因此SiC MOSFET亦可藉由提高效能,为传统的简单拓扑提供重新使用的机会。在图3中,将使用1200V SiC MOSFET的传统2-Level解决方案与先前提及的先进3-Level硅解决方案进行比较。2-Level拓扑结构的优点是控制方案非常简单,且减少50%的零件数量。此种解决方案可用于光电与UPS变频器,以及驱动系统、电池充电及能源储存解决方案中具有双向性的主动式前端。如图3所示,尽管切换频率从24kHz提高至48kHz,但在2-Level SiC MOSFET解决方案的高负载条件下,效率提高了0.3~0.4%,这的确令人惊奇,因为其切换电压较3 -Level运作高出两倍(800V比400V)。

图3 使用1200V SiC MOSFET的传统2-Level解决方案与先进3-Level硅解决方案比较

然而,以SiC MOSFET进行设计也存在着挑战。设计人员必须考量SiC MOSFET的切换瞬变。相较于经常可在1200V Si IGBT中见到的5~20V/ns,50V/ns或更高的dv/dt并不罕见。因此,电路板层级上的寄生耦合电容将导致过多的能源损耗。对于以更简单的2-Level解决方案取代3-Level Si IGBT解决方案的情况而言,如果切换电压与频率皆加倍,则寄生耦合电容将产生高出八倍的能源损耗。图3显示当SiC MOSFET在标准IGBT 2-Level解决方案中随插即用时的原始效率线,而下一个效率线则显示有关汲极-源极寄生电路板电容的PCB谨慎设计能如何减少损耗。当切换频率增加时,应考量的第二个主题涉及电感器的磁芯损耗。

由于涟波电流及其相应的损耗在整个负载范围内维持恒定,藉由改变芯材料来改善磁芯损耗主要会影响部分负载效率。相较于3-Level Si IGBT解决方案,这两项改善最终将带来高于98.5%的理想效率线。这显示SiC MOSFET主要并非Si IGBT的随插即用选项,而且需要大量的设计作业才能将效能提升到更高水准。

硅主流技术影响SiC可靠性/稳固性

目前为止,SiC MOSFET需要比Si IGBT或Si MOSFET更高的闸极驱动电压,而且经常面临极为接近零伏特的低闸极-源极临界值电压裕度。此微小的裕度使得闸极电压振铃尖峰处于高dv/dt旋转率,成为系统设计人员关注的问题。新型沟槽技术实现了标准化闸极驱动方案,使+15V的Si IGBT足以导通,而4V基准临界值电压可在电流关断时提供稳固的讯噪比。

SiC MOSFET还需要匹配的驱动器IC才能释放其所有潜力。这些驱动器必须处理高达50V/ns或更高的dv/dt以及高切换频率,对时序与公差带来了更严格的要求。SiC MOSFET也可能需要负闸极电压,特别是用于硬切换拓扑或米勒钳制时。因此,如英飞凌的EiceDRIVER IC便适合驱动SiC MOSFET,且可根据应用需求提供各种功能,包含紧密的传播延迟匹配、精确的输入滤波器、宽输出侧供电范围、负闸极电压功能或米勒钳制,以及扩展的CMTI功能。

SiC的可靠性与稳固性保证与硅主流技术密切相关。SiC是大功率的半导体,但是以此种材料设计MOSFET涉及各种技术挑战,包括调整效能参数以达到可靠性与稳固性。

设计平面SiC MOSFET时,必须在区域特定导通电阻与闸极氧化物可靠性之间取得主要的平衡,亦即「芯片成本与效能以及可靠性之间的权衡」。

平面SiC-SiO2介面上的缺陷密度在4H-SiC中非常高,这导致MOSFET通道中的电子散射,并因此降低电子通道移动率。效能降低会导致通道电阻增加,以及导通状态下功率损耗增加。只有透过在氧化物上施加过大的电场加以导通,或透过更高的闸极-源极电压或更薄的SiO2层,区域特定的导通电阻才能够保持在优良的低水准程度。

对于SiC材料中的沟槽MOSFET装置结构而言,由于垂直晶格平面中的SiO2介面具有远低于平面介面的缺陷密度,因此毋须过度驱动氧化物。然而,由于SiC材料中的高电场,沟槽结构对于沟槽转角处的阻隔模式而言是更大的挑战。实现适当场衰减的设计措施比平面结构更为复杂。

采用比例提升SiC成本不再高不可攀

在广泛采用SiC MOSFET之前,客户需确保合作的供应商能够稳定提供优质产品,且在需求增加时仍能维持水准。电源芯片商为此所建立的生产流程具有高容量及高灵活性,经验证可制造Si与SiC芯片,并组装成独立封装或电源模组。多项先进的功率装置技术先前皆已成功获得提升,例如CoolMOS、TRENCHSTOP IGBT及CoolSiC萧特基二极体;也致力于透过市场推广与增加产量推动CoolSiC MOSFET产品发展。

过去以来,SiC装置价格较硅装置高,是阻碍市场广泛采用SiC装置的因素之一。由于SiC与硅装置在原始晶圆制程中存有根本上的差异,因此SiC装置仍较为昂贵,而且在可预见的未来不会达到同等的成本。多年来由于采用比例提升、规模经济、新的区域有效芯片设计,以及生产更大的晶圆直径,SiC二极体价格已经下降。目前市场上SiC装置价格的下降及供货的增加,使得电源设计厂商面临提高电源转换效能并降低系统成本的压力,其需求也因此有所变更。

-

MOSFET

+关注

关注

143文章

7069浏览量

212566 -

功率器件

+关注

关注

41文章

1721浏览量

90280 -

SiC

+关注

关注

29文章

2747浏览量

62394

原文标题:SiC MOSFET进入主流市场,功率器件新局面正式开启

文章出处:【微信号:iawbs2016,微信公众号:宽禁带半导体技术创新联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SiC MOSFET进入主流市场,功率器件新局面正式开启

SiC MOSFET进入主流市场,功率器件新局面正式开启

评论