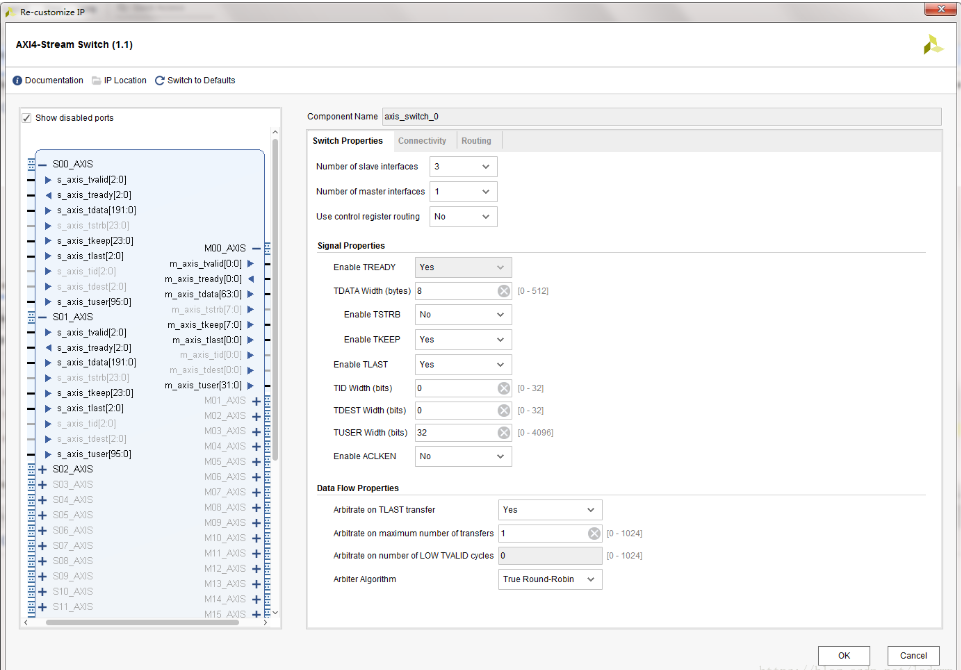

第一点是IP的生成,官方的IP显示应该是有BUG,我的使用需求是3从1主做仲裁,然后在IP显示图中显示了三组AXIs从接口,但是每个从接口是主接口的位宽的3倍,当时看到这个一度觉得很奇怪,IP的手册也没有说明接口的使用方法,后来看例化模板发现只有一组AXIS从接口,位宽是主接口的3倍,刚好符合我的实际设置情况。

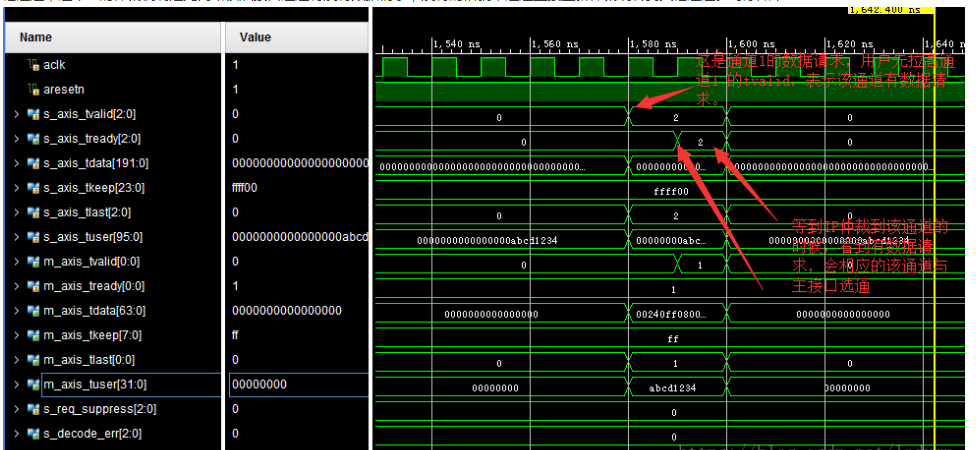

第二点是关于里面仲裁机制的细节,就是无论选择什么仲裁方式,对于接入这个AXIS从接口的信号,从接口的S_TVALID一定要提前于S_TREADY拉高,这个是什么意思呢,意思是说,用户接入从接口的逻辑,不能等到S_TREADY拉高,才把S_TVALID的握手机制,必须先让S_TVALID拉高告诉IP这个从接口有数据请求,当IP刚好仲裁到该从接口的时候,才会拉高S_TREADY接通到M_TREADY,所以某个从接口有数据请求的话不提前拉高S_TVALID的话,对应从接口的S_TREADY将不会选通连接到M_TREADY。由此可以推断,该IP的仲裁切换,是根据该从接口通道有没有数据请求来决定是否选通主接口与该从接口通道。这个和我平时写的类似于DDR多通道读写的仲裁机制有所不同,我之前是先选通该通道,然后判断该通道有没有数据请求,没有则重新仲裁跳转到其他通道,这个IP的仲裁机制是先判断该从接口通道有没有数据请求,没有的话就不选通直接重新仲裁跳转到其他通道。

序如下:

第三点是suppress信号,是抑制某个通道与主接口通道选通的控制位,如果置1,对应的从接口将会不与主接口通道选通。

以上的一些使用说明是基于3从1主的总线总裁使用心得,其他情况读者请自行分析。

-

Switch

+关注

关注

1文章

529浏览量

57737 -

Stream

+关注

关注

0文章

20浏览量

7932

发布评论请先 登录

相关推荐

是否可以使用AXI4流以某种方式从收发器中提取输入数据

如何吧AXI4-stream时钟转换器tkeep设置为null?

axi4-stream combiner问题的解决办法?

AXI-stream数据传输过程

看看在SpinalHDL中AXI4总线互联IP的设计

ARM CoreLink AXI4至AHB Lite XHB-400桥接技术参考手册

SoC Designer AXI4协议包的用户指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流协议断言用户指南

一文详解ZYNQ中的DMA与AXI4总线

ZYNQ中DMA与AXI4总线

AXI-Stream代码

关于AXI4-Stream协议总结分享

AXI4 、 AXI4-Lite 、AXI4-Stream接口

使用AXI4总线实现视频输入输出

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

基于3从1主的AXI4 Stream Switch使用

基于3从1主的AXI4 Stream Switch使用

评论