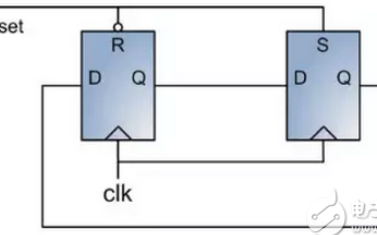

IC设计中同步复位与异步复位有什么区别?

异步复位是不受时钟影响的,在一个芯片系统初始化(或者说上电)的时候需要这么一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。而同步复位需要在时钟沿来临的时候才会对整个系统进行复位。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

IC设计

+关注

关注

38文章

1406浏览量

108476 -

同步复位

+关注

关注

0文章

28浏览量

10990 -

异步复位

+关注

关注

0文章

48浏览量

13713

原文标题:【M博士问答】IC设计中同步复位与异步复位有什么区别?

文章出处:【微信号:Mouser-Community,微信公众号:贸泽电子设计圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步

发表于 06-21 09:59

•2447次阅读

Xilinx FPGA的同步复位和异步复位

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和

发表于 07-13 09:31

•7759次阅读

FPGA同步复位和异步复位

FPGA(Field-Programmable Gate Array,现场可编程门阵列)中的复位操作是设计过程中不可或缺的一环,它负责将电路恢复到初始状态,以确保系统的正确启动和稳定运行。在FPGA设计

解析IC设计中同步复位与异步复位的差异

解析IC设计中同步复位与异步复位的差异

评论