1.引言

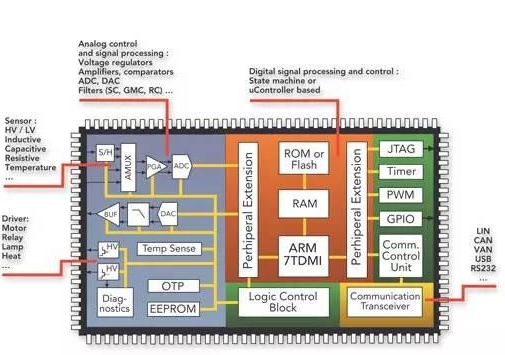

集成电路相关技术作为最具发展前景的技术,已经成为世界最具发展前景的高科技技术,一个国家的集成电路发展水平最能衡量整体的科技水平,目前受到国家的高度重视,特别是关于集成电路的芯片研发领域。

近年来,国内越来越多的科研机构、高校院所、IC企业研发部门等逐步关注和从事集成电路的电磁兼容性(IC EMC)研究。

目前关于IC EMC的相关研究国外起步较早,发展较快,已经形成比较完善的理论体系以及先进的测试研究设备,像欧洲的法国、德国、美国等,亚洲的韩国、日本,新加坡。

国内的相关的IC EMC研究目前集中于高校院所,如国防科技大学、浙江大学、解放军信息工程大学、中科院微电子所等,近年来也取得了重要成果。

2. 电磁敏感度

电磁兼容性分为电磁干扰(EMI)和电磁敏感度(EMS)。简单的说,EMI指的是待测设备影响其它设备正常工作产生的电磁辐射,EMS指的是设备抵御外界电磁辐射干扰的能力。

目前关于电磁敏感度测试分为多个项目,如传导、辐射、静电放电、电快速脉冲群、浪涌等。本文介绍其中两种测试方法。

3. 电磁敏感度测试方法

3.1传导抗扰度

传导抗扰度测试主要分为直接功率注入法、大电流注入法。这里介绍直接功率注入法。

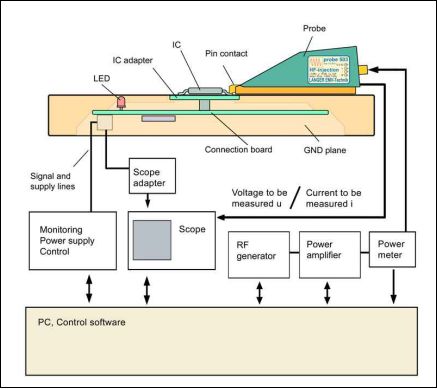

直接功率注入法,通过干扰源产生干扰脉冲,经过功放、定向耦合器、注入网络,进而注入测试设备。通过失效判据来判断设备的功能状态,确定注入电压的大小,测试框图如图1所示,图2为实际设备的配置,具体配置参考IEC 62132。

图1 测试框图

图2 测试设备

测试过程中,需要注意尽量按照测试标准进行测试,另外,相关测试板的设计要充分考虑接地设置。

3.2 静电放电

静电放电测试是设备抗扰度测试的重要项目,目前关于ESD的研究,国内起步较早,取得了不错的研究成果。但是ESD相关测试设备过于昂贵, 一般小型研究机构无法从事进一步研究,其研究成果大多集中于测试设备完备的大型科研机构。

目前国际上有关于ESD测试的通用标准IEC 61000,规定了ESD脉冲的幅值和上升时间,如图3所示,图4为标准的ESD发生器模型。

图3 ESD脉冲波形

图4 ESD发生器模型

ESD测试方法简单,只需把测试探头压上测试引脚注入脉冲波形即可,在测试过程中,测试人员要全程穿戴接地手环,防止人体自身静电造成干扰。

-

集成电路

+关注

关注

5390文章

11579浏览量

362447 -

电磁兼容

+关注

关注

54文章

1883浏览量

97922

原文标题:两种集成电路电磁敏感度测试方法介绍

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

集成电路的电磁兼容测试概述

电磁兼容性分析的方法

混合集成电路的电磁兼容设计

交流稳压电源的电磁兼容要求与测试方法详细介绍

集成电路电磁兼容性设计应遵循的原则和方法

汽车设计中的电磁兼容性和集成电路IC问题解决方案

如何设计混合集成电路的电磁兼容

介绍集成电路电磁兼容测试的两种方法

介绍集成电路电磁兼容测试的两种方法

评论