美国国防高级研究计划局(DARPA)于2017年6月1日宣布推出电子复兴计划(Electronics Resurgence Initiative,简称ERI)。计划未来五年投入超过 20亿美元,联合国防工业基地、学术界、国家实验室和其他创新温床,开启下一次电子革命。这是美国在电子领域花重金打造的又一具有国家战略的科研计划,本文将总体概要性的解读电子复兴计划诞生的背景与意义,电子复兴计划的3大研究领域及6大研究方向。之后的系列文章将针对3大研究领域:材料与集成、系统架构、设计分专题进行研究与探讨。

一、DARPA电子复兴计划诞生的背景与意义

DARPA成立于1958年,也正是Kilby提出集成电路的那一年,很多硅时代的进步,包括半导体材料的基本进步,大规模集成和精密制造,也都是在DARPA的支持和推动下得以实现。但是,与大多数发展道路一样,缩放(也即将更多的晶体管放在同一个芯片上)也终将迎来终点。以摩尔定律为代表的电子小型化道路,将逐步触到物理学和经济学的极限。随着这个转折点的临近,微电子技术的发展将需要一个新的创新阶段,从而继续保持电子创新的现代奇迹。

过去70年来,美国因其在电子和半导体领域的领先地位,享受到了经济、政治和国家安全上的优势。如今,在摩尔定律走向终结,电子领域急需转变突破的关键点,在人工智能和量子等新兴技术及产业涌现的当下,美国布局ERI计划是为了下一个十年乃至百年的领先,同时也是为国防部一些顶级技术重点领域,包括量子计算、人工智能、先进制造以及太空和生物技术,打下重要的基础。

ERI计划将专注于开发用于电子设备的新材料,开发将电子设备集成到复杂电路中的新体系结构,以及进行软硬件设计上的创新。ERI计划将补充DARPA去年创建的“联合大学微电子学计划”(Joint University Microelectronics Program,简称JUMP)。

二、ERI计划与JUMP计划形成互补

JUMP计划是DARPA和行业联盟半导体研究公司联合资助的最大的基础电子研究工作。预计在5年时间里投入1.5亿美金,联合了MIT、伯克利、加州大学体系里的美国众多一流高校和研究所,设置了6个不同的研究中心,探索6大不同的方向,是一个多学科跨领域的大规模长期合作计划,目标是大幅度提高各类商用和军用电子系统的性能、效率和能力(performance, efficiency, and capabilities)。

根据JUMP计划的公开资料,这些研究和开发工作应该“为美国国防部在先进的雷达、通信和武器系统方面提供无与伦比的技术优势,为军事和工业部门带来优势,并为美国的经济和未来的经济增长,提供独特的信息技术和对商业竞争力至关重要的处理能力”。

JUMP计划专注于中长期(8到12年)探索性研究,预期的国防和商业价值将在2025到2030年这个时间线实现。联盟致力于将资源集中在高风险、高收益、长期创新研究上面,加速电子技术和电路及子系统的生产力增长和性能提升,从而解决电子和系统技术中现有的和新出现的挑战。

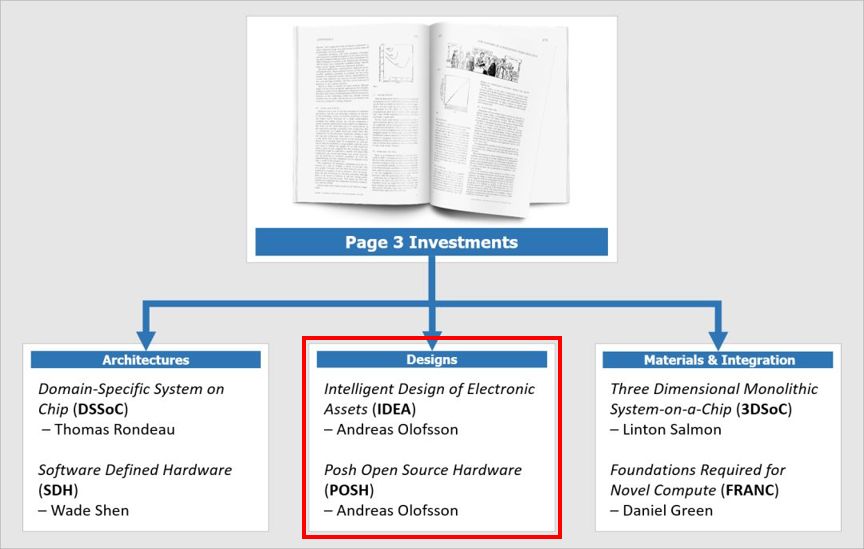

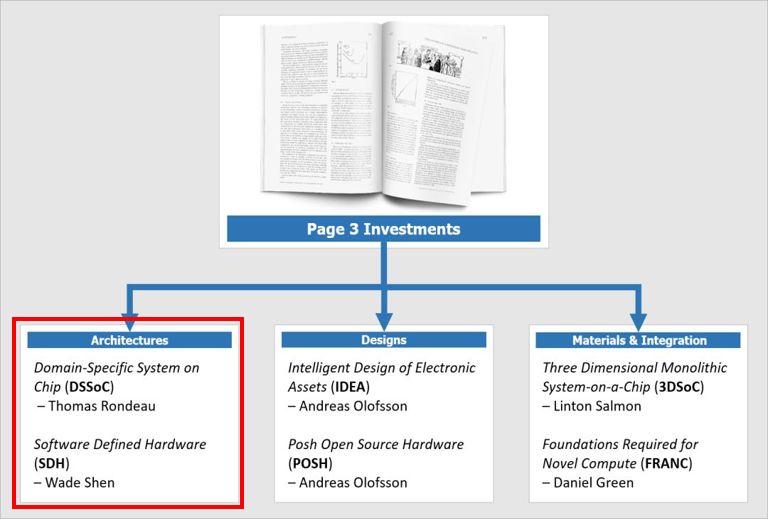

图1 2017年9月公布的ERI计划图

如果说JUMP是一个更侧重基础和研究探索的计划,那么ERI则更加实际一点,也更接近产业。ERI的三大关注重点:

开发用于电子设备的新材料(Materials and Integration):探索使用非常规电路元件而非更小的晶体管来大幅提高电路性能。硅是最常见的微系统材料,硅锗等化合物半导体也在特定应用中发挥了一定的作用,但这些材料的功能灵活性有限。ERI将表明,元素周期表为下一代逻辑和存储器组件提供了大量候选材料。研究将着眼于在单个芯片上集成不同的半导体材料,结合了处理和存储功能的“粘性逻辑”(sticky logic)设备,以及垂直而非平面集成微系统组件。

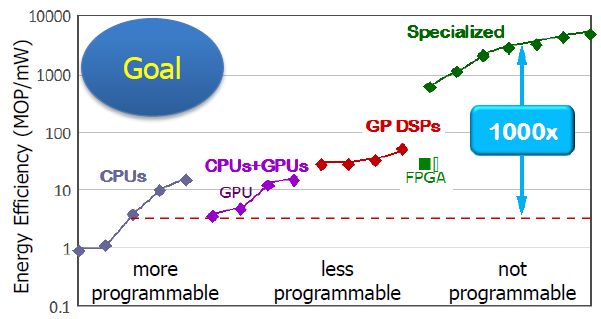

开发将电子设备集成到复杂电路中的新体系结构(Architectures):探索针对其执行的特定任务而优化的电路结构。GPU是机器学习持续进展的基础,GPU已经证明了从专用硬件体系结构中能够获得大幅的性能提升。ERI将探索其他机遇,例如能根据所支持的软件需求调整进行可重新配置的物理结构。

进行软硬件设计上的创新(Design):重点开发用于快速设计和实现专用电路的工具。与通用电路不同,专用电子设备可以更快、更节能。尽管DARPA一直投资于这些用于军事用途的专用集成电路(ASIC),但ASIC的开发可能会花费大量时间和费用。新的设计工具和开放源代码设计范例可能具有变革性,使创新者能够快速便宜地为各种商业应用创建专用电路。

三、DARPA“电子复兴计划”峰会宣布六大项目合作研究团队

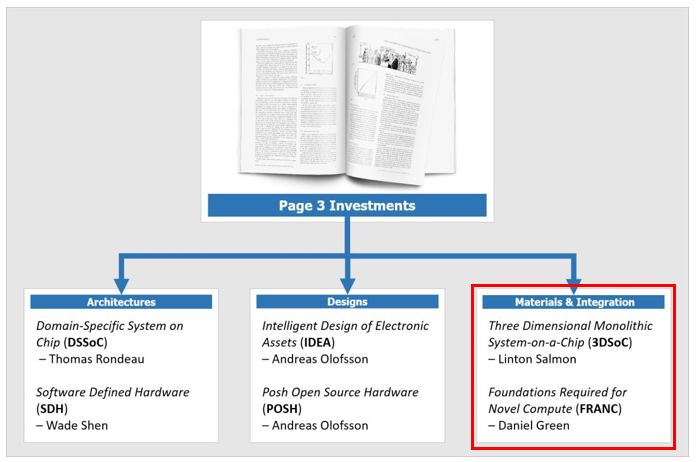

2018年7月23日,DARPA在加利福尼亚州旧金山举办的首届年度“电子复兴计划”(ERI)峰会开幕式上,宣布了ERI六大项目合作研究团队,旨在扶持和培养在材料与集成、电路设计和系统架构三方面的创新性研究。

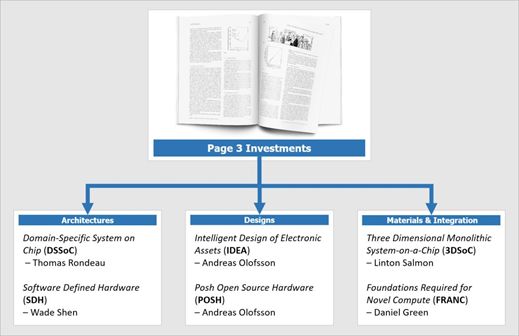

这六个项目旨在补充传统晶体管尺寸的不断缩小并确保持续改进电子性能(解决Moore在50年前即预测到将在当前半导体发展蓝图最后阶段出现的问题),分别为:

1.“三维单芯片系统”——3DSoC:Three Dimensional Monolithic System-on-a-Chip

2.“新式计算基础需求”——FRANC:Foundations Required for Novel Compute

3.“特定领域片上系统”——DSSoC:Domain-Specific System on a Chip

4.“软件定义硬件”——SDH:Software Defined Hardware

5.“高端开源硬件”——POSH:Posh Open Source Hardware

6.“电子设备智能设计”——IDEA:Intelligent Design of Electronic Assets

图2 ERI计划六大项目专注于系统架构、电路设计、材料与集成3大领域

1、材料与集成领域

(1)“三维单芯片系统”(3DSoC)项目

传统微电子芯片为平面、二维结构,3DSoC项目主要聚焦在单衬底第三维度垂直向上构建微系统所需材料、设计工具和制造技术的研发。通过该项目可实现逻辑、存储及输入/输出元件的高效封装,从而使系统的运行功耗更低,计算速度提升50倍以上。

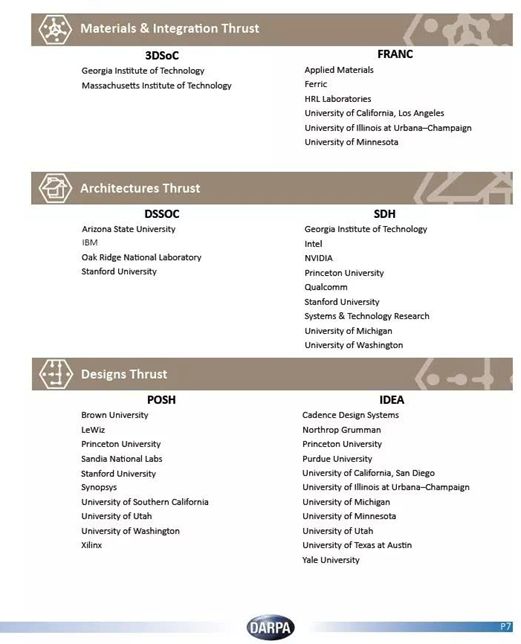

选定合作研究团队为Georgia Institute of Technology,Massachusetts Institute of Technology。

(2)“新式计算基础需求”(FRANC)项目

项目的目标是超越传统逻辑和存储功能相分离的冯诺依曼架构。当前,在冯诺依曼架构下,因数据在存储单元和处理器之间传输所造成的时间延迟和能量消耗成为阻碍计算机性能进一步提升的主要原因。针对该项目所提出的研究计划需要展示如何通过开发新型材料、器件及算法加速逻辑电路中的数据存储速度或通过设计全新的、比以往更为复杂的逻辑和存储电路结构来突破这一“存储瓶颈”。

选定合作研究团队为Applied Materials、Ferric、HRL Laboratories、University of California, Los Angeles、University of Illinois at Urbana–Champaign、University of Minnesota。

2、系统架构领域

(1)“特定领域片上系统”(DSSoC)项目

该项目的设立是受通过单一编程框架实现多应用系统快速开发需求的驱动。这一单一编程框架能够使片上系统设计人员将通用、专用(如专用集成电路)、硬件加速辅助处理、存储和输入/输出等要素进行混合和匹配,从而实现特定技术领域应用片上系统的简单编程。例如,软件定义无线电(software-defined radio)就是这些特定技术领域中的一种,应用范围包括移动通信、卫星通信、私人网络、所有类型雷达和网络空间电子战等。

选定合作研究团队为Arizona State University、IBM、Oak Ridge National Laboratory、Stanford University。

(2)“软件定义硬件”(SDH)项目

该项目旨在构建可重构软硬件设计和制造的决策辅助技术基础。这些可重构软硬件需要具备运行数据密集型算法的能力(具备该能力是实现未来机器学习和自主系统的基础)和与目前专用集成电路(ASICs)相当的性能。在现代战争中,决策是由所获取的数据信息来驱动的,例如,由成千上万个传感器提供的情报、监视和侦察(ISR)数据、后勤物流/供应链数据和人员绩效评估指标数据等。对这些数据的有效利用依赖于可进行大规模计算的有效算法。

选定合作研究团队为Georgia Institute of Technology、Intel、NVIDIA、Princeton University、Qualcomm、Stanford University、Systems & Technology Research、University of Michigan、University of Washington。

3、电路设计领域

(1)“高端开源硬件”(POSH)项目

该项目旨在构建一个开源的设计和验证框架,包括以低成本实现超复杂片上系统设计的技术、方法和标准。DARPA“电子复兴”计划团队期望利用可降低复杂片上系统设计门槛的全新设计工具开启专用设计创新的新时代。开源软件最有可能成为在应用层面实现创新的工具。

选定合作研究团队为Brown University、LeWiz、Princeton University、Sandia National Labs、Stanford University、Synopsys、University of Southern California、University of Utah、University of Washington、Xilinx。

(2)“电子设备智能设计”(IDEA)项目

该项目将开发创建电子硬件自动化布局生成器所需的算法、方法、软件,使没有电子设计知识的用户能够在24小时内完成混合信号集成电路、系统级封装和印刷电路板等电子硬件的物理设计。

选定合作研究团队为Cadence Design Systems、Northrop Grumman、Princeton University、Purdue University、University of California, San Diego、University of Illinois at Urbana–Champaign、University of Michigan、University of Minnesota、University of Utah、University of Texas at Austin、Yale University。

图3 DARPA于2018年7月公布6大项目合作研究团队

2

近年来(2005年~2018年),美国国防高级研究计划局(DARPA)在集成电路的材料领域进行了多项研究,对材料的研究创新不仅仅局限于半导体器件材料的研究,而是更加强调了材料在集成电路集成中所发挥的应用。下面详细介绍DARPA最近推出的电子复兴计划(Electronics Resurgence Initiative,简称ERI)中与材料相关的研究内容。材料与集成领域的主要研究方向包括三维单芯片系统(3DSoC)和新式计算基础需求(FRANC)。

图1 ERI计划中材料与集成领域的研究内容

一、“三维单芯片系统”(3DSoC)项目

传统微电子芯片为平面、二维结构,3DSoC项目主要聚焦在单衬底第三维度垂直向上构建微系统所需材料、设计工具和制造技术的研发。通过该项目可实现逻辑、存储及输入/输出元件的高效封装,从而使系统的运行功耗更低,计算速度提升50倍以上。该项目材料的研究与系统集成密切相关,主要在于3DSoC芯片中不同逻辑和存储层的材料选取,以实现高性能的3DSoC芯片。

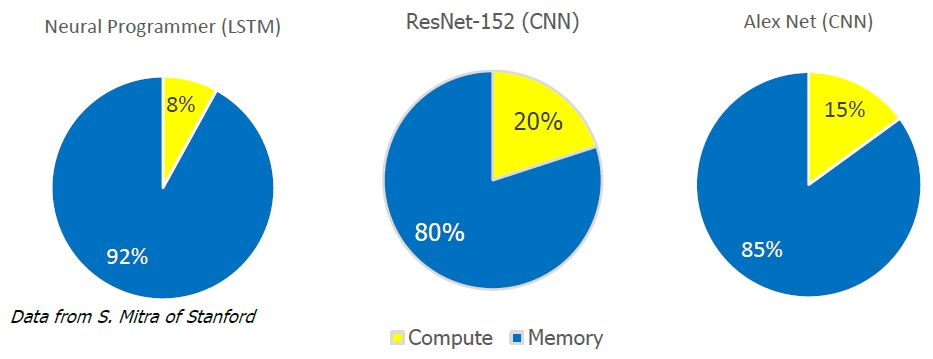

通过对基于7nm技术和不同算法的最新机器学习加速器的应用执行时间分析(如图2所示),虽然不同的机器学习算法从存储器中读写数据的时间略有不同,但是不管何种算法,存储器读写数据占用的时间均达到了80%以上,是限制计算速度的主要瓶颈。

图2 基于7nm技术和不同算法的最新机器学习加速器的应用执行时间分析

通过构建3DSoC芯片能缩短存储器和逻辑运算结构之间的物理距离,从而进一步减少存储器读写数据的时间,提高预算速度。作为3DSoC系统的一个成功举例,下图为Stanford大学S. Mitra 等人将3DSoC中的逻辑层和存储层制造在同一Die上的新型器件结构。

图3 Stanford大学S. Mitra团队研究的新型3DSoC解决方案

二、“新式计算基础需求”(FRANC)项目

项目的目标是超越传统逻辑和存储功能相分离的冯诺依曼架构。当前,在冯诺依曼架构下,因数据在存储单元和处理器之间传输所造成的时间延迟和能量消耗成为阻碍计算机性能进一步提升的主要原因。针对该项目所提出的研究计划需要展示如何通过开发新型材料、器件及算法加速逻辑电路中的数据存储速度或通过设计全新的、比以往更为复杂的逻辑和存储电路结构来突破这一“存储瓶颈”。

FRANC项目分为两大技术领域如下所示:

技术领域1(TA1)研究新的拓扑电路原型

子领域1:实现超越冯-诺伊曼拓扑的电路原型, 利用现有的材料和集成技术, 集成处理器和存储器来创建革命性的功能

子领域2: 允许利用新材料或集成技术,在冯-诺伊曼体系中集成非冯诺伊曼结构的加速器,加速器的性能优势可量化

技术领域2(TA2)研究新型计算的功能模组

开发支持超越冯-诺伊曼结构的组件或子系统,特别是开发新材料或集成技术,使未来的2.5D或3D集成解决方案能够在超越冯-诺伊曼计算拓扑的背景下实现,研究主题包括加速材料发现、非易失性存储器(NVM)、IC电源管理、芯片级光子组件。

图4 创新拓扑电路原型的两种方式

三维单芯片系统(3DSoC)和新式计算基础需求(FRANC)两大研究方向的目的都是问了解决存储器读写数据占用时间长这一限制计算速度的主要瓶颈,3DSoC是从3D垂直结构的角度出发,试图通过新材料与3D结构的融合实现这一目的。而FRANC项目用“新的材料和集成方案”创建“新颖的计算拓扑”,建议采取内存内计算、近内存计算等全新的拓扑机构来消除或减少数据移动的方式来加快处理数据的速度。通过这两个研究项目,我们可以发现DARPA强调材料在集成电路器件集成中发挥的作用,希望通过新材料结合新架构、新拓扑结构提高处理大数据的能力,为人工智能、超级计算等前沿领域的发展奠定基础。

3

上一章介绍了DARPA电子复兴计划(Electronics Resurgence Initiative,简称ERI)在材料与集成领域的布局和两个重点研究方向,本章介绍电子复兴计划中与电子电路设计相关的研究内容。电子电路设计领域的主要研究方向包括电子设备智能设计(IDEA)和高端开源硬件(POSH)。

图1 ERI计划中电子电路设计领域的研究内容

一、电子设备智能设计(IDEA)项目

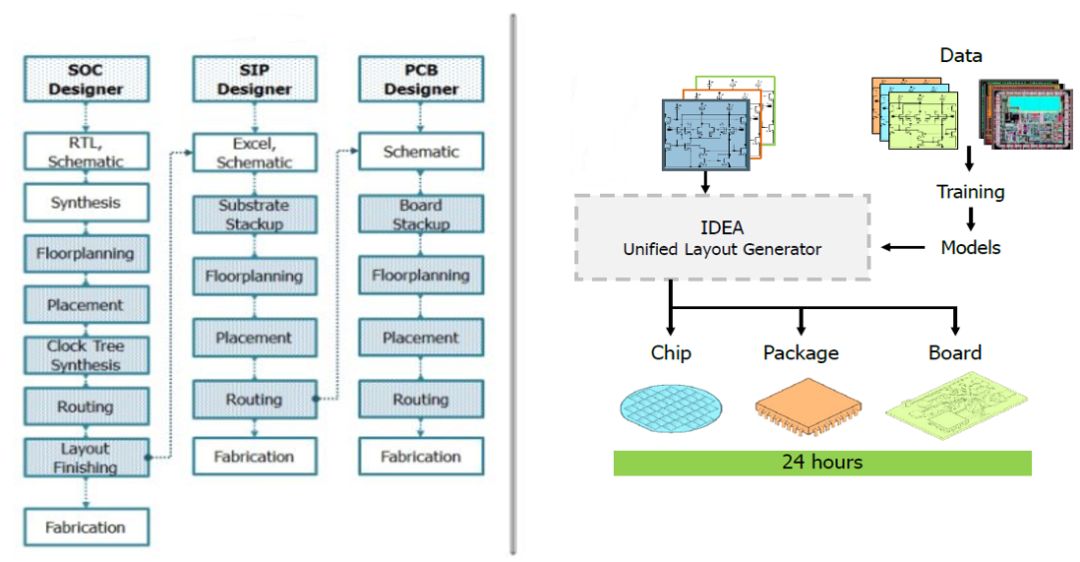

相比软件行业,芯片行业除了需要流片之外,还要解决两大关键问题,第一是版图设计,在电路设计完成之后需要通过版图设计生成GDS,第二是设计复用问题。IDEA项目就是针对第一大关键问题酝酿而生,目前数字电路的版图生成自动化程度已经相当高,但是模拟和混合信号电路仍然非常依赖手工去做版图。IDEA项目的研究目标是实现“设计过程中无人干预”的能力,在混合信号集成电路、多集成电路模块系统级封装和印刷电路板等复杂电子技术的24小时设计框架中也无需专家进行设计。

如下图所示,当今的SOC、SIP和PCB的设计流程在大部分环节都非常依赖于专业设计人员的知识输入,专业知识的载体是技术人员。IDEA项目的特点是通过收集大量的原始设计数据,通过人工智能和机器学习的方法训练得到模型,进而将模型导入一个统一的版图生成器中,通过版图生成器在24小时之内完成混合信号集成电路、多集成电路模块系统级封装和印刷电路板等的设计。IDEA的特点是专业知识的载体是软件,设计周期短,自动化程度高。

图2 当今SOC、SIP、PCB设计的流程(左)和IDEA项目的设计框架(右)

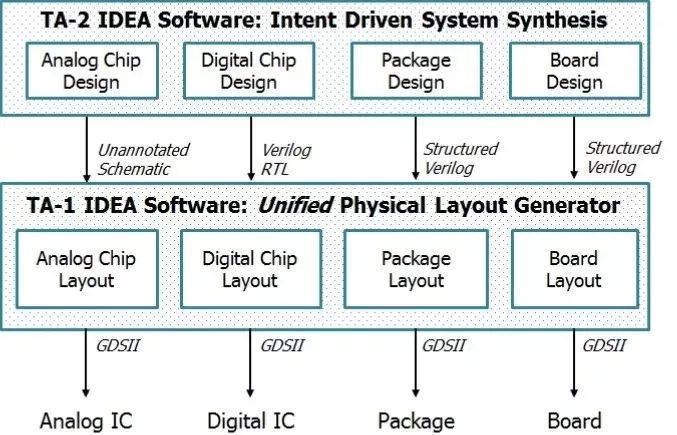

IDEA项目的两大技术领域分别是技术领域1(TA1):机器自动生成物理版图, 为模拟和数字SoCs, SiPs, PCBs开发一个统一的物理版图生成器和技术领域2(TA2):意图驱动的系统合成,开发一个意图驱动的、自动建构校正的系统生成器,如下图3所示。技术领域1的输入是用于模拟IC设计的netlist、用于数字IC设计的Verilog RTL、用于SiPs的结构化Verilog netlist和用于PCBs的结构化Verilog netlist,其输出是模拟电路、数字电路、多集成电路模块系统级封装和印刷电路板的版图设计。设计领域2则主要是根据系统的需求,基于一些组件模块,比如可用的封装、SiP用的die、SoC IP,生成设计网表,提供给技术领域1工具进行物理设计。

图3 IDEA项目的两大技术领域

二、高端开源硬件(POSH)项目

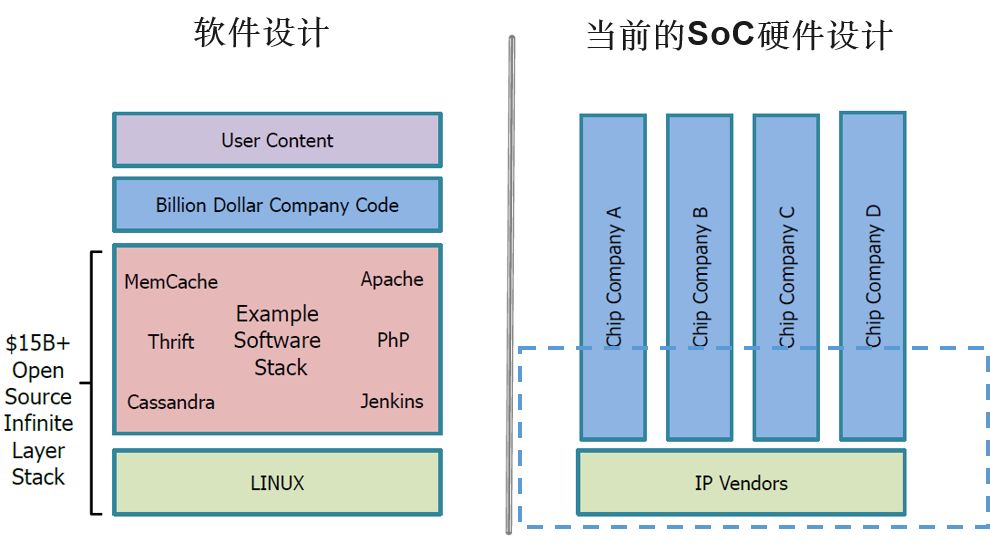

开源软件的蓬勃发展是目前软件开发可以快速、低成本实现的一个关键。从Linux,GNU,Android到现在各种开源的AI Framework,成功的开源项目往往能够产生革命性的影响。而在硬件设计难度和成本越来越高的情况下,“能否在硬件领域复制开源软件的成功”,自然成为一个值得考虑的问题。在这个背景下,DARPA的高端开源硬件(POSH)项目将提供开源设计和验证框架,包括技术、方法、标准,从而实现具有成本效益的超复杂片上系统设计。DARPA希望可降低复杂片上系统设计障碍的新工具能够打开一个特定应用设计创新的新时代。

图4 软件设计和硬件设计对比

如图4所示,目前软件设计中开源的部分很多,例如图中所提到的开源分布式NoSQL数据库系统Cassandra、开源的持续集成工具Jenkins、开源的软件框架Thrift、开源软件开发框架PhP等。对比软件的开源性,目前的SoC设计方法使IC设计开始进一步分工细化,出现了IP设计和SoC系统设计。对应于IP设计的IP Vendor的类型很多,主要包括了芯片设计公司、Foundry厂商、专业IP公司、EDA厂商等,其提供的IP核是芯片的核心组成部分,往往极具商业价值而非开源公开的。

在芯片设计项目中最重要的工作之一是验证工作,因为芯片不能失败(或者有缺陷)。如果芯片硬件有无法解决的bug,它带来的损失轻则是一次投片的费用打水漂,重则影响产品的上市时间或者公司的信誉,导致客户的流失,可能带来致命的打击。芯片项目和软件项目对Bug的容忍度有着根本的不同,基于此特点,POSH项目确立了三个主要技术目标:技术目标1(TA1):Hardware Assurance Technology指的是开发快速、有效、低成本的硬件验证方法对开源硬件进行有效质量验证;技术目标2(TA2):Open Source Hardware Technology指的是通过开发设计方法、标准、核心IP组件来创建一个可行的开源SoC生态系统;技术目标3(TA3):Open Source System-On-Chip Demonstration指的是通过设计一个最先进的开源SoC来验证开源硬件实施的可行性。

硬件开源是一个讨论了很久的话题,最近由于Nvidia开源DLA获得了更多关注。软件开源的成功能否能复制到硬件,既面临技术的挑战,又有生态和经济因素等诸多限制,挑战很大。但不管怎么说,能将自己的知识成果分享给大家,POSH、NVDLA和其它开源硬件项目能够开源就是非常有价值的事情。

4

上一章文章介绍了DARPA电子复兴计划(Electronics Resurgence Initiative,简称ERI)在电子电路设计领域的布局和两个重点研究方向,本章介绍电子复兴计划中与系统架构相关的研究内容。系统架构领域的主要研究方向包括特定领域片上系统(DSSoC)和软件定义硬件(SDH)。

图1 ERI计划中系统架构领域的研究内容

一、特定领域片上系统(DSSoC)项目

特定领域(Domain-Specific)的概念现在提的越来越多,大家也都逐渐看到它的重要性。现在的芯片项目越来越复杂,软件所占的比例非常高,投片、研发和应用的成本和风险越来越高。一套能把软硬件设计垂直整合起来的方法和工具,可以在不同但相似的应用间最大限度的实现重用,从而提高设计效率,降低成本。DSSoC项目的研究目标是将开发一种由通用处理器、专用处理器、硬件加速器、存储器、输入/输出元件等多个内核组成的异构片上系统,进而通过单个可编程器件实现多应用系统的快速开发。

如下图所示,当前许多高性能的专用芯片是以可编程性作为代价,特定芯片存在可编程弱和系统集成难度大的困难。如何设计一个系统架构,能够同时权衡专用性和通用性?特定领域计算的本质是建立一套完整的方法学和工具,能够高效的设计和实现面向一个领域的软硬件系统,同时这套方法和工具还可以方便的应用到新的领域。DSSoC项目提供一套垂直整合的方法,通过一个full-stack integration,提供一个软硬件框架,让程序员不必要了解底层硬件,但仍然可以充分的利用硬件的效率。目前,我们做一个架构设计的时候,往往要在通用性(可编程性)和专用性(高效率)之间做很多权衡。如果这个项目成功,那么在通用性和专用性之间的权衡就可以变得不那么困难了。

图2 当前芯片在可编程性和高性能方面的对比分析

如下图所示,DSSoC在软硬件垂直整合的方法体系中提出了5大关键技术:(1)Intelligent Scheduler:通过在系统中增加专用于调度的处理器,以及让每个Processor Elements (PE)都可以分析并上报自己的运行状态实现资源智能调度;(2)Software:软件工具包括开发工具,如编译器和调试器,算法库,以及Domain的应用程序和示例。软件工具是特定领域计算能否真正落地的最重要部分,一个基本要求是可以支持领域内的新的设计;(3)Domain ontology:描述Domain的特征,反映不同分组间的关系,对算法的细节特征进行描述,支持项目中的智能调度等工作;(4)Medium access control (MAC):MAC层是在PE间交换数据结构的媒介,既包括物理结构,拓扑,还包括一个标准编程接口;(5)Hardware integration:异构的SoC硬件, 包括CPU,GPU,TPU,Neuromorphic Unit,DSP,硬件加速器等。

图3 DSSoC项目提出的软硬件垂直整合方法

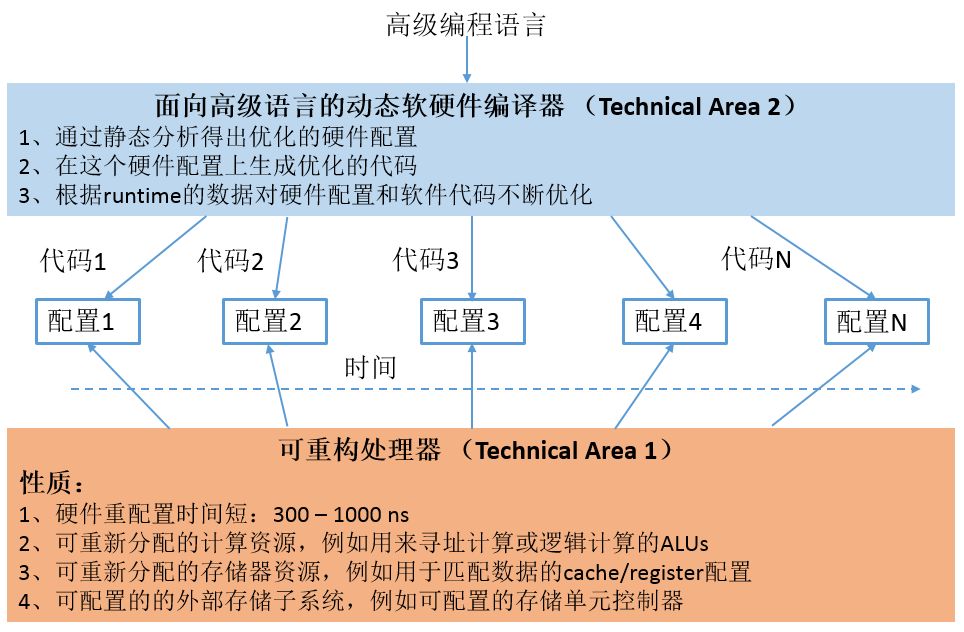

二、软件定义硬件(SDH)项目

软件定义硬件项目的研究目标是创建运行时可重新配置的硬件和软件,在不牺牲数据密集型算法的可编程性的情况下实现类似专用集成电路(ASIC)的性能,且没有专用集成电路开发相关的成本、开发时间或单个应用限制。在处理器设计过程中需要权衡的因素包括数学/逻辑资源、存储器、地址计算、数据读写和传送等,最优硬件配置根据算法不同而不同,没有一种硬件配置能有效解决所有的问题。现在虽然硬件设计水平已经达到专业化,但每个算法需要设计一个芯片,因此芯片设计成本高,往往也不具备可再编程性。通过SDH项目希望实现软硬件的Runtime优化,进而实现一个芯片实现多个应用,节约芯片设计成本,硬件通过高级语言实现可再编程性。

SDH程序将创建一个可扩展的硬件/软件架构,与ASIC不同,允许应用程序在运行时修改硬件配置。 SDH将实现两大目标:(1)输入数据变化时动态优化代码和硬件; (2)能够重用硬件来解决新问题,支持新算法。 为了实现这些目标,SDH把重点放在高速硬件重配置(very fast hardware reconfiguration speeds)和动态编译(dynamic compilation)。

SDH项目确立了两个主要技术目标:技术目标1(TA1)可重构处理器:可重构处理器要求重配置速度高于FPGA,而效率又要接近ASIC,功耗要远低于FPGA。而且这个处理器不仅要求片上的运算和存储可以重构,外部存储子系统也要求能够被配置为不同的数据访问模式;技术目标2(TA2)面向高级语言的动态软硬件编译器:在runtime时的优化同时包括了软件和硬件,编译器需要能够把高级语言转换为机器语言以及面向应用的硬件配置。

图4 SDH项目的两大技术领域

-

芯片

+关注

关注

454文章

50488浏览量

422242 -

集成电路

+关注

关注

5382文章

11409浏览量

361053 -

DARPA

+关注

关注

4文章

72浏览量

27819

原文标题:深入解读DARPA电子复兴计划

文章出处:【微信号:BIEIqbs,微信公众号:北京市电子科技情报研究所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DARPA电子复兴计划诞生的背景与意义

DARPA电子复兴计划诞生的背景与意义

评论