布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

直角走线

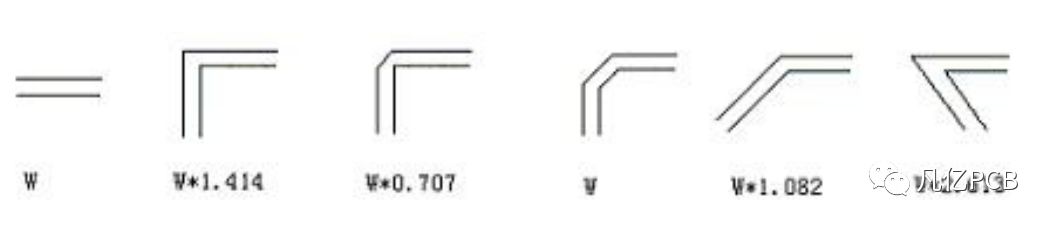

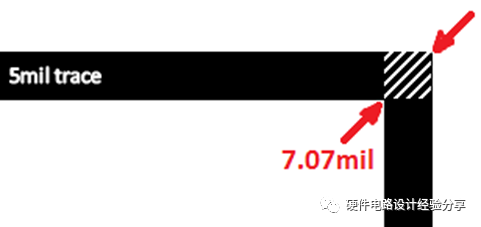

直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。

直角走线的对信号的影响就是主要体现在三个方面:

一是拐角可以等效为传输线上的容性负载,减缓上升时间;

二是阻抗不连续会造成信号的反射;

三是直角尖端产生的EMI。

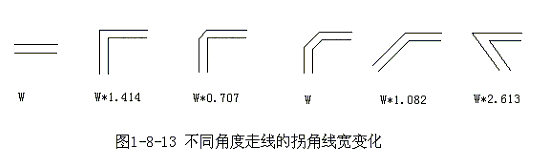

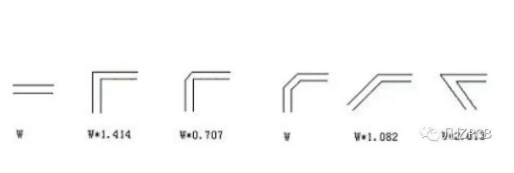

不同角度走线的拐角线宽变化

传输线的直角带来的寄生电容可以由下面这个经验公式来计算:

C=61W(Er)[size=1]1/2[/size]/ZO

在上式中,C就是指拐角的等效电容(单位:pF),W指走线的宽度(单位:inch),er指介质的介电常数,zo就是传输线的特征阻抗。举个例子,对于一个4Mils的50欧姆传输线(er为4.3)来说,一个直角带来的电容量大概为0.OlO1pF,进而可以估算由此引起的上升时间变化量:

T10-90%=2.2*C*ZO/2=2.2*0.0101*50/2=0.556ps

通过计算可以看出,直角走线带来的电容效应是极其微小的。

由于直角走线的线宽增加,该处的阻抗将减小,于是会产生一定的信号反射现象,我们可以根据传输线章节中提到的阻抗计算公式来算出线宽增加后的等效阻抗,然后根据经验公式计算反射系数:

p=(Zs-Z0)/(Zs+Z0)

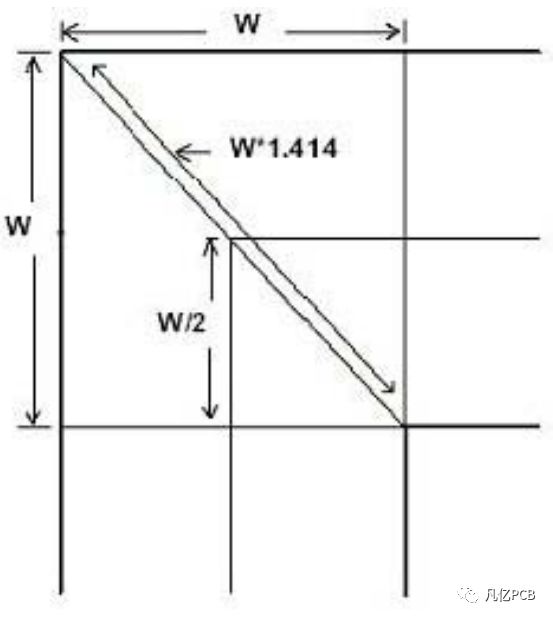

一般直角走线导致的阻抗变化在7%-20%之间,因而反射系数最大为0.1左右。而且,从下图可以看到,在W/2线长的时间内传输线阻抗变化到最小,再经过W/2时间又恢复到正常的阻抗,整个发生阻抗变化的时间极短,往往在1Ops之内,这样快而且微小的变化对一般的信号传输来说几乎是可以忽略的。

90度拐角分析

如果你想学习更全面的PCB设计知识,

可以了解我们的Allegro 弟子计划一对一课程。

很多人对直角走线都有这样的理解,认为尖端容易发射或接收电磁波,产生EMI,这也成为许多人认为不能直角走线的理由之一。然而很多实际测试的结果显示,直角走线并不会比直线产生很明显的EMI。也许目前的仪器性能,测试水平制约了测试的精确性,但至少说明了一个问题,直角走线的辐射已经小于仪器本身的测量误差。

总的说来,直角走线并不是想象中的那么可怕。至少在GHz以下的应用中,其产生的任何诸如电容,反射,EMI等效应在TDR测试中几乎体现不出来,高速PCB设计工程师的重点还是应该放在布局,电源/地设计,走线设计,过孔等其他方面。

当然,尽管直角走线带来的影响不是很严重,但并不是说我们以后都可以走直角线,注意细节是每个优秀工程师必备的基本素质,而且,随着数字电路的飞速发展,PCB工程师处理的信号频率也会不断提高,到10GHz以上的RF设计领域,这些小小的直角都可能成为高速问题的重点对象。

-

pcb

+关注

关注

4333文章

23224浏览量

401855 -

直角走线

+关注

关注

0文章

22浏览量

10738

原文标题:浅谈PCB设计中的走线——直角走线

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB中直角走线的对信号的影响有哪些?

PCB Layout中的专业走线解析

高速PCB设计中的走线技巧

pcb布线为什么不走直角

PCB直角走线的影响

解析PCB设计中的直角走线

解析PCB设计中的直角走线

评论