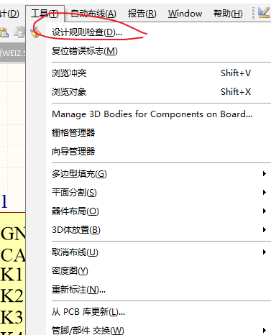

Layout时最常用的错误检查,这需要在布局布线前做好规则设置,所谓磨刀不误砍柴工,尤其是在Layout时,如果违反规则,就会亮起绿色,项目规模较大的时候特别影响视觉。

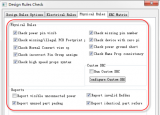

执行规则检查后,检查的结果会按下表依次列出:

以上的规则检查项对应的中文翻译、具体的规则设置、约束的具体PCB内容讲解如下:

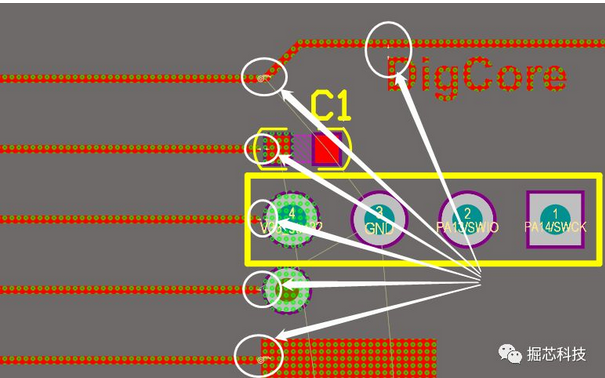

1. Clearance Constraint (Gap=10mil) (All),(All)

间隙约束,也就是约束PCB中的电气间距,比如阻容各类元件的焊盘间距小于规则中的设定值,即报警。

如下图中的走线与焊盘、铜皮、文本字符(DigCore)之间的距离,不同网络的两个焊盘之间的间距小于10mil,这样容易存在焊接过程中的接触短路风险:

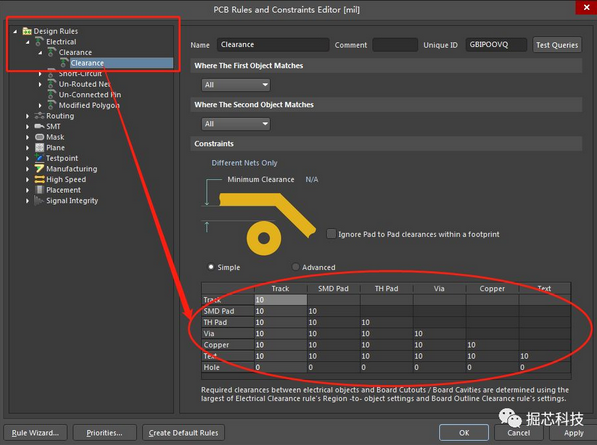

具体设置规则的方式:

该规则可以设置不同类型电气组件的间距约束值,如上图的表中,可以分别设置走线(Track)、贴片焊盘(SMD Pad)、通孔焊盘(TH Pad)、过孔(Via)、覆铜(Copper)、丝印字符(Text)、孔(Hole),这些两两之间的间距都可以设置约束值。

注:通孔焊盘是元件的引脚,打通PCB板并且孔周围有焊盘;过孔是布线时需要切换板层时靠过孔来穿透,过孔一般是全部被阻焊油覆盖的;孔则可以认为是通孔焊盘、过孔这些东西中间的孔,或者是机械孔,也就是被打穿后空掉的部分就是Hole。

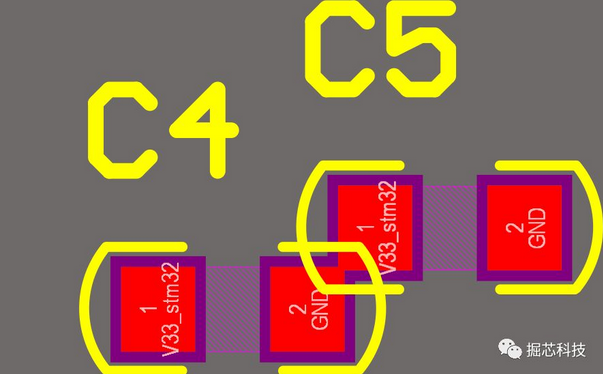

2. Short-Circuit Constraint (Allowed=No) (All),(All)

短路约束,即禁止不同网络的电气相接触。

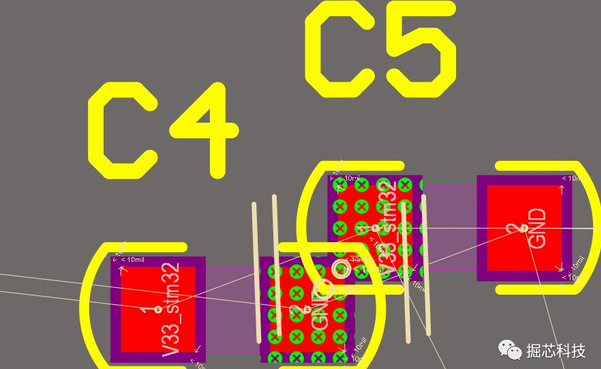

比如下图中的C4、C5两个电容,其中的两个焊盘电源和GND已经完全接触,这是不允许的。

短路的位置,执行约束规则检查后如下图:

该约束默认都是已经给设置了的,保持默认即可。

3. Un-Routed Net Constraint ( (All) )

未布线网络。

有时候板子元件数量巨大,很多网络焊盘可能是叠层放置,靠得很近,肉眼十五分确定是否已布线,即使AD有飞线显示功能(View->Connections->Show Net)如果挨得元可以明显看到一条细细的飞线,如下图:

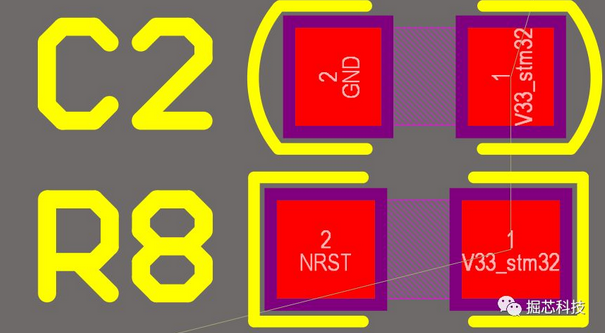

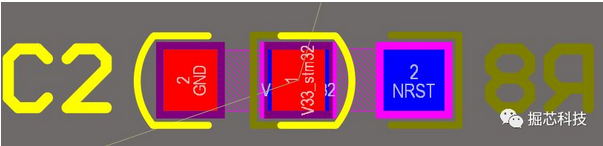

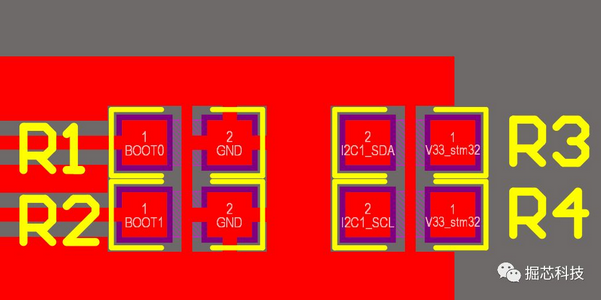

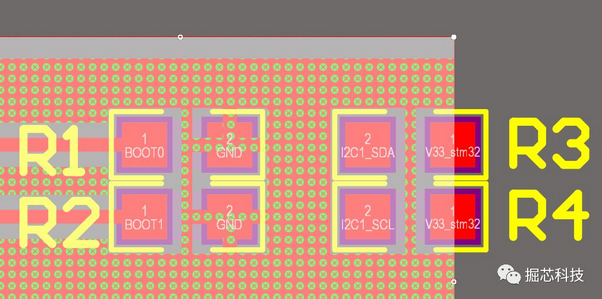

可如果挨得很近,甚至是不同层的时候,两个焊盘却在同一坐标位置,飞线将会是一个“点”的形状,如下图C2和R8的Pin1是同网络,飞线显示也就一个点,完全看不到未连接的状态:

因此利用该检查项快速定位到未布线的网络和具体坐标位置。

4. Modified Polygon (Allow modified: No), (Allow shelved: No)

多边形覆铜调整未更新。

这项检查是放置在电源分割、模拟地数字地分割时候,调整了分割范围、边框外形而未更新覆铜。

如下图,正常覆铜后:

而如果手动调整覆铜的外轮廓或者形状,则会有如下的报错:

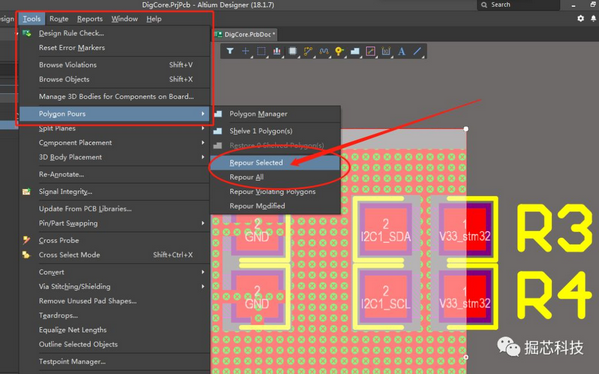

这个错误还是比较明显能够肉眼察觉,出现此错误时,执行菜单Tools->Polygon Pours->Repour Selected,对已选择的错误覆铜执行重新覆铜,或者选择Repour All对整个PCB的覆铜区域全部重新覆铜:

5. Width Constraint (Min=6mil) (Max=100mil) (Preferred=6mil) (All)

布线线宽约束。

线宽的约束体现在电源走线是需要考虑电流大小、PCB制板厂的最小线宽工艺,这些需要做最小线宽的约束设置;而有些信号线需要考虑阻抗要求、差分信号要求,或者一些BGA的扇出布线,这些需要做最大线宽的约束设置。

设置方法如下:

对不同类型的网络进行分别设置的好处是,在Layout的时候,调出布线功能是,软件自动匹配规则中的线宽对应当前正在布线的网络。

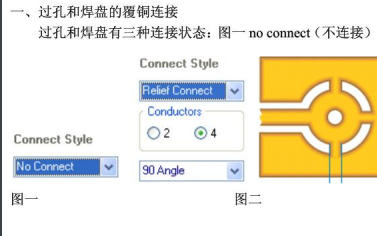

6. Power Plane Connect Rule(Relief Connect )(Expansion=20mil) (Conductor Width=10mil) (Air Gap=10mil) (Entries=4) (All)

电源平面连接规则。

此项检查常用于多层板项目中。主要设置覆铜时候铜皮和焊盘管脚连接方式、距离等参数。

7. Hole Size Constraint (Min=11.811mil) (Max=196.85mil) (All)

孔大小约束。这个参数主要是影响到PCB制板厂对钻孔工艺,对于设置太小或者太大的孔,制板厂未必会有这么细的钻头或者这么精准的工艺,同时也未必有太大的钻头,毕竟这是控制精细的东西,不是给毛坯房钻孔装修。

该参数的设置方式如下图:

8. Hole To Hole Clearance (Gap=10mil) (All),(All)

孔到孔之间的间距约束规则。

有时候元器件的封装有固定孔,而与另一层的元件的固定孔距离太近,从而报错。

如下图中,TF卡座的定位孔与背面的贴片按键固定孔距离太近,出现违反规则的警告:

9. Minimum Solder Mask Sliver (Gap=5mil) (All),(All)

最小阻焊间隙。

一般的在焊盘周围都会包裹着阻焊层,组焊层存在的目的是生成工艺中,阻焊油、绿油的开窗范围。如下图中的D1两个焊盘,周围的紫色外框就是阻焊层,而与下边一个焊盘的组焊层距离小于9mil,而报警。

最小阻焊间隙的设置如下图:

10. Silk To Solder Mask (Clearance=4mil) (IsPad),(All)

丝印到阻焊距离。

如下图,丝印时一条在Topoverlay的导线(制板后,该丝印是在PCB板表面的,一般白色),与阻焊层距离太近。

此设置时软件默认值10mil,设置方法如下图:

11. Silk to Silk (Clearance=5mil) (All),(All)

丝印与丝印间距。

这个是同一层丝印之间的距离规则。这个经过一般是在布局后报警数量最多的,因为布局后如果没有及时调整位号丝印的位置,一般都是各种旋转之后,位号丝印字会叠放在了别的器件焊盘上,这个时候报警最多。

如下图,布局时R5的位号丝印叠放在了R6的Pin1焊盘上,此时R6的丝印边框和R5的位号丝印重叠,这个如果不关注,制板时候,同时R5的位号丝印就会被R6的焊盘给裁剪掉,而看不到R5的位号丝印。

丝印与丝印间距的设置方式如下:

12. Net Antennae (Tolerance=0mil) (All)

网络天线。

这个规则的是指某些网络如果走线走到一半,并且走线长度超过设定值,而没有另一头接应,就形成天线效应。

如下图中的R6电阻的Pin2管脚,多出一根线而未走完或者本该不再走线,这样就致使天线效应的警报。

天线效应规则约束,可以设定走线长度阈值,并且超过此阈值则认为存在天线效应风险而产生警告:

13. Height Constraint (Min=0mil) (Max=1000mil) (Prefered=500mil) (All)

高度约束。

设定元器件的高度,从元器件所在的层算起。

★★★★★推荐文章

《嵌入式硬件通信接口-使用RingBuffer处理数据(二)详细设计过程》

《嵌入式硬件通信接口-使用RingBuffer处理数据(一)》

《快速开发MQTT(一)电子工程师眼中的MQTT》

《快速开发MQTT(二)初识MQTT》

《MQTT客户端搭建-最清晰的MQTT协议架构》

《MQTT服务端搭建-最快方式验证自己开发的客户端》

★★★★★相似文章

《嵌入式硬件通信接口协议-UART(五)数据包设计与解析》

《嵌入式硬件通信接口协议-UART(四)设计起止式的应用层协议》

《嵌入式硬件通信接口协议-UART(三)快速使用串口及应用》

《嵌入式硬件通信接口协议-UART(二)不同电气规范下的标准》

《嵌入式硬件通信接口协议-UART(一)协议基础》

《嵌入式硬件通信接口协议-SPI(二)分层架构设计模拟接口》

《嵌入式硬件通信接口协议-SPI(一)协议基础》

★★★★★扩展阅读

《【硬件电路】AltiumDesigner18规则检查含义》

《【硬件电路】N沟道、P沟道MOS管基本原理与应用案例》

文章首发于同名微信公众号:DigCore

欢迎关注同名微信公众号:DigCore,及时获取最新技术博文。

原文链接:https://mp.weixin.qq.com/s/jxlUBt-i9uWHfy6tMid3CQ

(说明:此处的文章从微信公众号拷贝而来,图片或者排版上可能存在一定的瑕疵,欢迎点击原文链接阅读)

-

PCB软件

+关注

关注

0文章

26浏览量

13508 -

altium

+关注

关注

47文章

953浏览量

118712 -

DRC规则

+关注

关注

0文章

5浏览量

3870

发布评论请先 登录

相关推荐

【硬件电路】AltiumDesigner18规则检查含义

【硬件电路】AltiumDesigner18规则检查含义

评论