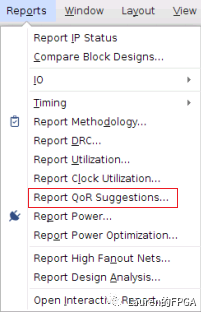

从Vivado 2018.3开始,可以通过图形界面方式使用命令report_qor_suggestions,如图1所示。从Tcl角度而言,就是多了一个-name选项。

图1

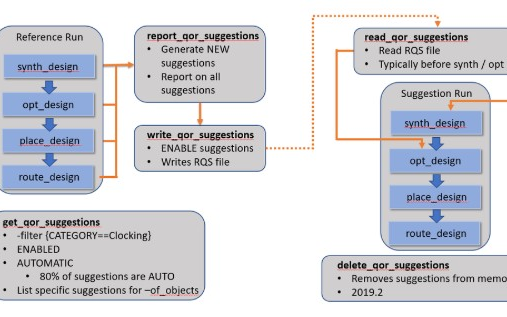

report_qor_suggestions的功能是在分析设计的基础上给出改善设计的建议,这些建议可以用.xdc或.tcl文件的形式体现出来,无论是Project模式还是Non-Project模式,这些文件均可加入工程中使用最终达到优化设计的目的。本质上,这些建议是与UFDM(UltraFast Design Methodology)保持一致的。

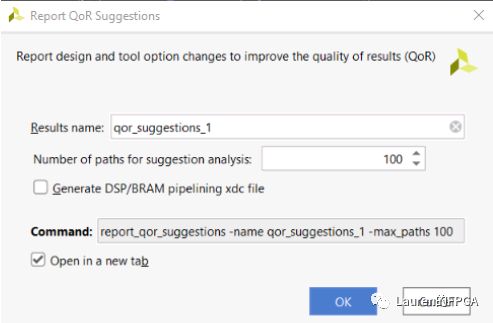

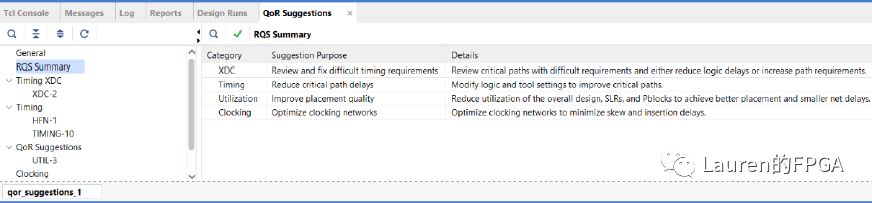

在图形界面方式下使用report_qor_suggestions会显示如图2所示界面,最终生成如图3所示的Summary。

图2

图3

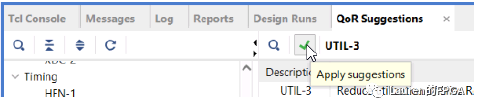

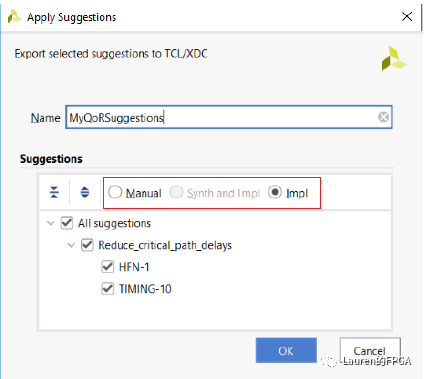

点击Apply Suggestions按钮,如图4所示,会弹出图5所示界面。最终会生成针对设计的优化建议,也就是前文所述的.xdc或.tcl文件。

图4

图5

在图5中,Manual用于显示无法以.xdc或.tcl形式提供的建议。Synth and Impl用于生成可应用于Synthesis和Implementation阶段的建议,而Impl用于生成仅适用于Implementation阶段的建议。

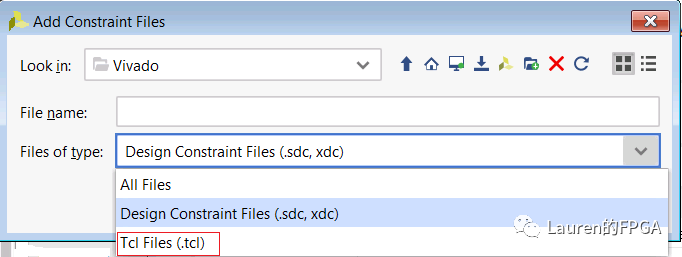

如果选择Synth and Impl,会生成两个文件:RQSPreSynth.tcl和RQSImplCommon.tcl。Project模式下,RQSPreSynth.tcl可作为约束文件直接添加到Constraint Set里(Vivado支持.tcl文件作为约束文件,添加时将文件类型切换为.tcl即可,如图6所示)。

图6

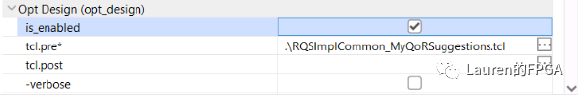

RQSImplCommon.tcl则应作为Hook Script在Opt Design阶段添加,如图7所示。

图7

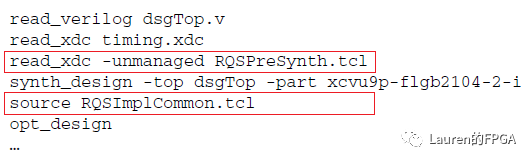

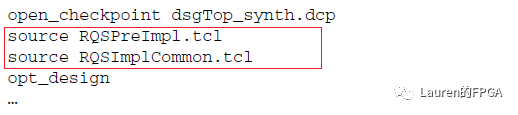

Non-Project模式下,这两个文件的添加方式如图8所示。

图8

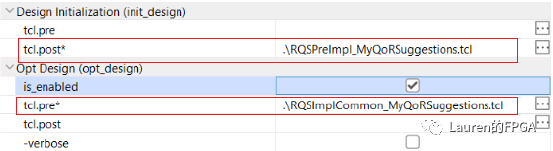

如果选择Impl,则会生成两个文件RQSPreImpl.tcl和RQSImplCommon.tcl。两者添加位置如图9所示。

图9

Non-Project模式下,这两个文件的添加方式如图10所示。

图10

对于Vivado 2018.3之前的版本,尽管没有图形界面方式,但可直接通过Tcl命令执行。添加-output_dir选项,指定文件生成目录,可在指定位置生成上述文件。需要注意的是RQSPreSynth.tcl和RQSPreImpl.tcl两者是不能同时使用的。

对于一些以DSP、BRAM或URAM为起点或终点的路径,如果这些模块自带的一些流水寄存器没有使能,可通过选项-evaluate_pipelining生成额外的约束使能这些流水寄存器。但要特别注意,这时设计的功能已经被修改,生成的约束只能用于评估这些流水寄存器被使能的情况下对设计时序的影响。就时序评估而言,相比于通过修改RTL代码使能这些寄存器,采用选项-evaluate_pipelining更快捷。如果使能这些寄存器能改善时序,那么可以再返回修改RTL代码,保证设计功能正确。

常见问题:

Q: 什么阶段使用report_qor_suggestions?

A: 该命令可在Synthesis和Implementation的任意阶段使用,但从Baselining的角度而言,最先在哪个阶段发现时序违例,就在那个阶段使用。

Q: 该命令生成的.tcl文件在哪里?

A: 如果直接在Tcl Console中输入该命令,相应的.tcl文件生成目录由选项-output_dir确定;如果是通过图形界面方式使用,相应的.tcl文件在当前工作目录下。当前工作目录可通过命令pwd查询。

结论

report_qor_suggestions会在分析关键路径的基础上给出优化建议,生成相应的.tcl文件,而这些文件可加入工程中执行达到优化的目的。

-

寄存器

+关注

关注

31文章

5388浏览量

121718 -

Vivado

+关注

关注

19文章

818浏览量

67139

原文标题:Vivado 2018.3 report_qor_suggestions怎么用

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为什么不用2017.4或者2018.3呢?最稳定的vivado版本是哪一种?

Vivado 2018.3这个Gadget你用了吗?

关于Vivado 2019.1的Dashboard功能详解

Report QoR Suggestions助力解决Vivado设计问题

解决方法论问题可提升实现的一致性

FPGA设计:关于Report QoR Assessment 命令的使用

基于Vivado/SDK 2018.3的XIP参考设计

【Vivado那些事】Vivado下怎么查看各子模块的资源占用?

赛灵思Vivado ML版优化应用设计

如何建立Vivado工程以及硬件配置

Vivado使用进阶:读懂用好Timing Report

在Vivado中利用Report QoR Suggestions提升QoR

Vivado 2018.3 report_qor_suggestions怎么用

Vivado 2018.3 report_qor_suggestions怎么用

评论