摘要

文章详细的研究了导电膏塞孔替代电镀铜制作任意层互连印制板时的可靠性及其对电性能的影响。根据范·米塞斯屈服准则分析了塞孔材料CTE可靠性原理并进行实验验证,同时评估了塞孔阶数、孔底残胶、塞孔孔内气泡对可靠性的影响,最后分析了导电膏塞孔对阻抗及损耗的影响。结果表明,对于导电膏塞孔工艺,在11阶盲孔设计时,其热应力、温冲测试等性能测试均满足产品可靠性要求,且导电膏塞孔对25G以下高速产品信号传输无明显影响。

前言

导电膏塞孔是实现任意层互连的技术方案之一,其雏形是松下的ALIVH(Any Layer Interstitial Via Hole)技术和东芝B2it(Buried Bump Interconnection Technology)技术[1]。任意层互连技术发展的一个关键技术是微孔化,即层与层之间通过微孔进行导通互连。微孔加工目前激光钻孔技术可以实现;而在微孔金属化技术这块,目前主要分三种:电镀填孔、导电材料塞孔、铜凸块[1]。其中,导电膏互连技术由于其用导电膏替代电镀进行填孔,不仅精细线路、高厚径比等制作工艺难度降低,流程简化;而且可以实现绿色生产,节省能源等特点,因此该技术具有广阔的发展前景。

导电膏主要成分是铜、锡、环氧树脂,因此导电率较电镀铜差,其结合与导通机理区别于电镀铜方式,主要是通过高温烧结在焊盘表层形成铜锡合金互连[2]。文章通过实验设计,评估了导电膏塞孔互连对于高速信号完整性的影响,同时评估了材料热膨胀系数与多阶盲孔设计可靠性问题,为该技术的推广应用提供技术参考。

1

试验部分

1.1试验材料与仪器

材料:very low loss覆铜板和半固化片、导电膏等。

仪器:四端口网络分析仪、高低温冲击试验箱、金相显微镜。

1.2试验设计

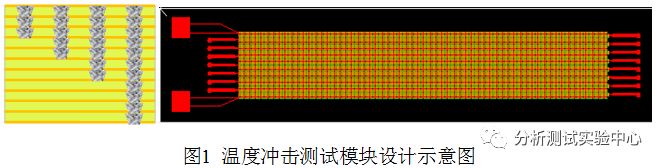

(1)导电膏塞孔互连可靠性评估:

为评估导电膏塞孔互连结构可靠性,分别设计了30 ppm/℃、35 ppm/℃、45 ppm/℃不同CTE材料的测试板。同时设计了1、3、5、7、11阶盲孔塞孔互连设计。可靠性测试条设计如下:

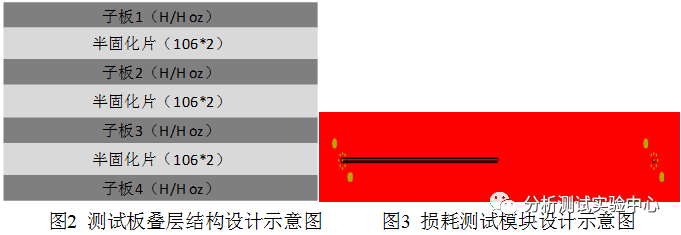

(2)塞孔互连对电性能影响:

为确定导电膏塞孔对于高速信号传输信号完整性影响,设计了8层板。采用阻抗计算软件进行阻抗设计,单端阻抗设计为50Ω;差分阻抗设计为100Ω。其叠层结构及阻抗线设计如下:

2

结果与讨论

2.1塞孔互连可靠性影响

2.1.1材料CTE影响

(1)材料CTE可靠性原理分析

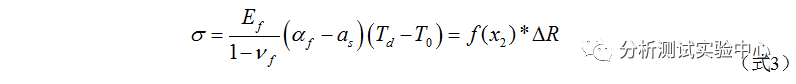

根据范·米塞斯屈服准则[3],盲孔结构等效应力公式如下:

其中,Ef表示孔内物质弹性模量,vf表示孔内物质泊松比,af表示孔内物质热膨胀系数,as表示层间介质材料<Tg下热膨胀系数,Td表示测试最高温,T0表示测试最低温。因此,可将以上等效应力公式转化为:

式中,△α为热膨胀系数差异。在温度冲击过程中,受材料变形产生孔内应力的影响,电阻值相应产生一定的改变。从而可以将孔内应力与阻值变化之间建立函数关系:

因此,从以上推论可知:

即:在固定温度冲击测试温度、时间等测试条件下,其可靠性结果正比于产品设计材料之间的热膨胀系数差异[3-6]。

(2)材料CTE可靠性验证

图4为不同CTE材料1阶盲孔设计对应-55℃-125℃温度条件,200次温冲循环阻值变化关系曲线。相同设计下,随着盲孔塞孔材料与板材之间CTE差异的增大,其温度冲击过程中孔内界面应力增大,从而导致温冲前后阻值变化增大。因此,对于产品设计,为满足更好的可靠性,材料CTE越接近越好,而不是CTE越小越好。

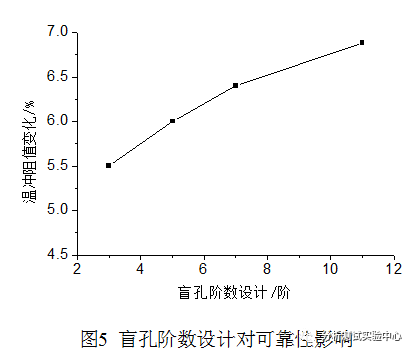

2.2.2塞孔阶数设计影响

图5是相同材料下不同盲孔阶数叠孔设计对应-55℃-125℃温度条件,200次温冲循环阻值变化关系曲线。随着盲孔叠孔阶数的增加,受外界温度冲击时内部应力叠加,导致热胀冷缩过程变形量增大,温冲阻值变化相应增大。该阻值变化值直接体现产品可靠性,因此,产品设计时应考虑叠孔影响。避免叠孔层数太多导致可靠性不良。从实验结果可知,导电膏塞孔烧结互连结合力较好,盲孔叠孔阶数每增加一层,阻值变化增大0.174%。盲孔设计11阶时,温冲前后阻值变化为6.88%,满足±10%变化标准。

2.2.3塞孔气泡影响

孔内气泡主要受两方面影响:一是导电膏内部空气、挥发性成分存在,热固化烧结时没有排出残留;另一方面受塞孔过程压力、速度、抽真空等导致塞孔不饱满影响。因此,气泡或多或少会有存在,一般直径大小<20μm。

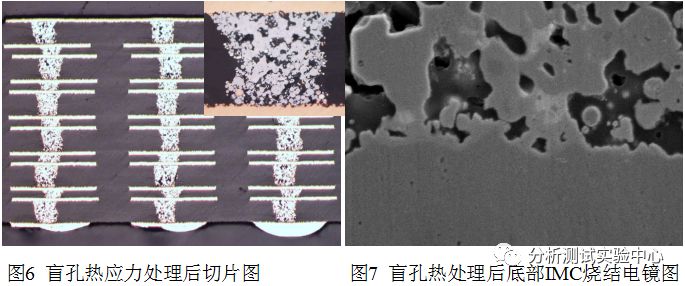

图6是11阶盲孔叠孔设计华为无铅+288℃三次漂锡处理后的切片图。从图可以看出,孔内导电膏中不均匀的分布有一些气泡。但是热应力测试后,盲孔顶底部及孔壁与介质材料界面都未发现分层等问题。图7为盲孔顶底与铜面烧结界面IMC层扫描电镜观测图。热应力处理前后,IMC层保持完好,未出现裂痕等不良问题。因此,塞孔气泡存在烧结完全的情况下,对产品可靠性无明显影响。

2.1.4孔底残胶影响

除塞孔控制外,激光钻孔是导电膏塞孔互连工艺非常重要的一环。当孔底激光钻孔树脂或碳膜未清除干净,塞孔后残留树脂或碳膜会阻碍孔内导电膏与底铜的烧结,无法形连续、均匀的IMC层,直接决定了信号导通性和可靠性。上图8是孔底树脂残留导致温冲过程中盲孔失效过程监控图。

对上图失效处切片可知,孔底与底铜结合处出现裂痕。对此处的导电膏树脂、介质层树脂和激光孔孔底与导电膏结合处进行元素分析对比可知,导电膏中的树脂与介质层树脂差别在于介质层树脂中含有Si元素。而在激光孔孔底结合界面元素分析发现Si元素的存在,说明激光钻孔有树脂残留。因此,导电膏塞孔工艺,需对激光钻孔品质进行过程严格管控保证产品质量。

2.2塞孔互连信号完整性影响

2.2.1塞孔互连对阻抗的影响

下图9是导电膏塞孔与常规电镀填孔工艺相同设计下单端过孔阻抗对比。由于导电膏电导率较电镀铜大,导电膏塞孔过孔阻抗较电镀填孔过孔阻抗大2Ω,两者之间过孔阻抗差异在4%左右。因此,对于导电膏工艺制作,在前端工程阻抗设计时需进行评估补偿。

2.2.2塞孔互连对损耗的影响

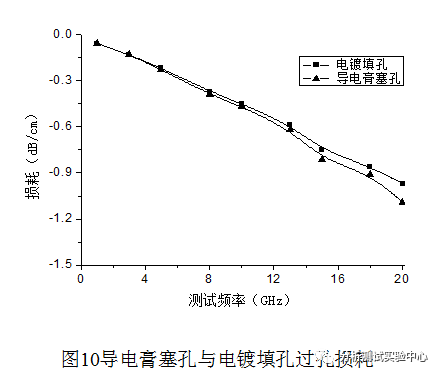

图10是导电膏塞孔与常规电镀填孔工艺相同设计下单端损耗测试结果。在12.5 GHz测试频率下,导电膏塞孔与电镀填孔损耗分别为0.62 dB/cm和0.59 dB/cm,两者之间差异0.03 dB/cm;当测试频率继续增大,两者之间损耗差异开始明显。频率增大到20 GHz时,两者损耗差异增大到0.12 dB/cm。因此,25G以下高速产品采用导电膏塞孔工艺信号损耗基本无影响。但对于更高速需求产品的应用则需评估塞孔互连对信号完整性影响来确认。

3

结论

通过以上试验,得出以下结论:

(1)材料的选择对于导电膏塞孔互连可靠性有着至关重要的影响,选择与导电膏CTE越接近的材料、优化盲孔设计、做好激光钻孔品质管控是提升导电膏塞孔互连产品可靠性的关键;

(2)随着盲孔叠孔层数的增加,失效概率直线增大。常规Z-CTE值45 ppm/℃左右的材料,其盲孔叠孔设计11阶可靠性测试满足IPC标准要求。推论预估设计达到30阶时会出现温冲循环测试前后阻值超过±10%而失效;

(3)导电膏塞孔互连工艺对25G以下高速产品应用时信号传输无明显影响;但随着信号或频率继续增大,由于导电膏电阻率较电镀铜大的原因,信号损耗开始有明显差异。

-

PCB设计

+关注

关注

394文章

4725浏览量

87726 -

信号完整性

+关注

关注

68文章

1423浏览量

96032 -

电镀铜

+关注

关注

0文章

26浏览量

9200 -

导电

+关注

关注

0文章

240浏览量

21727 -

可制造性设计

+关注

关注

10文章

2065浏览量

15861 -

华秋DFM

+关注

关注

20文章

3496浏览量

5003

原文标题:导电膏塞孔的可靠性及其对电性能的影响

文章出处:【微信号:ruziniubbs,微信公众号:PCB行业工程师技术交流】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

浅析印制板的可靠性2

碳膜印制板制造技术概述及特点

线路电镀和全板镀铜对印制电路板的影响

电镀对印制PCB电路板的重要性

网印贯孔印制板制造技术

如何才能获取高可靠性的印制板?

干货:PCB电镀铜前准备工艺有哪些?

分析 | 电镀铜前准备工艺:沉铜、黑孔、黑影,哪个更可靠?

如何提高印制板的可靠性

导电膏塞孔替代电镀铜制作任意层互连印制板时的可靠性及其对电性能的影响

导电膏塞孔替代电镀铜制作任意层互连印制板时的可靠性及其对电性能的影响

评论