嵌入式系统设计人员面临着对更高性能和更快上市时间的不断增长的需求。嵌入式处理器需要经常实时地执行不断扩展的任务。同时,应用需要高吞吐量和高能效以及小外形和低成本。多核微控制器单元(MCU)提供了一种可行的新解决方案,利用模块化设计以经济的价格提供多倍的性能提升。

几十年来,随着IC上晶体管数量的增加,芯片性能不断提高。采用高速缓存和流水线等技术的更复杂的架构允许芯片设计人员使用不断增加的硅密度来不断提高处理速度。这已不再是这种情况。芯片设计人员已经耗尽了替代架构的可能性。生产力的增长已经从跟上摩尔定律的速度下降到不到一半。当今提高生产力的唯一方法是通过使用多个CPU来利用模块化。这导致了多核MCU的发展。

硬件:同构与异构

我们将多核MCU定义为具有两个或多个CPU的微处理器,这些CPU一致地共享一个公共存储器。在多核架构中,每个处理器都有自己的指令流作用于自己的数据流(MIMD)。

多核MCU可以归类为同构或异构。顾名思义,同类模块具有两个相同的CPU,可以并行或冗余地运行操作。德州仪器(TI)的Hercules系列产品专为安全应用而设计,拥有两个同步运行的ARM Cortex-R4F CPU。它们执行相同的操作,然后比较每个时钟周期的结果,有效地建立一个“安全岛”,为设计人员提供可靠的基础,以在医疗,工业和汽车应用中实施更复杂的操作。为了消除潜在的常见故障模式,设计团队将芯片组定向为彼此90°,并引入了处理器时序的延迟。该芯片可在高达200 MHz的频率下运行,并可运行32 MB的闪存。

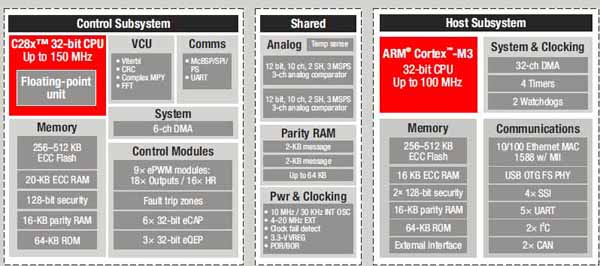

对于具有特殊要求的应用 - 例如,计算密集型操作或大量信号处理 - 异构MCU可以提供更好的解决方案。异构MCU包含不同类型的处理器。它可能具有通用CPU以及数字信号处理器(DSP)和/或专用于浮点运算的处理器。例如,TI的Concerto异构多核MCU结合了C28x 32位CPU和ARM Cortex M3 32位CPU来优化子系统(图1)。 C28管理控制子系统,提供高达150 MHz的浮点运算。同时,ARM Cortex处理通信,逻辑和排序/监控,速度高达100 MHz。 MCU在闪存和RAM上都集成了错误检测功能,以及带有多个系统看门狗的内置时钟监控功能。

图1:异构多核MCU,如Concerto包含不同的内核,可为每项任务提供最佳解决方案。

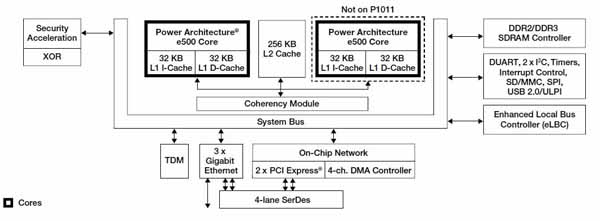

真正的多核MCU需要的不仅仅是具有共享内存的多个内核。为了实现有效的并行处理,架构必须确保每个CPU都在最新的可能数据上运行。在双核MCU中,每个CPU都有一个专用的I(L1)高速缓存,但所有CPU共享一个2级(L2)高速缓存(图2)。挑战在于确保如果CPU1更新其L1缓存中的变量,CPU2将使用正确的信息,而不是其L1缓存先前从L2缓存中获取的旧数据。设计通常使用各种名称已知的硬件监视器来完成此操作,包括一致性模块或简单地说是窥探器。例如,当CPU 1将变量保存到其L1高速缓存时,一致性模块注册该更改并使CPU2的L1高速缓存中的数据无效。当CPU2尝试访问该位置时,它无法并且必须转到L2缓存以获取新数据。

图2:来自飞思卡尔的QorIQ系列功能一个一致性模块,用于监控每个CPU的I级缓存的更改,以确保每个核心都运行最新的数据。

飞思卡尔半导体的QorIQ P2平台系列通信处理器基于双e500 Power Architecture内核,每个CPU具有双32 KB L1高速缓存,另外还有256 KB二级高速缓存。用户可以选择在两个内核之间对L2缓存进行分区,也可以将其配置为存储内存或SRAM。 P2020评估板,名为P2020COME-DS-PB-ND,使工程师能够熟悉飞思卡尔双核MCU的复杂性。 Digi-Key网站还提供双核QorIQ产品的产品培训模块。

功能并行与数据并行

硬件只是一个开始。多核MCU的最大好处是程序员可以利用软件最大限度地提高工作效率的方式。有多种方法可以编程多核MCU。在对称多处理(SMP)中,也许是最常见的方法,所有CPU都可以访问公共内存空间并由单个操作系统运行。 CPU通过共享内存中的变量进行通信。任何CPU都可以运行任何进程,但通常在任何给定时间都不会在CPU之间共享进程。

非对称多处理(AMP)提供更多自由度。在AMP中,可以将特定CPU分配给某些进程以实现最佳性能。非对称体系结构甚至可以在不同的处理器上运行不同的操作系统,在核心处理和时间敏感操作上运行实时操作系统(RTOS),而通用核心在Linux上运行。

多核MCU的主要优点之一是并行处理能力。并行处理可分为功能并行处理和数据并行处理。功能并行性涉及将任务分解为单个运算符。不同处理器执行不同功能。这是一种强大的技术,但不是多核方法中真正的肌肉所在。

数据并行性提供了最大的性能提升。它涉及将数据划分为由不同核心处理的各个部分。这是一种功能强大的技术,但由于CPU通过共享内存进行通信,因此同步对于确保CPU以正确的顺序和正确的数据进行操作至关重要。

多线程或fork/join并行性提供了一种确保同步的方法。系统将处理划分为线程,在CPU之间拆分数据,每个CPU在其数据块上运行相同的代码。当线程完成其操作时,它们重新组合以产生结果。在完成所有线程之前,操作不会结束,因此这种方法可确保同步。

使用先进先出(FIFO)缓冲区提供了另一种同步方法。当CPU通过FIFO进行通信时,如果它是空的,它们只能写入它。数据强制执行优先级 - 如果缓冲区已满,则进程后期的CPU无法写入。它必须轮流等待。

互斥(互斥)锁提供了更复杂的同步方法。通过硬件实现,互斥锁可确保在任何给定时间只有一个CPU拥有共享变量的所有权。当给定线程开始其操作时,它读取变量并设置锁定,这阻止其他线程访问信息。当操作结束时,线程释放锁定,以便其他人可以访问它。

特别是在并行处理方面,多核MCU为嵌入式设计提供了强大的解决方案。但是,它们必须经过精心设计和编程。线程越多,该过程就越具有挑战性。错误可能导致系统死锁,循环结束,甚至产生可能的结果,这些结果意外地依赖于首先完成哪个线程。

硬件设计有其自身的挑战。虽然解决方案功能强大,但重要的是要意识到它们不一定是给定应用程序的最佳解决方案。用户需要考虑处理器功能和带宽限制 - 与内核一样快,他们都将使用相同的通信总线,ADC和其他资源。

总体而言,多核MCU为各种嵌入式设计挑战提供了有用的选择。存在用于简化嵌入式设计和编程的工具。通过访问它们并密切关注测试和验证,设计团队可以获得高性能和经济的价格点,并加快产品上市速度。

-

mcu

+关注

关注

146文章

17143浏览量

351142 -

嵌入式

+关注

关注

5082文章

19118浏览量

305091 -

操作系统

+关注

关注

37文章

6818浏览量

123326

发布评论请先 登录

相关推荐

多核嵌入式系统存在的局限性?怎么解决这些问题?

多核MCU可用于简化嵌入式设计 精选资料推荐

嵌入式多核程序设计资料分享

中国首颗ARM+RISC-V异构多核MCU伴随IAR在上海国际嵌入式展亮相

嵌入式异构多核的片上通信架构设计

NI LabVIEW 8.6 全面简化嵌入式系统原型构造与发

嵌入式多媒体应用的多核编程框架

嵌入式多媒体多核应用软件设计解析

嵌入式多媒体多核应用软件设计框架

多核MCU可用于简化嵌入式设计

嵌入式linux和物联网,嵌入式Linux或RTOS:用于物联网

嵌入式linux和物联网,嵌入式Linux或RTOS:用于物联网

多核MCU可用于简化嵌入式设计

多核MCU可用于简化嵌入式设计

评论