软件定义无线电(SDR)是RF,数据转换和数字信号处理的复杂组合。此外,这些设备现在具有构建经济高效的SDR系统的性能。本文着眼于如何构建SDR系统,包括最近的开源开发。

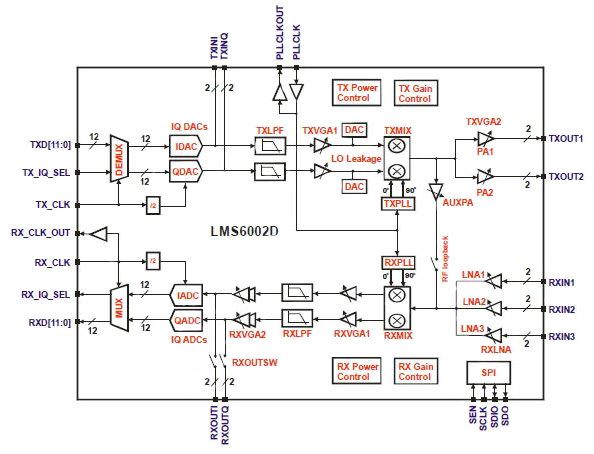

软件定义的系统变得越来越普遍,无线系统处于领先地位。使用单一架构来处理各种频率和越来越复杂的协议可以降低成本和尺寸,并可以降低整体功耗。但是,构建软件定义无线电(SDR)传统上并不容易。前端必须捕获尽可能多的频带,并能够将其下变频以由模数转换器(ADC)捕获,以便可以处理RF流以提取相关的数字数据。这需要高性能调谐器,高速ADC和复杂的数字信号处理器(DSP),而且最近才有每个元件具有从分立元件实现SDR的性能水平,如图1所示。

这显示了从通过ADC的高速信号捕获到处理数据的DSP引擎的不同元素。

图1:显示复杂性的典型SDR架构在多通道系统中,硬件定义无线电(HDR)实现需要为每个通道进行大量模拟信号处理,从而导致电路板面积大,模拟设计复杂度高,灵活性有限以及对RF的敏感性干扰。千兆采样ADC允许将多个窄带和宽带通道组合成一个超宽带通道;从而将信道化从模拟域推向DSP,FPGA或ASIC,其中频率和带宽可以通过数字方式进行控制,从而实现最大的系统灵活性和可重新配置性。

SDR方法通过较小的电路板和较小的电路板降低模拟复杂性,从而提供优势。由于多个硬件通道被单个系统取代,因此功耗和系统成本更低。它也不易受到射频干扰,因此需要较少的屏蔽。虽然SDR已经用于军事通信和雷达系统,但它越来越多地用于3G/4G基站和宽带微波回程,以及光网络和最新的测试和测量设备。随着集成度的提高和成本的降低,它现在也可用于消费类多媒体应用一家名为Lime Microsystems的公司已采用RF元件并将其集成到单芯片中,采用开源硬件设计,以刺激SDR系统的发展。

SDR的单芯片

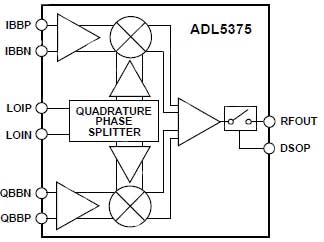

Lime Microsystems的LMS6002D是用于3GPP(WCDMA/HSPA,LTE),3GPP2(CDMA2000)和4G LTE应用以及GSM微微BTS的完全集成的多频带,多标准RF收发器。它将LNA,PA驱动器,RX/TX混频器,RX/TX滤波器,合成器,RX增益控制和TX功率控制与极少的外部元件相结合。

图2: LMS6002D集成了SDR的前端。

LMS6002D收发器的顶层架构如图2所示。发送器和接收器均采用零中频架构,提供高达28 MHz的调制带宽,相当于14 MHz基带IQ带宽。

在发送端,来自基带处理器的IQ DAC采样通过12位多路并行CMOS输入级总线提供给LMS6002D。模拟IQ信号由片内发送DAC生成,并将这些信号馈入TXINI和TXINQ输入。发送低通滤波器(TXLPF)去除由DAC的零保持效应产生的图像,然后IQ信号被放大,并且本地振荡器(LO)泄漏DAC在IQ路径中插入DC偏移以取消LO泄漏。然后将IQ信号与发送PLL输出混合以产生调制的RF信号。然后通过两个独立的可变增益放大器(TXVGA2)对该RF信号进行分离和放大,并提供两个片外输出作为RF输出。

发送器增益控制范围为56 dB,由TXVGA1 IF放大器提供,具有31 dB范围和TXVGA2 RF放大器,范围为25 dB。这两款发射器放大器均具有1 dB增益步进控制。

LMS6002D提供RF环回选项(见图2),可将TX RF信号反馈到基带进行校准和测试。 RF环回信号由辅助PA(AUXPA)放大,以增加环路的动态范围。

在接收侧,提供三个独立的输入,每个输入都有一个专用的LNA。每个端口的预处理RF信号首先由可编程低噪声放大器(RXLNA)放大。然后将RF信号与接收PLL输出混合以直接下变频到基带。在可编程带宽低通道选择滤波器(RXLPF)之前,IF放大器(RXVGA1)可以实现大的AGC步长。接收的IQ信号由可编程增益放大器RXVGA2进一步放大。在RXVGA2的输入端施加DC偏移,以防止饱和并保持ADC动态范围内的接收。使用片上接收ADC将产生的模拟接收IQ信号转换为数字域,并在多路复用的12位CMOS输出电平并行总线上作为输出提供给基带处理器。接收时钟RX_CLK在RX_CLK_OUT引脚的片外提供,可用于与基带数字接收数据采样时钟同步。

通过闭合RXOUT开关并关断RXVGA2,RXOUTI和RXOUTQ引脚可用作IQ ADC输入。在此配置中,ADC可用于测量两个外部信号,例如片外PA温度传感器或峰值检测器。

两个发送器输出(TXOUT1,TXOUT2)和三个接收器输入(RXIN1,RXIN2,RXIN3)提供多频段操作。接收器有三个增益控制元件,RXLNA,RXVGA1和RXVGA2。 RXLNA增益控制由AGC的单个6 dB步长组成,当存在大的同信道阻塞时,系统NF的减少是可接受的。主LNA(LNA1和LNA2)通过一个6位字进行精细增益控制,当需要大输入带宽时,提供±6 dB控制,用于频率校正。

RXVGA1模块提供25 dB的控制范围,7使用位控制字,响应不是对数线性的。最大步长为1 dB,因为当存在大型带内阻塞时,RXVGA1用于在信道滤波器之前降低系统增益所需的AGC步长。该增益可以在基带的控制之下或固定在校准上。同时,如果需要ADC输入端的恒定RX信号电平,RXVGA2可为AGC提供大量增益控制。它具有30 dB增益范围控制,步长为3 dB。

为了实现全双工操作,LMS6002D包含两个独立的合成器(TXPLL,RXPLL),均由相同的参考时钟源PLLCLK驱动。 PLLCLK信号在PLLCLKOUT输出引脚提供,可用作基带时钟。

发送器输出端口针对65Ω差分负载进行了优化,末级放大器为漏极开路,需要+3.3 V电源电压。但是,接收器输入都是不同的。 RXIN1是低频输入,可在0.3 - 2.8 GHz范围内工作,RXIN2是高频输入,可在1.5 - 3.8 GHz范围内工作。 RXIN1和RXIN2都需要匹配电路以获得最佳性能,而RXIN3是宽带输入,覆盖0.3 - 3.0 GHz范围,带有200差分输入,通常与宽带变压器匹配。

差分信号在接收和发送中完成整个芯片的模拟路径使用两个低相位噪声合成器来实现全双工操作。两种合成器都能够输出高达3.8 GHz的频率。每个合成器使用小数N分频PLL架构,两个合成器使用相同的参考频率,灵活性在23到41 MHz之间。合成器产生的复合输出具有适当的电平,可以驱动TX和RX路径中的IQ混频器。

LMS6002D可以接受限幅正弦和CMOS电平信号作为PLL参考时钟。支持直流和交流耦合,但必须为交流耦合模式启用内部缓冲器自偏置。 PLL参考时钟输入也可以是低压CMOS(例如2.5 V或1.8 V),通过降低时钟缓冲电源来实现。

该器件在TX和RX路径中集成了高选择性低通滤波器滤波器具有可编程通带,以便在DAC/ADC时钟频率上提供更大的灵活性,并在接收链中提供出色的相邻通道抑制。滤波器也是可调的,以补偿过程/温度变化。 TX和RX滤波器是相同的,但是通过SPI链路独立控制。

设计的一个关键要素是LMS6002D的所有功能完全由一组内部寄存器控制,可通过串口访问。这允许控制器根据环境设置芯片的不同标准。这些在图3中的开源MyriadRF硬件板上突出显示。

图3:用于LMS6002D SDR前端的开源MyriadRF硬件板。

在前端,新的RF采样架构有助于提高SDR的效率。德州仪器(TI)通过直接RF采样系列扩展了其每秒千兆次采样(GSPS)ADC产品系列。这些射频采样ADC的性能超过2.7 GHz,基于TI现有的12位ADC系列。结合其宽带放大器和低噪声时钟和定时解决方案,这使新的RF采样和宽带SDR系统能够有效地提高系统容量,可扩展性和灵活性,同时减小系统尺寸,重量,功耗,成本和设计时间。

RF采样的优势

RF采样ADC可以解决集成的一些挑战。单个直接RF采样ADC可替代混频器,LO合成器,放大器,滤波器和ADC的整个IF或ZIF采样子系统,同时降低物料清单(BOM)成本,设计时间,电路板尺寸,重量和此外,模拟频率下变频功能可以移植到DSP,FPGA或ASIC中,其中频率和带宽可以通过数字方式进行控制,从而实现最大的系统灵活性和可重新配置性。 RF采样ADC系列的1.8 GHz奈奎斯特带宽可确保该解决方案可在未来产品中轻松扩展以实现更宽的带宽。

单个直接RF采样ADC可替代整个IF或ZIF采样子系统,以数字方式实现的滤波器和混频器,大大提高了系统的可编程性和可扩展性。这些引脚兼容,从500 MSPS到3.6 GSPS,减少了设计时间和成本,使未来的升级变得简单。

这些都包含在小型开发平台中。这使用TMS320DM6446 DSP片上系统,594 MHz TMS320C64x + DSP内核以及297 MHz ARM926处理器内核和丰富的外设,包括串行端口,USB,EMAC,DDR2 EMIF以及视频端口。 Xilinx的Virtex-4 SX35 FPGA提供额外的硬件处理。 ADS5500,125 MSPS,14位双通道ADC与500 MSPS,16位双通道DAC5687并排,电路板可选择5 MHz或20 MHz通道。其他电路板可堆叠在开发平台上,RF模块工作在360 MHz至960 MHz之间,可选的第二个RF模块可用于全双工操作或覆盖其他频段。

高性能前端 - 结束SDR

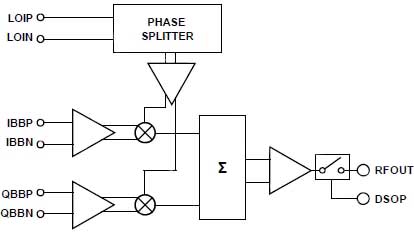

在使用高性能数据转换器时,高性能宽带调制器至关重要。 ADI公司的ADL5375是一款宽带正交调制器,设计工作频率范围为400 MHz至6 GHz。相位精度和幅度平衡可为SDR通信系统提供高性能中频或直接射频调制。

图4:ADL5375宽带正交调制器

硅锗双极架构(图4)提供宽基带带宽以及从450 MHz至3.5 GHz变化不超过1 dB的输出增益平坦度。这些特性加上宽带输出回波损耗≤-12 dB,使ADL5375成为宽带零中频或低中频至射频应用,宽带数字预失真发射机和多频段无线电设计的理想选择。它接受两个差分基带输入和一个单端LO,并产生单端50Ω输出。这两个版本提供500 mV(ADL5375-05)和1500 mV(ADL5375-15)的输入基带偏置电平。

ADL5375可分为五个电路模块:LO接口,基带电压 - 电流(V -to-I)转换器,混频器,差分到单端(D-to-S)级,偏置电路如图5所示。

图5: ADL5375调制器可以分解为五个独立的模块。

LO接口产生两个正交的LO信号。这些信号用于驱动混频器。 I/Q基带输入信号通过V-I级转换为电流,然后驱动两个混频器。这些混频器的输出组合起来为输出平衡 - 不平衡变压器供电,从而提供单端输出。偏置单元为V-to-I级产生参考电流。

LO接口由设置输入阻抗的多相正交分配器和限幅放大器组成。然后,每个正交LO信号通过限幅放大器,为混频器提供有限的驱动信号。

LO输入可以单端驱动或差分驱动。对于3 GHz以上的应用,差分驱动LO输入可能会导致改善的OIP2和LO泄漏。

差分基带输入(QBBP,QBBN,IBBN和IBBP)呈现高阻抗。施加到这些引脚的电压驱动V-to-I级,将基带电压转换为电流。 V到I级的差分输出电流为它们各自的混频器供电。基带输入端的DC共模电压设置两个混频器内核中的电流,并且改变基带共模电压会影响混频器中的电流并影响整体调制器性能。基带共模电压的推荐直流电压为ADL5375-05为500 mVDC,ADL5375-15为1500 mV。

ADL5375有两个双平衡混频器:一个用于同相通道(I通道) )和一个用于正交信道(Q信道)。两个混频器的输出电流相加成一个内部负载。在此负载上产生的信号用于驱动D-to-S级,该级由片上有源平衡 - 不平衡转换器组成,将差分信号转换为单端信号。平衡 - 不平衡转换器为输出提供50Ω阻抗,因此RF输出不需要匹配网络,以便在50Ω环境中实现最佳功率传输。

I/Q调制器设计用于与AD9779A高速DAC轻松连接,因为它们是具有相同偏置电平和类似高信噪比(SNR)的良好匹配器件。 500 mV的匹配偏置电平允许无缝接口,不需要增加噪声和插入损耗以及额外组件的电平转换网络。增加摆幅限制电阻(RSLI,RSLQ)可以在不损失分辨率或0.5 V偏置电平的情况下适当调整DAC摆幅。每个器件的高SNR通过电路保持高SNR。

ADL5375设计用于与ADI系列TxDAC转换器(AD97xx)成员的最小元件接口,以轻松构建SDR系统。 ADL5375的基带输入要求直流共模偏置电压为500 mV,每个AD9779A输出摆幅为0 mA至20 mA,每个DAC输出的单个50Ω电阻接地可提供所需的500 mVDC偏置。只需四个50Ω电阻,每个引脚的电压摆幅为1 VPP。这导致每个输入对上的差分电压摆幅为2 VPP。通过向接口添加电阻RSLI和RSLQ,可以降低DAC的输出摆幅,而不会损失DAC分辨率。电阻器作为差动对的每一侧之间的分流器放置。这样可以在不改变50Ω电阻已经建立的直流偏置的情况下降低交流摆幅。

通常需要对DAC输出进行低通滤波,以在驱动调制器时消除图像频率。上述接口非常适合引入这种滤波器。滤波器可以插在直流偏置设置电阻和交流摆幅限制电阻之间。这样做可以确定滤波器的输入和输出阻抗。

结论

现在可以使用高性能和高度集成的部件,构建软件定义的无线系统变得越来越容易。接收,发送和调制阶段现已集成到可通过外部微控制器控制的灵活单芯片中,或者可以在开发板上无缝地组合更高性能的部件,以加快设计过程。

-

放大器

+关注

关注

143文章

13460浏览量

212433 -

转换器

+关注

关注

27文章

8524浏览量

146253 -

无线

+关注

关注

31文章

5388浏览量

172633

发布评论请先 登录

相关推荐

labview用于通信测试的软件定义无线电架构

如何为我的软件定义无线电接收器架构构建模拟前端?

软件定义无线电的应用

如何构建软件定义的无线系统

如何构建软件定义的无线系统

评论