MCU是许多嵌入式子系统设计中的关键元素,但实现必要的系统功能通常需要额外的功能。也许基于MCU的设计中最受限制的元素之一是片上存储器。越来越多的应用程序需要比MCU可用的系统内存更多的系统内存。特别是,先进的人机界面(HMI)设计可能需要大量的只读图像和音频信息,这些信息不容易存储在MCU片上闪存中。此外,越来越多的应用发现片上RAM过度限制了需要大量数据缓冲和存储的高级通信通道。

本文将快速回顾现代MCU上可用的一些外部存储器接口。这将有助于设计人员更有效地实现需要额外外部存储的基于MCU的系统 - 无论是NVM闪存还是易失性SRAM/DRAM。

SDRAM的外部存储器接口

也许最多扩展存储能力所需的明显外部存储器接口适用于大型工作SRAM。通常,MCU具有相对少量的片上SRAM,并且通常应用将需要比片上可用的更多的工作存储器。例如,高级用户界面可能需要大量缓冲存储器来处理图形用户界面(GUI)和创建视频或音频提示。通常,在存储或传输这些数据文件时使用压缩技术以降低本地存储要求或系统带宽要求。这意味着可能需要大量的工作存储来解压缩这些文件。通常,通信应用或数字信号处理应用中需要大量工作存储器作为缓冲存储器。

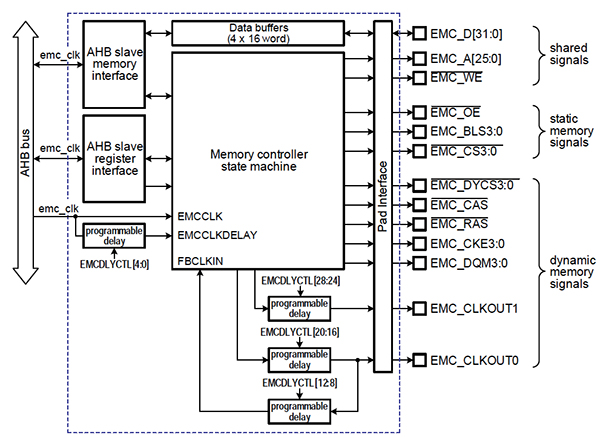

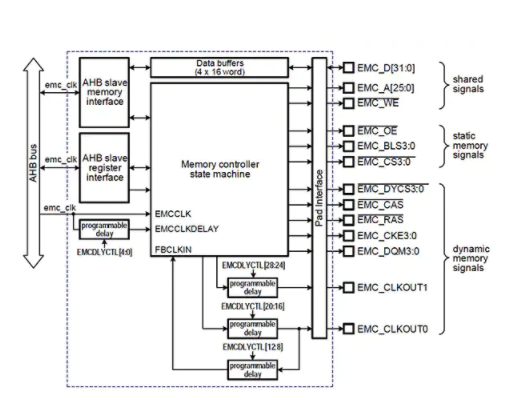

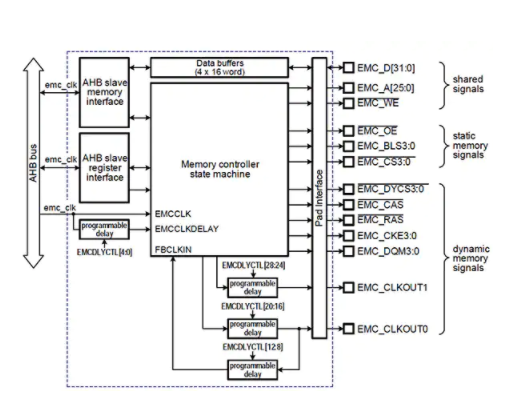

许多MCU为外部存储器接口控制器提供了用于控制外部SDRAM器件的特殊电路。强调支持SDRAM接口的关键硬件元件的示例MCU是恩智浦LPC1787 MCU。外部存储器控制器外设,如图1所示,具有几个可编程延迟元件,用于调整关键SDRAM信号中使用的关键接口信号的时序。例如,可以调整两个潜在SDRAM时钟(CLKOUT1和CLKOUT2)的延迟值,以根据存储器的要求定位转换。此外,另一个可编程延迟调整从存储器读取的数据被采样的时间。这种时序调整及其范围和精度对于简化存储器接口,电路板布局和相关的信号时序检查至关重要。

图1 :恩智浦LPC1787 MCU外部存储器控制器。 (恩智浦提供)

恩智浦LPC1787外部存储器接口还包括几个其他重要的硬件功能,使外部SDRAM接口更高效。例如,框图顶部显示的数据缓冲区可用作读缓冲区,写缓冲区或组合使用。作为写入缓冲区,它们允许对事务进行分组,以最大限度地减少外部写入操作的数量,从而提高系统带宽并降低功耗。作为读缓冲器,它们充当本地数据副本,因此对相同位置的进一步访问可以使用片上缓冲器版本。这减少了外部读取操作的数量,从而提高了系统带宽并降低了功耗。

请注意,NXP内存控制器还支持RAM,ROM和Flash的静态存储器接口。这是大多数现代MCU存储器 - 控制器外设中使用的典型方法,因为大多数硬件在两个应用程序之间都很常见,并且应用程序通常不需要同时使用这两种类型的存储器。

配置外部存储器

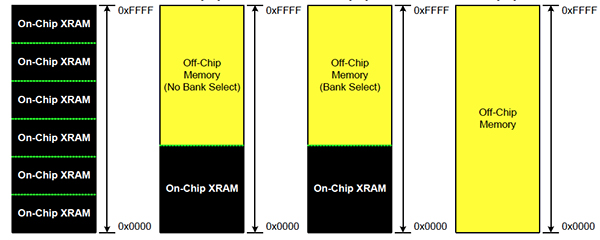

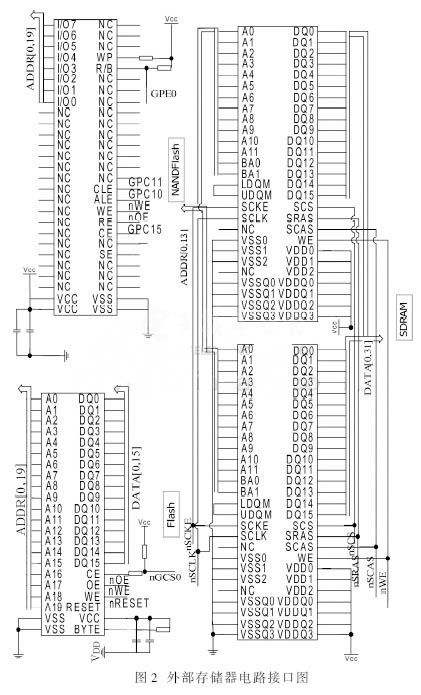

外部存储器通常用于多种用途 - 应用程序不会将其视为存储的单块“块”。用于配置片外存储器块以简化存储器访问的方法有助于简化应用程序编码。 Silicon Labs C8051F70x/71x MCU系列使用了这种技术的一个例子。在该MCU中,使用特殊的MOVX指令访问外部存储器。为了便于将访问组合到片上和片外存储器,可以将片上存储器的一部分映射到外部存储器空间。图2显示了可用于将内部和外部存储器映射到外部存储器地址空间的四种配置模式。在模式1中,如图2的最左侧所示,内部XRAM映射到完整的外部存储器空间,当片上XRAM存储器地址超过片上存储器的数量时,地址“包裹”。当芯片退出复位时,这可能是一种有用的模式,以避免未初始化外部存储器的启动问题。成功配置和测试存储器接口后,可以启用外部存储器空间。如果不使用外部存储器,也可以使用该模式。

图2:Silicon Labs C8051F70x/71x外部存储器配置。 (由Silicon Labs提供)

在模式2和3中,图2中左起第二个和第三个,地址空间在片上和片外访问之间分配。在模式2中,存储体选择不用于将高阶地址位驱动到地址总线上;用户可以控制这些地址值,以提供额外的灵活性。在模式3中,片上存储体地址自动用于驱动外部地址总线,从而提供更简单但不太灵活的方法。在模式4中,在图2的最右侧,片外存储器完全映射到外部地址空间。这使得可以访问在其他地址模式中可能无法访问的外部数据,以充分利用可用内存。如果您的应用程序具有多种不同类型的外部存储器要求 - 代码,数据缓冲区,转换表或音频/视频处理,则可以简化设计,以使用具有地址映射和块访问功能的外部存储器控制器。

外部存储器接口灵活性

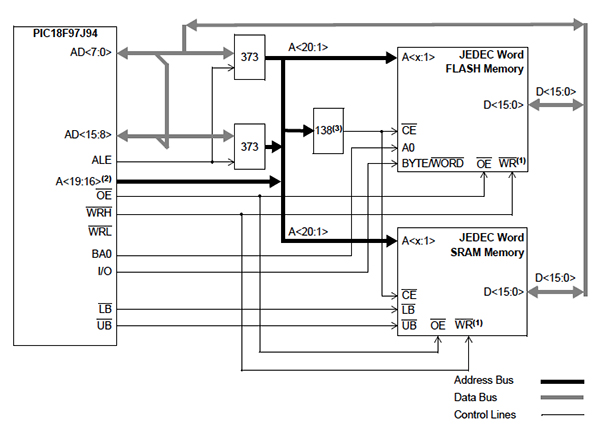

在某些应用中,MCU外部存储器接口支持多种存储器类型同时最小化器件引脚数量至关重要。常见的组合是用于程序存储的Flash和用作工作存储器的SRAM。如果MCU上使用多个存储器接口,则可能会在封装中添加20个或更多引脚,从而增加了成本,功耗和电路板空间要求。一些MCU在外部存储器控制器中提供了额外的灵活性,可以轻松适应各种存储器设备。例如,流行的Microchip PIC18F MCU系列提供了灵活的存储器接口,可以扩展到多种器件类型。图3显示了使用单个外部总线连接标准闪存和标准SRAM的一种方法。在这种情况下,使用一些外部组件(两个373锁存器和一个138解码器)来最小化MCU上使用的引脚数量。 (对于只需要一个373锁存器的8位接口,也可以实现更简单的实现)。具有这种灵活性的外部存储器接口允许“保存的”IO用于其他功能,最大化引脚效率,这是基于MCU的设计中最重要的元素之一。

图3:Microchip PIC18F MCU外部存储器接口框图。 (由Microchip Technology提供)

接口时序灵活性

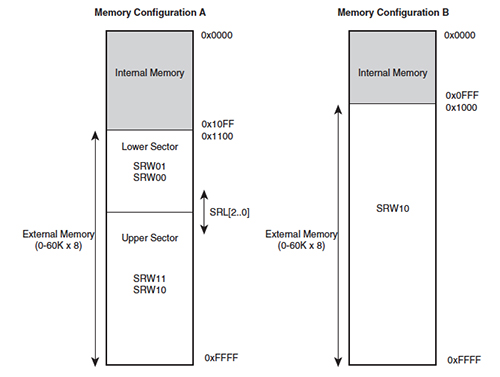

除IO互连灵活性外,外部接口通常还需要一定的时序灵活性。例如,如果内存慢于MCU时钟周期,则可能需要插入等待状态。理想情况下,可以为不同的外部存储器块分配不同的等待状态特性。当外部接口不仅可用于标准存储器而且可用于存储器映射器外设(如液晶显示器,模数转换器和数模转换器)时,此功能更为重要。 Atmel ATmega MCU系列可以为外部存储器空间分配两个不同的等待状态值。如下面的图4所示,存储器配置A允许外部存储器被分成两个扇区 - 上部扇区和下部扇区。扇区大小可以有八个不同的值之一,以0x2000为增量从0x2000到0xE000调整上段和下段之间的分界线。

图4:Atmel ATmega64外部存储空间。 (由Atmel提供)

将外部存储器空间划分为两个扇区可以轻松地将具有较大等待状态值的设备和具有较小等待状态值的设备组合在一起。也许最重要的是,如果零等待状态存储器用于频繁访问的程序数据,即使较慢的设备共享相同的存储器总线,也可以使用零等待状态值。这样可以最大限度地降低MCU引脚要求,同时提高性能并节省功耗。

结论

MCU有时需要使用外部存储器接口扩展可用的片上存储器。了解这些接口的功能可以缩短设计时间,降低成本并提高系统性能。

-

mcu

+关注

关注

146文章

17113浏览量

350901 -

嵌入式

+关注

关注

5082文章

19100浏览量

304622 -

存储器

+关注

关注

38文章

7481浏览量

163751

发布评论请先 登录

相关推荐

基于MCU系统的外部存储器接口配置

详解多功能双接口存储器方案

一种基于TI新一代MSP430FR系列MCU的多功能双接口存储器设计

基于DSP的存储器接口宽度调节设计

怎么使用AT32 MCU的SPIM作为外部存储器的扩展功能

如何选择DSP芯片的外部存储器?

外部存储器电路接口电路图

扩展MCU功能时,明智地使用外部存储器接口

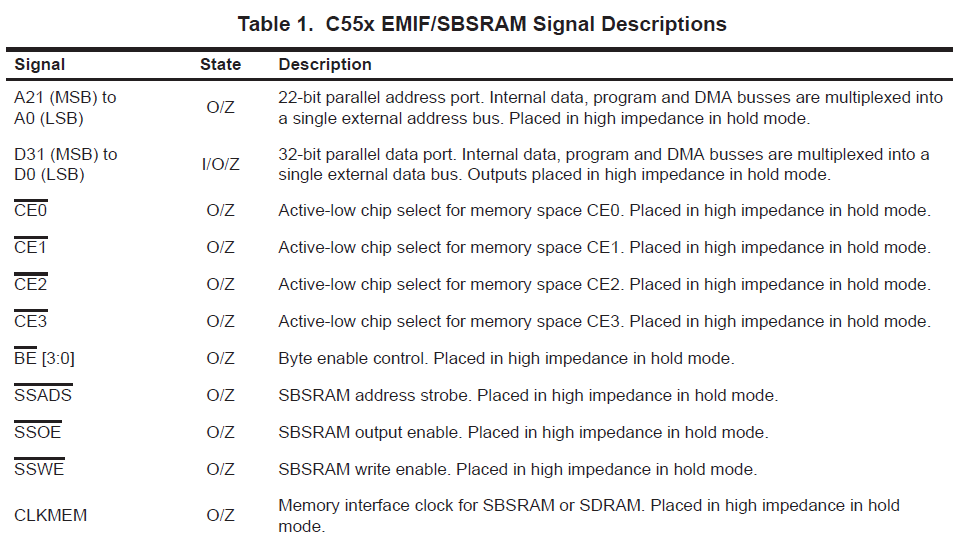

TMS320VC5510外部存储器接口于SBSRAM的系统级连接和寄存器配置概述

外部存储器有哪些

使用低内存MSP430™ MCU的带备份存储器的外部RTC

基于MCU外部存储器接口的系统设计

基于MCU外部存储器接口的系统设计

评论