在由北京未来芯片技术高精尖创新中心和清华大学微电子学研究所联合主办的第三届未来芯片论坛上,清华大学正式发布了《人工智能芯片技术白皮书(2018)》。

《白皮书》首次整合了国际化的学术和产业资源,紧扣学术研究和产业发展前沿,对人工智能芯片技术进行了深入探讨、专业阐述,完成了对AI芯片各种技术路线梳理及对未来技术发展趋势和风险预判。

据悉,《白皮书》由斯坦福大学、清华大学、香港科技大学、***新竹清华大学,北京半导体行业协会及新思科技的顶尖研究者和产业界资深专家,包括10余位IEEE Fellow共同编写完成。

无芯片不AI,新计算范式来袭

近些年随着大数据的积聚、理论算法的革新、计算能力的提升及网络设施的发展,使得持续积累了半个多世纪的人工智能产业,又一次迎来革命性的进步,人工智能的研究和应用进入全新的发展阶段。

实际上,人工智能产业得以快速发展,都离不开目前唯一的物理基础——芯片。可以说,“无芯片不AI”。

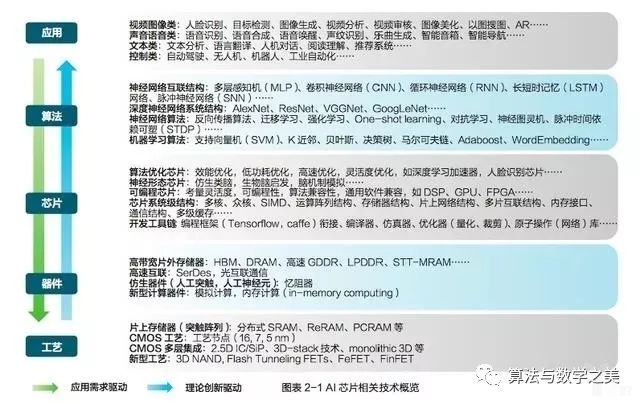

目前,关于AI芯片的定义没有一个严格和公认的标准。较为宽泛的看法是面向人工智能应用的芯片都可以称为AI芯片。具体来说,报告中探讨的AI芯片主要分为三类,一是经过软硬件优化可高效支持AI应用的通用芯片,如GPU;二是侧重加速机器学习(尤其是神经网络、深度学习)算法的芯片,这也是目前AI芯片中最多的形式;三是受生物脑启发设计的神经形态计算芯片。

AI芯片的计算既不脱离传统计算,也具有新的计算特质,主要特点有三:处理内容往往是非结构化数据,如视频、图像及语音等,需要通过样本训练、拟合基环境交互等方式,利用大量数据来训练模型,再用训练好的模型处理数据;处理过程需要很大的计算量,基本的计算主要是线性代数运算,大规模并行计算硬件更为适合;处理过程参数量大,需要巨大的存储容量,高带宽、低延时的访存能力,及计算单元和存储器件间丰富且灵活的连接。

AI芯片的新计算范式,也为芯片提出了处理非结构化数据、计算量大及存储和计算间的访问连接等新问题。

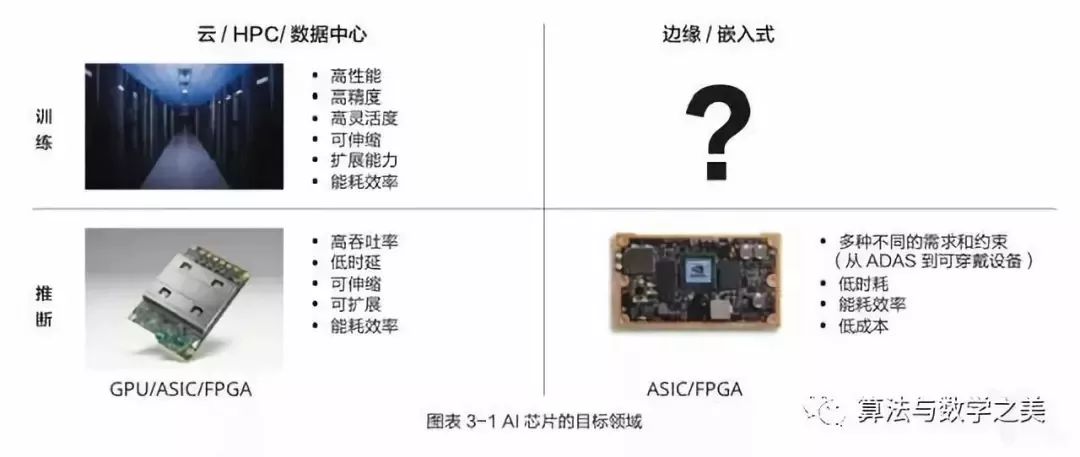

AI芯片发展现状:云、边结合

在应用场景上,AI芯片的应用主要分为云端和终端,以深度学习的算法来说,云端人工智能硬件负责“训练+推断”,终端人工智能硬件负责“推断”,因而终端的计算量更小,相对没有传输问题。但从自动驾驶、智慧家庭,到loT设备等,速度、能效、安全和硬件成本等是重要因素。

云端AI计算:目前各大科技巨头纷纷在自有云平台基础上搭载人工智能系统,主要有IBM的waston、亚马逊的AWS、以及国内的阿里云、百度云平台等。其中英伟达的GPU采用更为广泛,赛灵思、英特尔、百度等厂商也在积极采用FPGA在云端进行加速,一些初创公司,如深鉴科技等也在开发专门支持 FPGA 的 AI 开发工具。另外,除GPU和FPGA外,AI领域专用架构芯片ASIC则因其更好的性能和功耗,成为云端领域新的搅局者,如谷歌的TPU。

边缘AI计算:随着人工智能应用生态的爆发,越来越多的AI应用开始在端设备上开发和部署。

智能手机是目前应用最为广泛的边缘计算设备,包括苹果、华为、高通、联发科和三星在内的手机芯片厂商纷纷推出或者正在研发专门适应 AI 应用的芯片产品。另外,也有很多初创公司加入这个领域,如地平线机器人、寒武纪、深鉴科技、元鼎音讯等。传统的IP 厂商,包括 ARM、Synopsys 等公司也都为包括手机、智能摄像头、无人机、工业和服务机器人、智能音箱以及各种物联网设备等边缘计算设备开发专用 IP 产品。

自动驾驶是未来边缘AI 计算的最重要应用之一,MobileEye SOC 和 NVIDIA Drive PX 系列提供神经网络的处理能力可以支持半自动驾驶和完全自动驾驶。

目前云和边缘设备在各种AI应用中往往是配合工作。最普遍的方式是在云端训练神经网络,然后在云端(由边缘设备采集数据)或者边缘设备进行推断。

AI芯片的技术挑战:冯·诺依曼、CMOS工艺和器件瓶颈

由于前文所述的AI芯片需要满足高效的数据访问,以及深度学习下的新的计算范式,AI芯片在发展上,也遇到了一些瓶颈问题,特别是冯·诺依曼瓶颈,及CMOS工艺和器件瓶颈。

冯·诺依曼瓶颈:在传统“冯·诺依曼架构”中,计算模块和存储单元互相分离,数据从处理单元外的存储器提取,处理完之后再写回存储器。每一项任务,如果有十个步骤,那么CPU会依次进行十次读取、执行,再读取、再执行,这就造成了延时,以及大量功耗花费在了数据读取上。

可以不夸张地说,大部分针对AI,特别是加速神经网络处理而提出的硬件架构创新都是在和这个问题做斗争。概括来说,目前的解决思路包括减少访问存储器的数量,降低访问存储器的代价。

CMOS工艺和器件瓶颈:目前,人工智能,特别都是机器学习的发展将需要更有力的、超过每秒百亿次运算能力的计算系统,而构建这些系统的基础是CMOS技术的芯片,而CMOS工艺能不断提高系统性能主要得益于集成尺寸的缩小。过去30年,摩尔定律很好预测了这种计算进步,但由于基础物理原理限制和经济的原因,持续提高集成密度变得越来越困难。

目前的解决方案是通过开发提供大量存储空间的片上存储器技术,并探索利用片上存储器去构建未来的智能芯片架构。另外,近年来,可以存储模拟数值的非易失性存储器发展迅猛,能同时具有存储和处理数据能力,可以破解传统计算体系结构的一些基本限制,有望实现类脑突触功能。

AI芯片架构设计趋势:云端、边缘设备、软件定义

而针对以上AI芯片计算和应用上的需求,目前云端和边缘设备的AI芯片都在进行新的研发。

AI云端训练和推断:大存储、高性能、可伸缩。从英伟达和谷歌的设计实践可以看出云端AI芯片在架构层面,技术发展的几个特点和趋势:存储的需求(容量和访问速度原来越高);处理能力推向每秒千万亿,并支持灵活伸缩和部署;专门针对推断需求的FPGA和ASIC。

边缘设备:目前,衡量AI 芯片实现效率的一个重要指标是能耗效率——TOPs/W,这也成为很多技术创新竞争的焦点。

其中,降低推断的量化比特精度是最有效的方法;除降低精度外,提升基本运算单元MAC的效率还可以结合一些数据结构转换来减少运算量;另一个重要的方向是减少对存储器的访问,如把神经网络运算放在传感器或存储器中;此外,在边缘设备的AI芯片中,也可以用各种低功耗设计方法来进一步降低整体功耗。最后,终端设备AI芯片往往呈现一个异构系统,专门的AI加速器和CPU、GPU、ISP、DSP等协同工作以达到最佳效率。

软件定义芯片:通用处理器如CPU、GPU,缺乏针对AI算法的专用计算、存储单元设计,功耗大;专用芯片ASIC功能单一;现场可编程阵列FPGA重构时间开销过大,且过多的冗余逻辑导致其功耗过高。以上传统芯片都难以实现AI芯片所需要的“软件定义芯片”。

可重构计算技术允许硬件架构和功能随软件变化而变化,具备处理器的灵活性和专用集成电路的高性能、低功耗,是实现“软件定义芯片”的核心,被公认为是突破性的下一代集成电路技术,清华大学的AI芯片Thinker目前采用可重构计算框架,支持卷积神经网络、全连接神经网络和递归神经网络等多种AI算法。

AI芯片中的存储技术、新兴计算技术及神经形态芯片

如前所述,提高AI芯片的性能和能效的关键之一在于数据访问。而在传统的冯·诺依曼体系结构中,数据从存储器串行提取并写入到工作内存,导致相当长的延迟和能量开销。

近期,面向数字神经网络的极速器(GPU、FPGA和ASIC)迫切需要AI友好型存储器;中期,基于存内计算的神经网络可以为规避冯·诺依曼瓶颈问题提供有效的解决方案;后期,基于忆阻器的神经形态计算可以模拟人类的大脑,是AI芯片远期解决方案的候选之一。

而对应的新兴计算技术包括近内存计算、存内计算,以及基于新型存储器的人工神经网络和生物神经网络。

神经形态芯片,即“仿生电脑”。如前所说,对于冯·诺依曼、CMOS工艺和器件瓶颈形成的AI芯片存储、计算间的问题,神经形态计算是一种新的路径。

近些年,神经形态计算也用来指采用模拟、数字、数模混合VLSI以及软件系统实现的神经系统模型。其将数字处理器当作神经元,把内存作为突触,内存、CPU和通信部件完全集成在一起,采用模拟人脑神经元结构来提升计算能力。每个神经元计算都是本地的,且从全局来看神经元们是分布式在工作。受到脑结构研究的成果启发,研制出的神经形态芯片具有低功耗、低延迟、高速处理、时空联合等特点。

人工智能的未来:算法、架构、器件的不断探索

“未来能否有一个终极算法来实现通用人工智能?”这个问题还没有人能给出肯定的答案。芯片是人工智能算法的物理基础,它与算法唇齿相依。如果能有统一的终极算法出现,那么我们很可能会看到一个终极芯片出现。

但在未来很长一段时期,不同的应用仍然需要不同的算法(也包括传统算法),因此我们还必须探索不同的架构,探索新的器件甚至材料。随着底层芯片技术的进步,人工智能算法也将获得更好的支持和更快的发展。

CMOS 技术与新兴信息技术的交叉融合,开源软件到开源硬件的潮流渐显,预示着将迎来一个前所未有的协同创新机遇期。

-

人工智能

+关注

关注

1791文章

46877浏览量

237615 -

深度学习

+关注

关注

73文章

5493浏览量

120983 -

AI芯片

+关注

关注

17文章

1860浏览量

34912

原文标题:清华发布《AI芯片技术白皮书》:新计算范式,挑战冯诺依曼、CMOS瓶颈

文章出处:【微信号:wwzhifudianhua,微信公众号:MEMS技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

清华大学正式发布了《人工智能芯片技术白皮书(2018)》

清华大学正式发布了《人工智能芯片技术白皮书(2018)》

评论