UART(串口)收发模块设计- 02

整体架构回顾

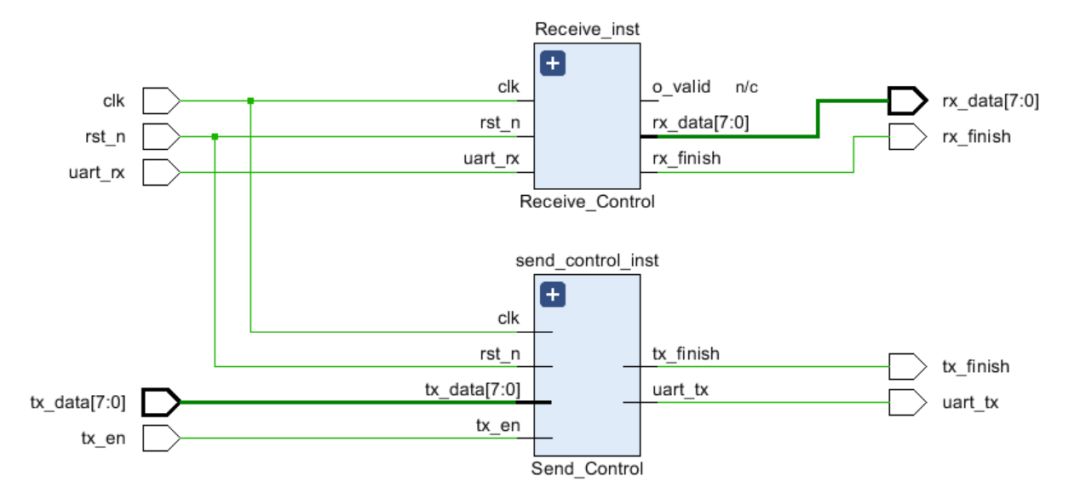

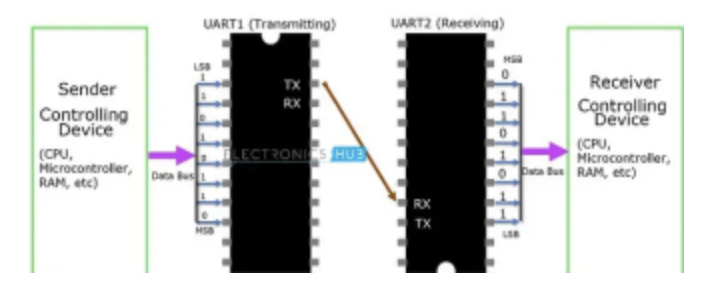

整体结构如下图,整个UART有两个大模块,一个接收模块,一个发送模块。具体大家可以回顾文章《UART(串口)收发模块设计- 01》。

波特率时钟产生模块

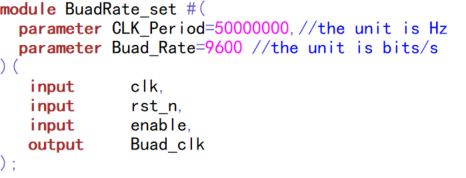

收发模块里面都有一个波特率时钟产生模块BuadRate_set,用于将系统时钟clk进行分频,得到波特率时钟Buad_clk,以控制数据的收发。

端口如下,通过CLK_Period指定当前的clk时钟频率,比如50M,则为50000000。Buad_Rate为设定的波特率。

主要设计代码如下,通过localparam DIV_PEREM指定分频计数值。分频计数器为cnt,当enable为高时,cnt开始循环的从0递增到DIV_PEREM。Buad_clk在每次cnt==DIV_PEREM的时候就翻转一次,从而得到clk时钟的CLK_Period/Buad_Rate倍分频。

数据接收模块

状态机:数据接收模块通过一个状态机来控制。状态机的跳转由波特率时钟下降沿控制。波特率时钟Buad_clk起始为高电平。

IDLE:其中IDLE为空闲状态,只有当检测到起始位的时候,才进入GET_DATA。

GET_DATA:在GET_DATA状态下获得8位数据位数据,通过一个计数器来计数接收到的数据位数。当cnt为‘d7时表明接收到了8位数据,便跳到最后一个状态END_BIT。

END_BIT:等待停止位的到来,然后回到IDLE状态,完成数据的接收。

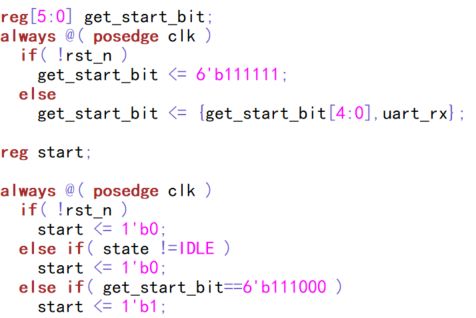

起始位的检测:其实就是在IDLE状态下,检测uart_rx的下降沿,如下代码所示。将uart_rx通过一个6bit的移位寄存器get_start_bit(uart_rx从低bit往高bit移动),那么当get_start_bit的,高3bit都为1,低3bit为0时,表明uart_rx出现了下降沿,此时将start拉高,以便启动状态机和波特率时钟产生模块BuadRate_set。

数据的接收:在GET_DATA状态下,由波特率时钟的下降沿控制,将uart_rx往一个8bit的移位寄存器送,uart_rx从高bit向低bit流动(由于串口发送是先发低位数据)。

数据发送模块

状态机:数据接收模块通过一个状态机来控制。状态机的跳转由clk时钟上升沿控制。

IDLE:IDLE为空闲状态,当检测到tx_en(发送使能信号)为高,则进入EN_TX模块。

EN_TX:在EN_TX模块发送10bit数据(起始位,数据位,停止位)。数据的发送由波特率时钟Buad_clk上升沿控制。如下代码,在cnt为0时将tx_data(待发送的数据位)与起始位(0),装载到data_to_send中,然后对data_to_send做从高位向低位的移位操作,高位填1。将data_to_send的最低位接uart_tx,发送出去。利用cnt计数发送的位数。

上板实测

这里设计了一个实测设计(UART_TEST),功能如下:

上电复位后,通过串口向上位机发送数据8'h34,然后只要收到上位机发送过来的数据,就将其返回给上位机。

大家可以把源码下下来,自己新建工程,结合开发板上板测试一下。

文件里面提供了一个PC端串口调试上位机SSCOM。大家在上板测试时,需要一个USB转串口器(有的开发板上集成了这个),使得板子的串口可以通过USB端口与PC上位机通信。

-

寄存器

+关注

关注

31文章

5336浏览量

120260 -

计数器

+关注

关注

32文章

2256浏览量

94485 -

时钟

+关注

关注

10文章

1733浏览量

131461

原文标题:UART(串口)收发模块设计- 02

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

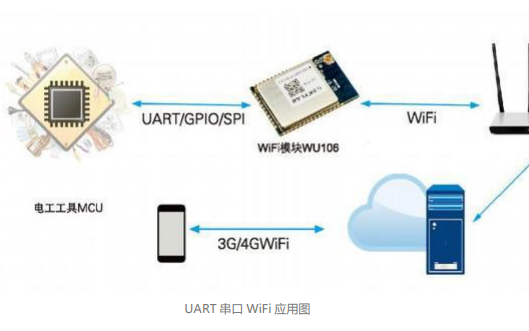

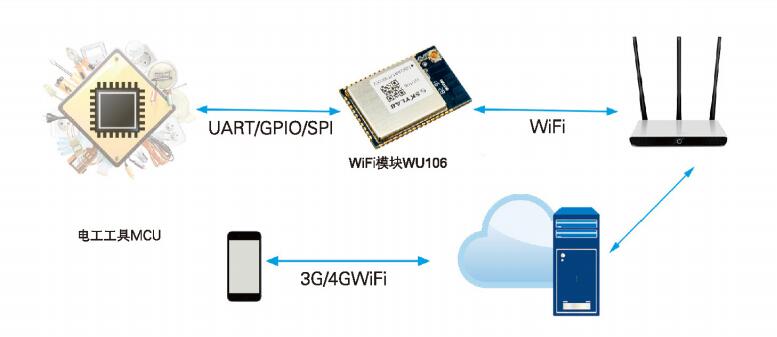

Iot物联网UART串口WiFi模块及智能插座wifi模块解决方案

物联网UART串口WiFi模块及智能插座方案app界面介绍

uart是什么意思?认识uart串口

ESP8266方案小尺寸、UART串口WiFi模块规格书下载.pdf

UART串口WiFi模块的工作原理及应用

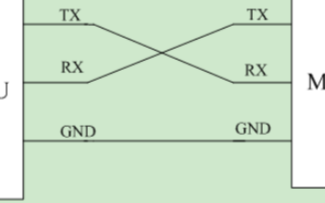

串口、COM口、UART口, TTL、RS-232、RS-485区别详解

SKYLAB UART串口WiFi模块改进无线控制设计—简化设计

【CubeIDE】STM32 HAL库史上最详细教程(一):UART串口收发

串口、COM口、UART口和TTL、RS-232、RS-485介绍

UART(串口)收发模块设计

UART(串口)收发模块设计

评论