尽管围绕着可制造性设计(DFM)的价值、定义、变化性和技术争执颇多,但所有的问题都是基于芯片。当然,当我们开始考虑45和32纳米设计时,芯片DFM是很关键的要求。然而,关注芯片DFM,却忽视了更重要的技术需要:面向印刷电路板的DFM。

我们都知道即使硅片百分之百完美,如果芯片到芯片通信链接的任何一个元件(比如封装,连接头或电路板)损坏,目标系统可能仍然不能正常工作。许多封装、连接器和PCB供应商也许被系统设计师追逼着控制他们的加工容差。

但是,除非所有供应商一致加强规范,例如一个有正负5%容差的连接器对PCB正负10%容差的系统可能收效不大。为了优化系统设计,设计师需要研究每个元件的因果关系。迄今为止,我们没有DFM工具来处理诸如此类的设计问题。

在预布局设计阶段,高速系统或信号完整性工程师通常只能进行有限的Spice仿真。为确保系统工作正常,需要对能覆盖所有加工容差的边界情形进行仿真。

例如,PCB内的金属线宽变化、介电堆叠高度、介电质常数和损耗正切值全部都能影响阻抗和衰减。然而,仅有较大规模公司的工程师才可能有资源来定制自有的脚本,来进行上千次仿真工作,然后再对结果进行处理。即便这样,对哪种变量进行扫描仍然没有定义完好的标准。

最明显缺乏的是封装和连接器的边界模型。对于高速设计,这些模型只能通过与频率相关的S参数来精确定义。然而,极少有供应商提供好的S参数模型,更不用说在宽范围频率内的边界模型了。

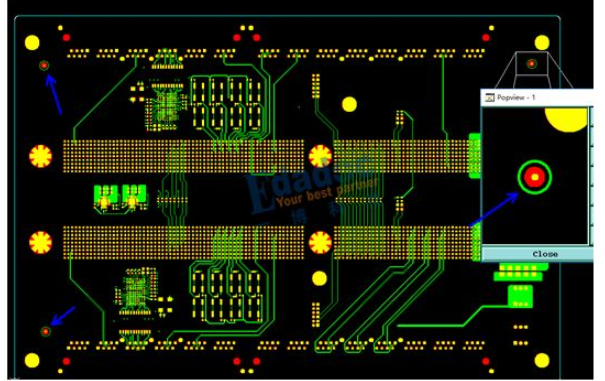

在后布局验证阶段,需要进行复杂PCB的精确提取和仿真,以计算详细的转角和弯曲。可是,几乎没有工具可用。

很明显,需要通用的PCB设计和验证方法。那么,我们需要些什么呢?

让我们关注两大领域。对预布局设计,举例来说,最好有GUI驱动的线路图输入编辑器,使设计师能容易地输入每个元件的变化,仿真并处理结果,报告每个变量的产生和影响。

对后布局验证,DFM工具需要能自动调整版图以覆盖边界情形,采用快速的全波提取器来提取寄生参数,在电路仿真中用I/O晶体管边界模型仿真。

只有当设计师在设计和验证内都考虑了工差,他们才能说做了可制造性设计。只有当工具供应商认识到芯片只是子系统——比如PCB——的一部分,那么DFM最终才能与开发终端产品的客户真正相关起来。

-

芯片

+关注

关注

457文章

51342浏览量

428145 -

pcb

+关注

关注

4329文章

23187浏览量

400487 -

DFM

+关注

关注

8文章

465浏览量

28419

原文标题:DFM不应局限于芯片,PCB更需要它

文章出处:【微信号:circuit-ele,微信公众号:PCB工艺技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DFM除了应用在芯片上还可以应用在哪了吗PCB更需要

DFM除了应用在芯片上还可以应用在哪了吗PCB更需要

评论