2.5D异构和3D晶圆级堆叠正在重塑封装产业。

堆叠:一种摩尔定律以外的高度集成替代方案

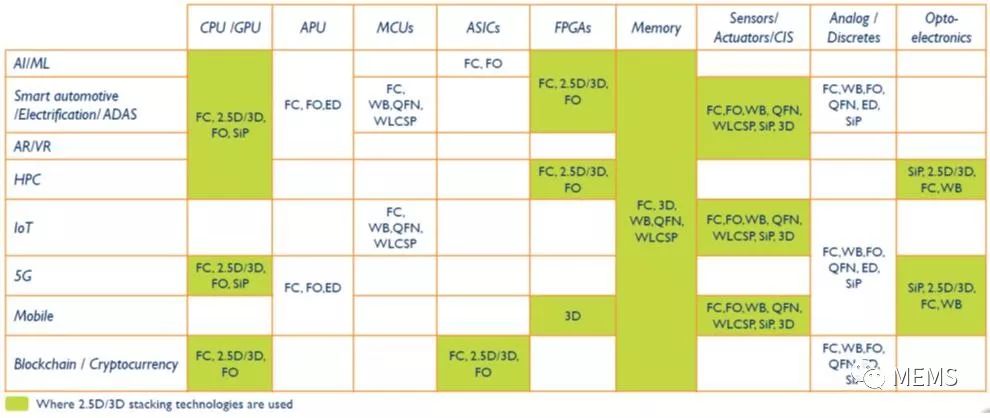

摩尔定律的放缓,为满足行业大趋势严格指标要求的新发明开辟了道路。在封装领域,许多半导体厂商倾向于2.5D和3D堆叠技术,而硅通孔(TSV)是最早的堆叠技术之一。经过数年的发展和对MEMS的关注,它最终进入了许多应用领域。如今,2.5D和3D堆叠技术已成为能够满足当前人工智能(AI)和数据中心等应用性能需求的唯一解决方案。堆叠技术已被应用于高、中、低端市场的各种硬件,包括3D堆叠存储、图形处理单元(GPU)、现场可编程门阵列(FPGA)和CMOS图像传感器(CIS)等。

各种应用中先进堆叠封装技术的市场机遇

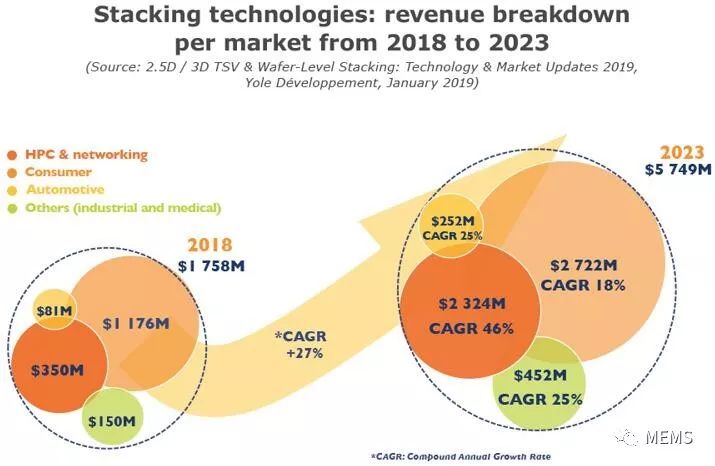

高带宽存储(HBM)和CMOS图像传感器等硬件占据了TSV市场的大部分营收。堆叠技术整体市场规模将在2023年超过55亿美元,在此期间的复合年增长率(CAGR)可达27%。对于目前来说,消费类市场是最大的细分市场,其市场份额超过了65%。但矛盾的是,这并不意味着消费类市场就是这些技术的主要驱动因素。事实上,高性能计算(HPC)是堆叠技术的真正驱动因素,在2019~2023年期间将呈现最快的增长速度,市场份额预计将从2018年的20%增长到2023年的40%,就封装营收而言,这相当于2018年营收的6倍以上增长。相应的,消费类市场份额将减少,而汽车、医疗和工业等其他市场将维持目前的市场份额。

2018~2023年按市场细分的堆叠技术营收

从TSV到晶圆级堆叠,封装技术正在蓬勃发展

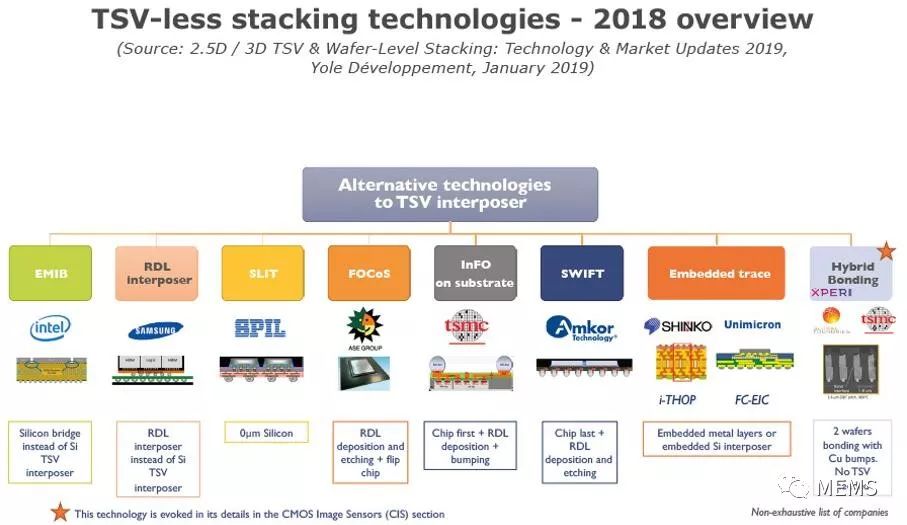

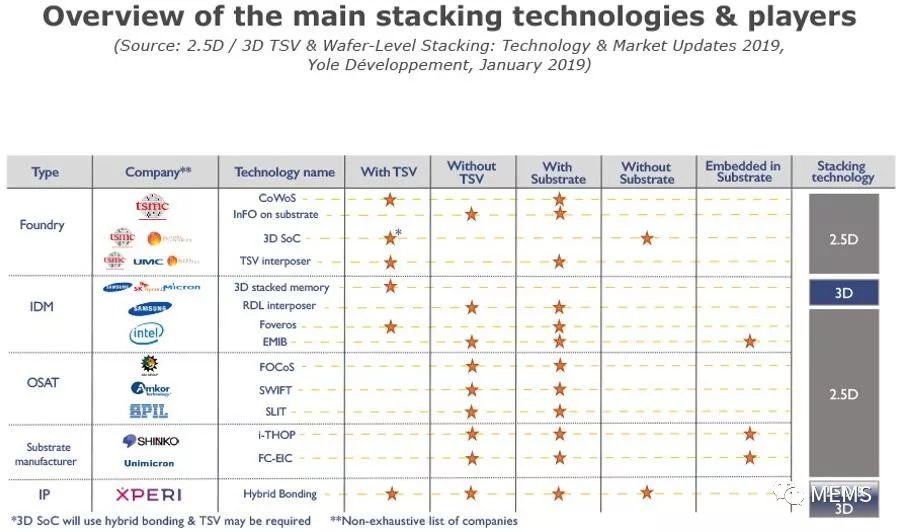

由于堆叠技术竞争主要集中在“TSV”和“无TSV(TSV-less)”之间进行,因此Yole在本报告中针对这两类技术进行了分析。

对于目前的高端市场,市场上最流行的2.5D和3D集成技术为3D堆叠存储TSV,以及异构堆叠TSV中介层。Chip-on-Wafer-on-Substrate(CoWos)技术已经广泛用于高性能计算应用,新的TSV技术将于2019年上市,即来自英特尔(Intel)的Foveros(基于“有源”TSV中介层和3D SoC技术,具有混合键合和TSV互连(可能)技术)。Foveros的出现表明,虽然“TSV”受到了来自“无TSV”技术的挑战,但厂商仍然对它很有信心。

我们不能忽视“无TSV”技术在市场上的兴起。这些创新可以划分为“带基板型(with substrate)”和“嵌入基板(embedded in substrate)”两组。嵌入式多芯片互连桥接(EMIB)技术已经商业化,是“嵌入基板”组的一种,其Si桥在基板中较深的位置。其他基板技术也正在开发中,但仍未上市,例如集成薄膜高密度有机封装(I-THOP)和倒装芯片-嵌入式中介层载具(FC-EIC)等。

左边是业界标准2.5D封装的芯片,右边是英特尔EMIB封装的芯片

图片来源:《英特尔嵌入式多芯片互连桥接(EMIB)》

“带基板型”技术也用于TSV替代,例如基板上集成扇出型封装(InFO),它广泛用于苹果公司(Apple)的处理器。此外,再分配层(RDL)中介层技术目前正在开发中,预计将在2020年上市。最后同样需要注意的是,基板上扇出型芯片(Fan Out Chip on Substrate, FOCoS)于2016年开发并商业化,但似乎订单并不多。

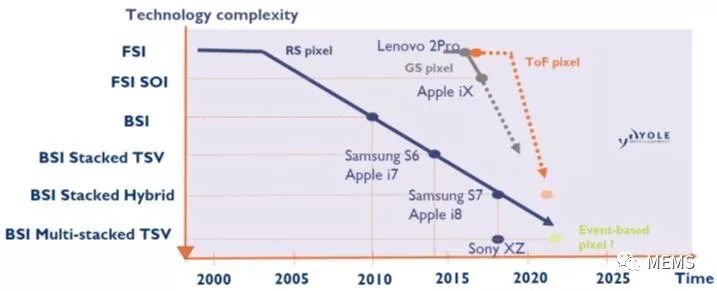

堆叠技术赋能的CMOS图像传感器发展路线图

混合键合技术可以桥接“TSV”/“无TSV”这两个主要技术类别。这项技术的独特之处在于它可以同时成为TSV技术的挑战者和支持者。自2016年以来,它一直被用于智能手机的CMOS图像传感器,并且在不久的将来,它将作为一种互连解决方案整合存储和2.5D高端市场。

2018年“无TSV”堆叠技术概览

谁在支持并投资堆叠技术?

各类不同的市场参与方都希望在不断增长的55亿美元堆叠市场中占有一席之地,目前主要有四种商业模式在堆叠业务领域参与竞争:代工厂、集成器件制造商(IDM)、外包半导体封测厂商(OSAT)和IP厂商。

据麦姆斯咨询介绍,台积电(TSMC)、联华电子(UMC)和格芯(GlobalFoundries)等晶圆代工厂,主导了TSV异构堆叠技术,因为它们有能力自己生产中介层。拥有“Foveros”技术的英特尔,是唯一一个试图在这个领域参与竞争的IDM。

对于3D堆叠存储,竞争主要在IDM“三巨头”三星(Samsung)、SK海力士(SK Hynix)和美光(Micron)之间,这些公司将继续统治堆叠存储市场。

同时,3D SoC是一种代工技术,很可能只有一家代工厂会生产它,以确保高良率并控制风险。在这方面,台积电在上市时间的竞争中领先于格芯。

对于“无TSV”技术,竞争主要存在于代工厂、IDM、OSAT和基板制造商之间。三星、英特尔和台积电等厂商,都参与了“有”和“没有”TSV技术的开发。2016年,OSAT巨头日月光(ASE)向市场引入了FOCoS技术,而安靠(Amkor)等其他厂商也已经开发出了合适的技术,但仍然在等待订单中。

日本新光(Shinko)、欣兴电子(Unimicron)以及最近的富士通互连科技(Fujitsu Interconnect)等基板公司,仍然在研发中。IP厂商Xperi的混合键合技术处于“有TSV”和“无TSV”技术之间,预计将对市场产生积极影响。Xperi的另一个优势是其技术兼容高端和中/低端细分市场。

代工厂、IDM和IP厂商相比OSAT在堆叠技术方面有优势,因为后者在获得订单方面有困难。

主要堆叠技术及厂商概览

-

摩尔定律

+关注

关注

4文章

634浏览量

79079 -

图像传感器

+关注

关注

68文章

1904浏览量

129581 -

堆叠

+关注

关注

0文章

35浏览量

16607

原文标题:《2.5D/3D硅通孔(TSV)和晶圆级堆叠技术及市场-2019版》

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用于扇出型晶圆级封装的铜电沉积

2.5D/3D芯片-封装-系统协同仿真技术研究

日本计划量产2nm芯片,着眼于2.5D、3D封装异构技术

3D封装结构与2.5D封装有何不同?3D IC封装主流产品介绍

2.5D异构和3D晶圆级堆叠正在重塑封装产业

2.5D异构和3D晶圆级堆叠正在重塑封装产业

评论