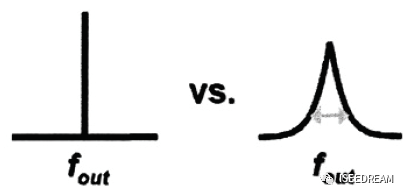

相位噪声就是信号在相位上的噪声。准确的讲是指时钟信号相对于其载波频率的频率成分的变化量,它是关于载波频率偏移量的函数。相位噪声是时钟抖动的频域表示,图下图所示为相位噪声示意图。

时钟抖动

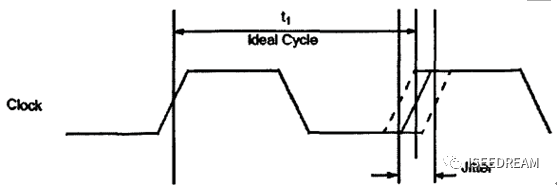

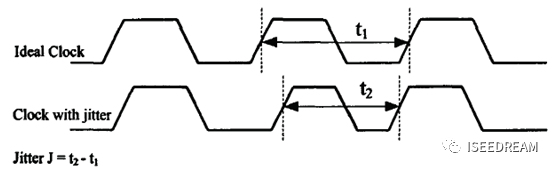

时钟抖动是指实际输出时钟信号相对于理想信号任何相应边沿偏移的时间长度。而实际的跳变沿可以超前或者滞后其理想位置.一般可以用时间的绝对值或者频率的百分比作为抖动的衡量单位。下图所示为时钟抖动示意图。

导致抖动的原因有电源噪声,晶体管的热噪声和闪烁噪声,村底噪声以及输入时钟信号的反射和EMI等。时钟抖动时相位噪声的时域表示。

抖动一般分为三类:相位抖动,周期抖动和周期.周期抖动,且不同类型抖动的特性和测量方法均不同。

相位抖动

相位抖动是指实际输出时钟信号的跳变沿偏离其理想位置的时间长度,它可以用频谱分析仪来测量。下图所示为相位抖动定义的示意图。

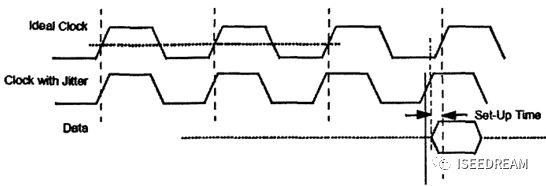

这种抖动很重要,在基于微处理器的系统中,处理嚣需要2ns的数据建立时间,如果驱动时钟的相位抖动最大值是2 5ns时,时钟的上升沿有可能在数据有效前进行采样,那么就采样到错误的数据,如下图所示。

周期抖动

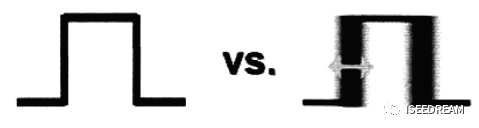

周期抖动是指实际时钟信号的周期同理想时钟周期的差值。它可以被任何示波器测量到。这种抖动是很重要,因为它定义了输出时钟频率的最大和最小值,即时钟周期的最大和最小值。下图所示为周期抖动定义的示意图。

周期-周期抖动

周期-周期抖动是指输出时钟信号当前周期同前一个周期大小的差值,这种抖动很难测量,需要时序间隔分析器(Timing Interval Analyzer)测量。下图为周期-周期抖动定义的示意图,Jl和J2是测量的抖动值。

PLL工作状态

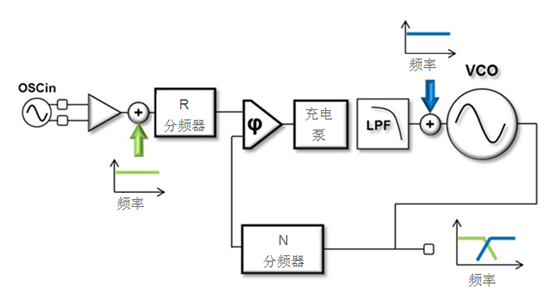

锁相环有四种工作状态,即锁定状态、失锁状态、捕获过程和跟踪过程。

(1)锁定状态:整个环路已经达到输入信号相位的稳定状态。它指输出信号相位等于输入信号相位或者是两者存在一个固定的相位差,但频率相等。在锁定状态时,压控振荡器的电压控制信号接近平缓。

(2)失锁状态:环路的反馈信号与锁相环输入信号的频率之差不能为零的稳定状态,或是在无限时间范围内不停振荡无法达到锁定的状态,它们都称为失锁状态。当环路的结构设计有问题,或者是输入信号超出了锁相环的应用范围的时候都会进入失锁状态。这个状态意味着环路没有正常工作。

(3)捕获过程:指环路由失锁状态进入锁定状态的过程。这个状态表明环路已经开始进入正常工作,但是还没有达到锁定的稳态。此过程应该是一个频率和相位误差不断减小的过程。

(4)跟踪过程:是指在PLL环路处于锁定状态时,若此时输入信号频率或相位因其它原因发生变化,环路能通过自动调节,来维持锁定状态的过程。由于输入信号频率或者相位的变化引起的相位误差一般都不大,环路可视作线性系统。

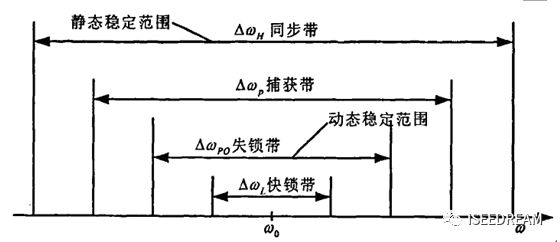

一般用四个参数指标来描述PLL的系统频带性能:

(1)同步带:它指的是环路能保持静态锁定状态的频率范围。当环路锁定时,逐步增大输入频率,环路最终都能保持锁定的最大输入固有频差。

(2)失锁带:锁相环路稳定工作时的动态极限。也就是说PLL在稳定工作状态时,输入信号的跳变要小于这个参数,PLL才能快速锁定。若输入信号的跳变大于该参数而小于捕捉带,则环路还是能锁定,但是需要较长的时间。

(3)捕获带:只要反馈信号和输入信号的频差在这一范围内,环路总会通过捕获而再次锁定,随着捕获过程的进行,反馈信号的频率向着输入信号频率方向靠近,经过一段时间后,环路进入快捕带过程,最终达到锁定。

(4)快捕带:在此频差范围内,环路不需要经历周期跳跃就可达到锁定,实现捕获过程。

对于简单的PLL来说,上面的四个参数的量化关如下图所示。

由上图可见,同步带比其它三个频带要宽的多,而捕获带则要大于快捕带,并且大多数情况下捕获带也比失锁带。

PLL捕获过程简单总结:

捕获带是PLL总会变为锁定的范围,但这个过程有时相当慢。

快锁带是PLL在参考频率与输出频率之间的一个差拍内锁定的频率范围,通常PLL的工作频率范围限制在快捕带内。

同步带是PLL能够在静态保持相位跟踪的频率范围。

失锁带是PLL稳定工作的动态范围,如果在这个范围内失去跟踪,通常PLL会再次锁定,但如果是捕捉过程,则这个过程是缓慢的。

-

噪声

+关注

关注

13文章

1122浏览量

47437 -

pll

+关注

关注

6文章

777浏览量

135203

原文标题:行业 | 设计干货,芯片中PLL中相位噪声基本介绍

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何根据基本的数据表规格估算出PLL的相位噪声

如何在PLL输出端产生最低的相位噪声?

如何根据基本的数据表规格估算出PLL的相位噪声

浅析芯片中PLL中的相位噪声

浅析芯片中PLL中的相位噪声

评论