乘法器是众多数字系统中的基本模块。从原理上说它属于组合逻辑范畴:但从工程实际设计上来说,它往往会利用时序逻辑设计的方法来实现,属于时序逻辑的范畴。

通过这个实验使大家能够掌握利用FPGA/CPLD设计乘法器的思想,并且能够将我们设计的乘法器应用到实际工程中。乘法器的设计方法有两种:组合逻辑设计方法和时序逻辑设计方法。采用经合逻辑设计方法,电路事先将所有的乘积项全部计算出来,最后加法运算。采用时序逻辑设计方法,电路将部分已经得到的乘积结果右移,然后与乘积项相加并保存和值,反复迭代上述步骤直到计算出最终乘积。

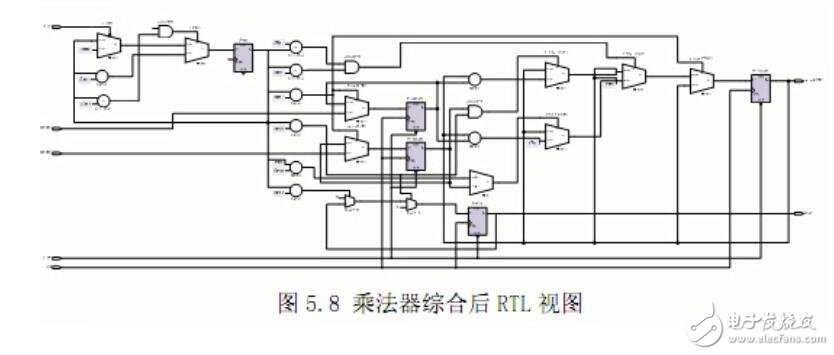

在该实验中就是要利用时序逻辑设计方法来设计-一个16位乘法器,既然是利用时序逻辑设计方法那么就得利用时钟信号控制乘法器运算。用时序逻辑设计方法与用组合逻辑设计方法比较,它有什么好处呢?利用时序逻辑设计方法可以使整体设计具备流水线结构的特征,能适用在各种实际工程设计中。

更多关于BJ-EPM240学习板之乘法器设计实验请看视频。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1630文章

21761浏览量

604443 -

乘法器

+关注

关注

8文章

205浏览量

37123

发布评论请先 登录

相关推荐

求助,LMX2572LP参考时钟路径中的乘法器MULT的输入频率范围问题求解

在lmx2572LP的参考时钟输入路径中,有一个乘法器MULT,其输入频率范围在手册中描述为10Mhz~40MHz。当我在TICS Pro软件中进行配置时,这个乘法器提示我“Maximum

发表于 11-08 11:36

请问如何用VCA810实现模拟乘法器?

我在《德州仪器高性能单片机和模拟器件在高校中的应用和选型指南》中看见,书中说VCA810可以做为模拟乘法器使用,但是应用手册里的公式却不是V0=VC*Vin,而是一个带指数向的公式,所以我很好

发表于 09-23 07:11

CDCF5801A具有延迟控制和相位对准的时钟乘法器数据表

电子发烧友网站提供《CDCF5801A具有延迟控制和相位对准的时钟乘法器数据表.pdf》资料免费下载

发表于 08-22 10:56

•0次下载

CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表

电子发烧友网站提供《CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表.pdf》资料免费下载

发表于 08-22 09:18

•0次下载

请问带有乘法器的信号链噪声带宽如何确定?

有一个信号链路,前级运放设置的带宽是100K-110K,增益为10倍,输入信号也在这个带宽内,然后后面经过一个乘法器,将信号频谱搬移到0-10K这个带宽内,后级放大电路的带宽也设置到0-10K,增益设置为10倍,那么假设最前端输入电压噪声密度为10nV/sqrt(Hz),输出电压噪声应为多少呢?

发表于 08-15 08:00

SN5497、SN7497同步6位二进制速率乘法器数据表

电子发烧友网站提供《SN5497、SN7497同步6位二进制速率乘法器数据表.pdf》资料免费下载

发表于 06-03 09:24

•2次下载

CMOSBCD速率乘法器CD4527B TYPES 数据表

电子发烧友网站提供《CMOSBCD速率乘法器CD4527B TYPES 数据表.pdf》资料免费下载

发表于 05-21 09:19

•0次下载

CMOS二进制速率乘法器CD4089B TYPES 数据表

电子发烧友网站提供《CMOS二进制速率乘法器CD4089B TYPES 数据表.pdf》资料免费下载

发表于 05-21 09:17

•0次下载

BJ-EPM240学习板之乘法器设计实验

BJ-EPM240学习板之乘法器设计实验

评论