MAXII内部震荡时钟使用实例

①新建工程,并建一个verilog文档作为顶层设计文件。

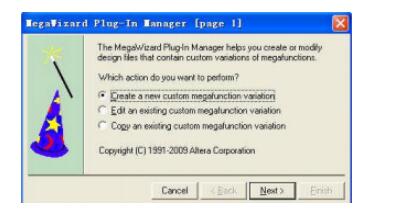

②配置内部振荡器的宏功能。点击ToolsMegaWizardPlug-InManager…,弹出如图5.25所示的对话框。使用第一个默认选项新建一个宏功能,再点击“next”。

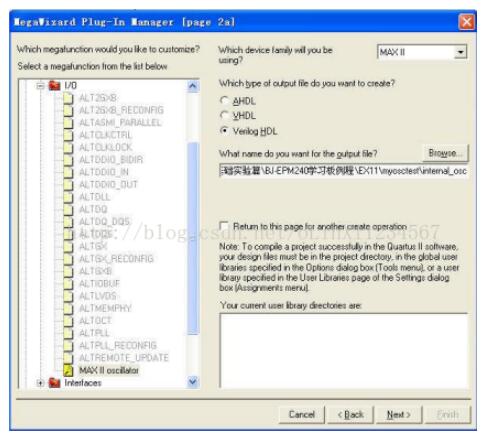

然后在新弹出的窗口中如图5.26进行选择设置。功能部分选择I/O下拉选项的最后一个“MAXIIoscillator”,器件选择“MAXII”,语言选择“VerilogHDL”,在输出文件最后加上文件名,这里命名为“internal_osc”。完成设置后点击“next”。

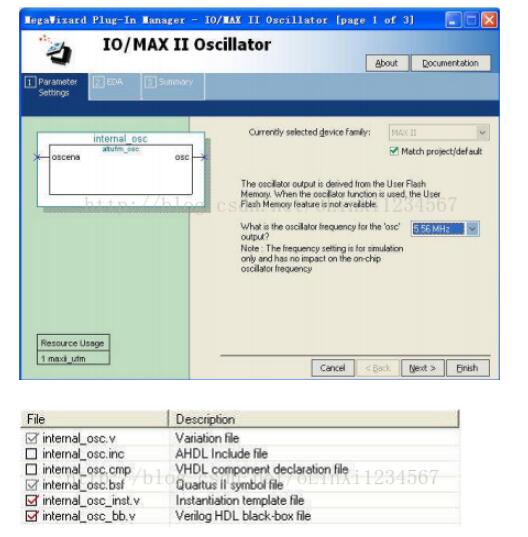

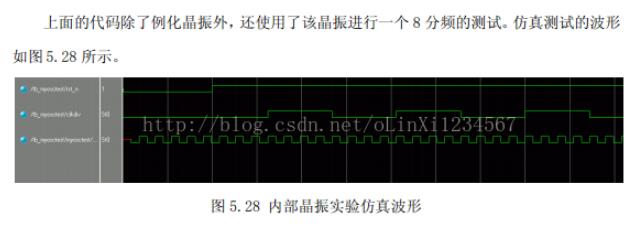

③往后就是具体的晶振的设置了,在第一步ParameterSetting里选择使用的晶振频率,EDA里也没有需要设置的,Summary里选择需要的输出文件即可。

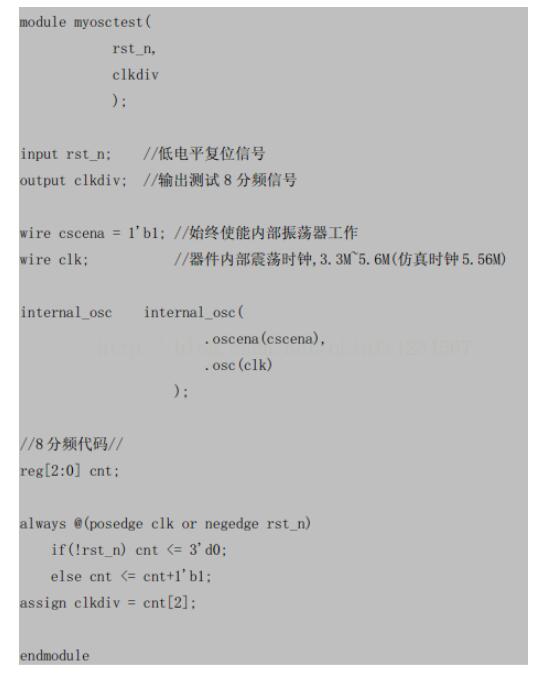

在配置完成后点击“Finish”即可,然后到文件输出的文件夹下找到internal_osc_inst.v文件,它是一个配置好的宏功能的例化文件,拷贝到我们的工程顶层下进行更改。更改后的顶层源代码如下:

-

时钟

+关注

关注

11文章

1738浏览量

131623 -

MAXII

+关注

关注

0文章

2浏览量

6810

发布评论请先 登录

相关推荐

TLV320ADC6140内部有时钟源吗?

使用LMK04228输出100MHZ的波形,出现了类似震荡的情况,导致FPGA端的时钟无法锁定,怎么解决?

TAS5731M内部有主时钟MCLK吗?

INA286输出震荡的原因?

LMH6518芯片内部前级放大器高增益时发生震荡怎么解决?

在ESP32C3中如何设置CPU震荡源为内部PLL_CLK?

凯迪正大分享电缆震荡与电缆震荡试验的注意点

使用STM8L做内部RTC做时钟,时钟计时计到了超过24时怎么解决?

如何在PSoC™ 4000S上使用外部时钟而不是内部时钟?

芯片为什么要时钟信号 时钟芯片的作用是什么?

FPGA时钟内部设计方案

GD32F303 使用PA8输出内部时钟频率

MAXII内部震荡时钟使用实例

MAXII内部震荡时钟使用实例

评论