Testbench

testbench是一种验证的手段。首先,任何设计都是会有输入输出的。但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估。那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟平台”的产生。在这个平台上你可以对你的设计从软件层面上进行分析和校验,这个就是testbench的含义。

简单的Testbench设计

//timescale 仿真时间单位/时间精度(时间精度不能比时间单位还要大)

timescale 1ns/1ps

//定义一个无输入无输出的Moudle

module Led_clg_tst();

//被测设计的输入信号,对应测试脚本的输出信号(注意要定义成reg)

reg clk;

reg rst_n;

//被测设计的输出信号,对应测试脚本的输入信号(注意要定义成wire)

wire led;

//例化待测模块

Led led_test

(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

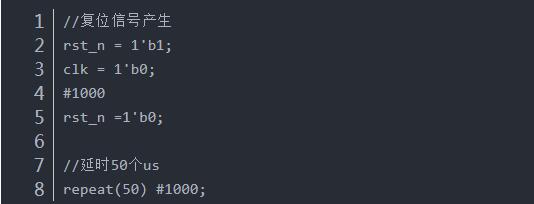

//使用Initail生成rst_n激励

initial

begin

//监控Led信号变化

monitor(monitor(time,”led value= %b\n”,led);

end

//使用alwasys模拟产生25M的时钟信号

always #20 clk = ~clk;

endmodule

-

设计

+关注

关注

4文章

818浏览量

69888

发布评论请先 登录

相关推荐

编写高效Testbench的指南和示例

verilog HDL的testbench怎么编写?

Verilog testbench问题求助

FPGA入门必备:Testbench仿真文件编写实例详解

最实用的Modelsim使用教程

如何确定芯片的方向 最简单的芯片原理

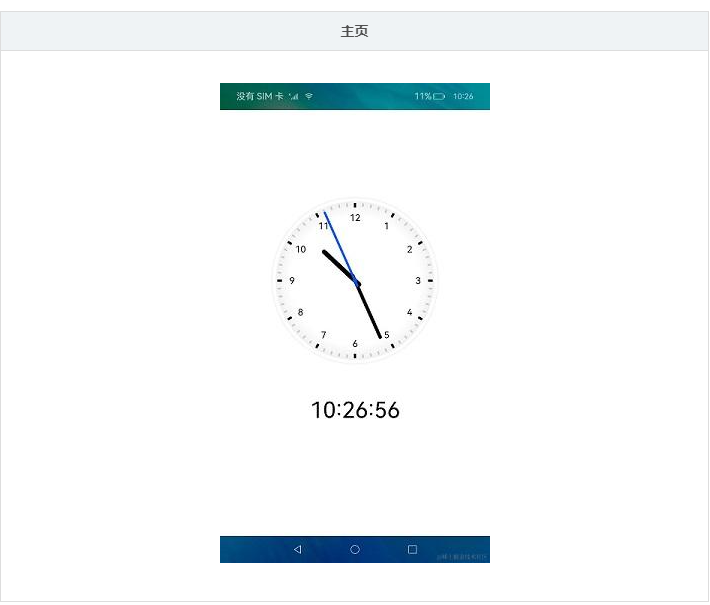

简单的Testbench设计

简单的Testbench设计

评论