精密模数转换器应用广泛,如仪器仪表和测量、电力线继电保 护、过程控制、电机控制等。目前,SAR 型ADC 的分辨率可 达18 位甚至更高,采样速率为数MSPS;Σ-Δ 型ADC 的分辨 率则达到24 位甚至32 位,采样速率为数百kSPS。为了充分 利用高性能ADC 而不限制其能力,用户在降低信号链噪声方 面(例如实现滤波器)面临的困难越来越多。

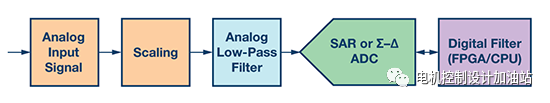

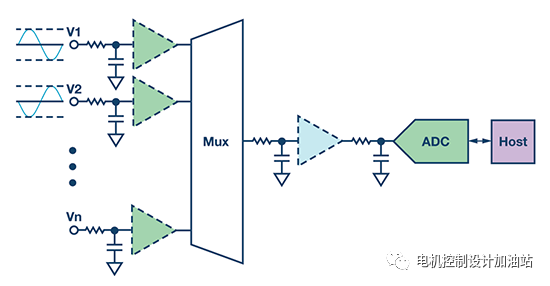

本文讨论在ADC 信号链中实现模拟和数字滤波器以便达到最 佳性能所涉及到的设计挑战和考虑。如图1 所示,数据采集信 号链可以使用模拟或数字滤波技术,或两者的结合。精密SAR 型和Σ-Δ 型ADC 一般在第一奈奎斯特区进行采样,因此,本 文将着重讨论低通滤波器。本文的意图不是讨论低通滤波器的 具体设计技术,而是讨论其在ADC 电路中的应用。

图1.一般数据采集信号链

理想滤波器和实际滤波器

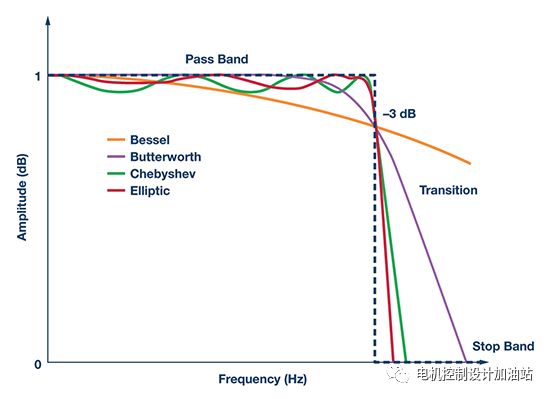

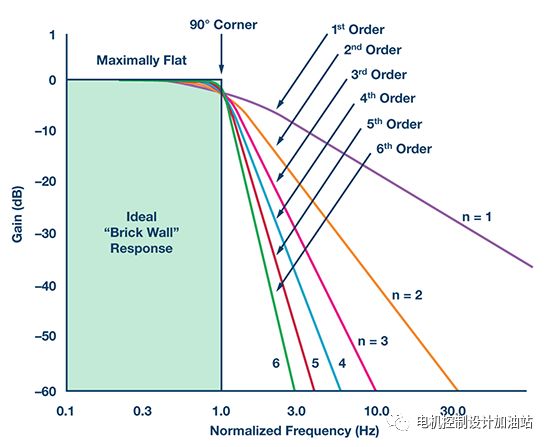

理想低通滤波器应当具有很陡的过渡带,其通带应具有出色的 增益平坦度,如图2 中的砖墙虚线所示。此外,阻带衰减应将 任何残余带外信号降低至0。某些常用实际滤波器的响应如图2 中的彩色线条所示。如果通带增益不平坦或有纹波,这种响应 可能会影响基频信号。阻带衰减不是无限的,会限制对带外噪 声的筛选。过渡带也可能没有陡峭的滚降,导致对截止频率周 围的噪声衰减不佳。另外,所有非理想滤波器都会引入相位延 迟或群延迟。

图2.理想滤波器与实际滤波器的幅度响应对比

模拟滤波器与数字滤波器

模拟低通滤波器可以在ADC 转换之前消除信号路径中的高频 噪声和干扰,帮助避免混叠噪声污染信号。它还能消除滤波器 带宽之外的过驱信号的影响,避免调制器饱和。发生输入过压 时,模拟滤波器还能限制输入电流,衰减输入电压。因此,它 能保护ADC 输入电路。叠加于接近满量程信号上的噪声尖峰 可能会让ADC 的模拟调制器饱和,必须利用模拟滤波器将其 衰减。

由于数字滤波发生在转换之后,因而可以移除转换过程中注入 的噪声。在实际应用中,采样速率远高于奈奎斯特理论指出的 两倍基频信号频率。因此,后置数字滤波器可以利用针对更高 信噪比和更高分辨率的滤波技术来降低转换过程中注入的噪 声,例如:信号带宽之外的输入噪声、电源噪声、基准源噪声、 数字接口馈通噪声、ADC 芯片热噪声或量化噪声。

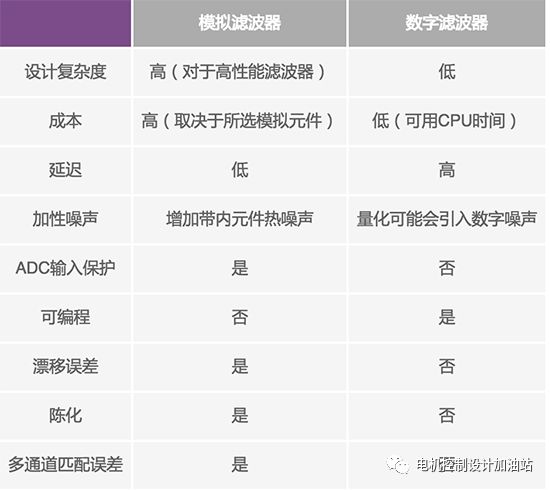

表1简要列出了模拟滤波器与数字滤波器的优点和缺点。

表1.模拟滤波器与数字滤波器

模拟滤波器考虑

抗混叠滤波器放在ADC 之前,因此这些滤波器必须为模拟滤 波器。理想抗混叠滤波器具有如下特性:通带内具有单位增益, 无增益变化,混叠衰减水平与所用数据转换系统的理论动态范 围一致。

根据架构不同,ADC 会有不同的输入电阻,这会影响输入滤 波器设计。以下考虑关系到ADC 模拟输入滤波器的设计。

与ADC 前端接口的RC 抗混叠滤波器的限制

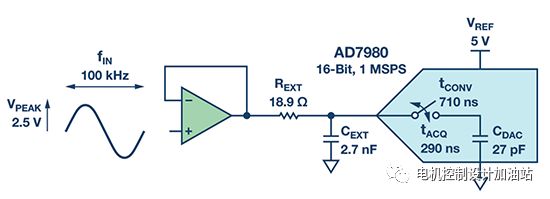

在Alan Walsh 为Analog Dialogue 杂志撰写的文章"精密SAR 型模数转换器的前端和放大器和RC 滤波器设计" 中,有一个针对AD7980ADC 的RC 滤波器应用示例,如图3 所示。

算出的RC 滤波器是一个低通滤波器,截止带宽为3.11 MHz。 但是,某些设计人员可能会意识到,3.11 MHz 远大于100 kHz 的输入信号频率,因此,该滤波器无法有效降低带外噪声。为 实现更高动态范围,可以换用590 Ω 电阻,以获得100 kHz 的 –3 dB 带宽。这种方法主要有两个问题。由于通带中会有更多 衰减,对于AD7980 ADC 示例,100 kHz 附近的幅度衰减最高 可达30%,因此,信号链精度会大大降低。带宽越小,则建立 时间越长,这使得AD7980 的内部采样保持电容无法在指定的 采集时间内完成充电,因而无法执行下一次有效转换。这导致 ADC 转换精度降低。

设计人员应当确保ADC 之前的RC 滤波器能在目标采集时间内 完全建立。这对需要较大输入电流或具有等效的较小输入阻抗 的精密ADC 来说异常重要。某些Σ-Δ 型ADC 在无缓冲输入模 式下对输入RC 值的要求最高。可以将具有较大电阻或电容的超 窄低通滤波器放在一般具有较大输入阻抗的输入放大器之前。 或者可以选择具有极高输入阻抗的ADC,例如ADAS3022其 输入阻抗为500 MΩ。

图3.采用16 位1 MSPS ADC AD7980 的RC 滤波器

1. 多路复用采样信号链的滤波器建立时间

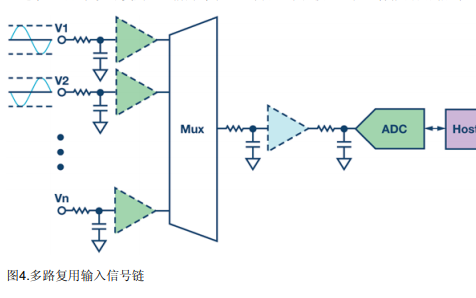

在通道间切换时,多路复用输入信号通常含有较大的阶跃。最 差情况下,一个通道处于负满量程,而下一个通道则处于正满 量程(见图4)。这种情况下,当多路复用器切换通道时,输入 阶跃大小将是ADC 的满量程。

对于这些通道,可以在多路复用器之后使用一个单通道滤波 器,使得设计更简单,成本更低。如上所述,模拟滤波器必定 会引入建立时间。每次多路复用器在通道间切换时,该单通道 滤波器都必须充电到所选通道的值,因而会限制吞吐速率。为 提高吞吐速率,可以在多路复用器之前为每个通道添加一个滤 波器,但这样做会提高成本。

图4.多路复用输入信号链

2. 通带平坦度和过渡带限制与噪声的关系

遭遇高噪声的应用,尤其是在接近第一奈奎斯特区边缘处发生 很高干扰的应用,需要滚降厉害的滤波器。然而,人们已从实际模拟低通滤波器得知:从低频到高频,幅 度会滚下来,并有一个过渡带。增加滤波器级数或阶数可以改 善带内信号的平坦度,并使过渡带收窄。然而,这些滤波器的 设计很复杂,因为它们对增益匹配非常敏感,以至于无法实现 数阶的衰减幅度。此外,在信号链中增加任何元件(如电阻或 放大器)都会引入带内噪声。

图5.不同阶数的理想巴特沃兹滤波器过渡带

对于某些具体应用,模拟滤波器设计的复杂度和性能需要进行 取舍。例如,在采用AD7606的电力线继电器保护应用中,对 于50 Hz/60 Hz 基频输入信号及其相关前五次谐波,保护通道 的精度要求低于测量通道。保护通道可以使用一个一阶RC 滤 波器,而测量通道使用二阶RC 滤波器,以便提供更好的带内 平坦度和更急剧的滚落过渡。

3. 同步采样的相位延迟和匹配误差

滤波器设计不仅仅关系到频率设计,用户可能还需要考虑模拟 滤波器的时域特性和相位响应。在某些实时应用中,相位延迟 可能非常重要。如果相位随输入频率而变化,那么相位变动将 更糟糕。滤波器的相位变化一般用群延迟来衡量。对于非常数 群延迟,信号会在时间中扩散,导致脉冲响应变得很差。

对于多通道同步采样应用,例如电机控制或电力线监控中的相 电流测量,还应考虑相位延迟匹配误差。确保滤波器在多个通 道上引起的额外相位延迟匹配误差可以忽略不计,或者在工作 温度范围的信号链误差预算范围内。

4.低失真和低噪声应用的元件选择挑战

对于低谐波失真和低噪声应用,用户必须为信号链设计选择合 乎要求的元件。模拟电子元件不是完全线性的,会引起谐波失 真。Walsh 的文章中讨论了如何选择低失真放大器和如何计算 放大器噪声。放大器等有源元件需要低THD + N,同时也要考 虑普通电阻和电容等无源元件的失真和噪声。

电阻的非线性有两个来源:电压系数和功率系数。根据具体应 用,高性能信号链可能需要使用由特定技术制造的电阻,如薄 膜或金属电阻。如果选择不当,输入滤波电容可能会造成显著 失真。如果成本预算允许,聚苯乙烯和NP0/C0G 陶瓷电容是 很好的备选元件,可以改善THD。

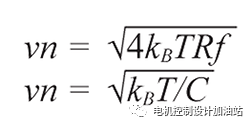

除放大器噪声外,电阻和电容也会有电子噪声,后者是由处于 均衡态的电导体内部的电荷载子的热扰动产生的。RC 电路的 热噪声有一个简单的表达式,电阻R 是满足滤波要求所需要 的,同时R 越高,相应的热噪声也越大。RC 电路的噪声带宽 为1/(4RC)。

除放大器噪声外,电阻和电容也会有电子噪声,后者是由处于 均衡态的电导体内部的电荷载子的热扰动产生的。RC 电路的 热噪声有一个简单的表达式,电阻R 是满足滤波要求所需要 的,同时R 越高,相应的热噪声也越大。RC 电路的噪声带宽 为1/(4RC)。

B (玻尔兹曼常数) = 1.38065 × 10–23m2kgs–2K–1

T 为温度 (K)

f 为砖墙滤波器近似带宽

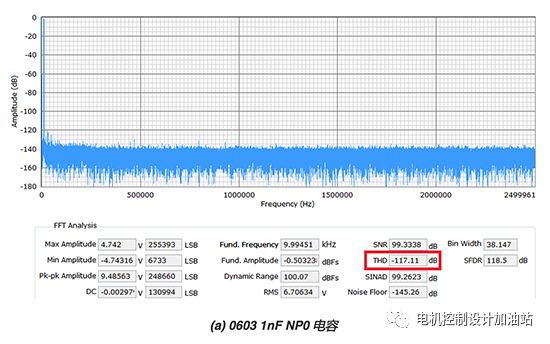

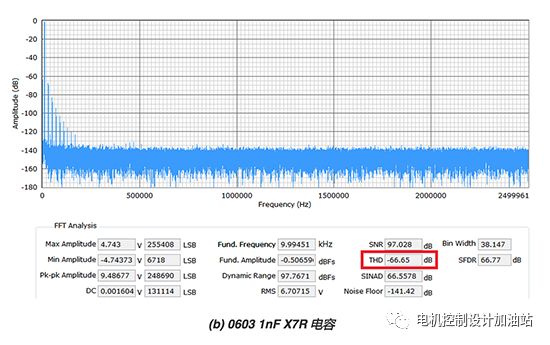

图6 显示在EVAL-AD7960FMCZ评估板上,NP0 电容和X7R 电容对THD 性能的影响:(a) 显示一个10 kHz 正弦波信号音 的频谱,C76 和C77 为1 nF 0603 NP0 电容,而 (b) 显示使用 1 nF 0603 X7R 电容时的频谱。

图6.在EVAL-AD7960FMCZ 评估板上NP0 和X7R 电容对THD 的影响

了解前面的设计考虑之后,便可利用ADI 公司的模拟滤波器向导设计有源模拟滤波器。它会根据应用要求计算电容和电阻值,并选择合适的放大器。

数字滤波器考虑

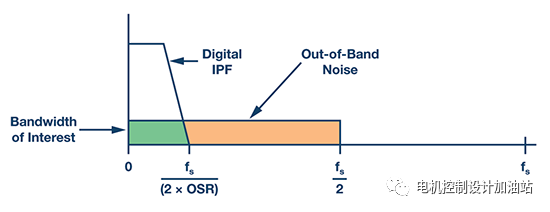

SAR 型和Σ-Δ 型ADC 正在稳步实现更高的采样速率和输入带 宽。以两倍奈奎斯特速率对一个信号过采样,会将ADC 量化 噪声能量均匀扩散到两倍频段中。这样便很容易设计数字滤波 器来限制数字化信号的频带,然后通过抽取来提供所需的最终 采样速率。这种技术可降低带内量化误差并提高ADC SNR。 它还能放宽滤波器滚降要求,从而减轻抗混叠滤波器的压力。 过采样降低了对滤波器的要求,但需要更高采样速率ADC 和 更快的数字处理。

1. 对ADC 使用过采样速率所取得的实际SNR 改善

利用过采样和抽取滤波器所取得的SNR 改善,可从N 位ADC 的 理论SNR 求得:SNR = 6.02 × N + 1.76 dB + 10 × log10[OSR], OSR = fs/(2 × BW)。注意:此公式仅适用于只存在量化噪声的 理想ADC。

图7.奈奎斯特转换器过采样

还有很多其他因素会将噪声引入ADC 转换代码中。例如:信 号源和信号链器件的噪声,芯片热噪声,散粒噪声,电源噪声, 基准电压噪声,数字馈通噪声,以及采样时钟抖动引起的相位 噪声。这种噪声可能会均匀分布在信号频段中,表现为闪烁噪 声。因此,实际实现的ADC SNR 改善幅度一般低于用公式计 算出的值。

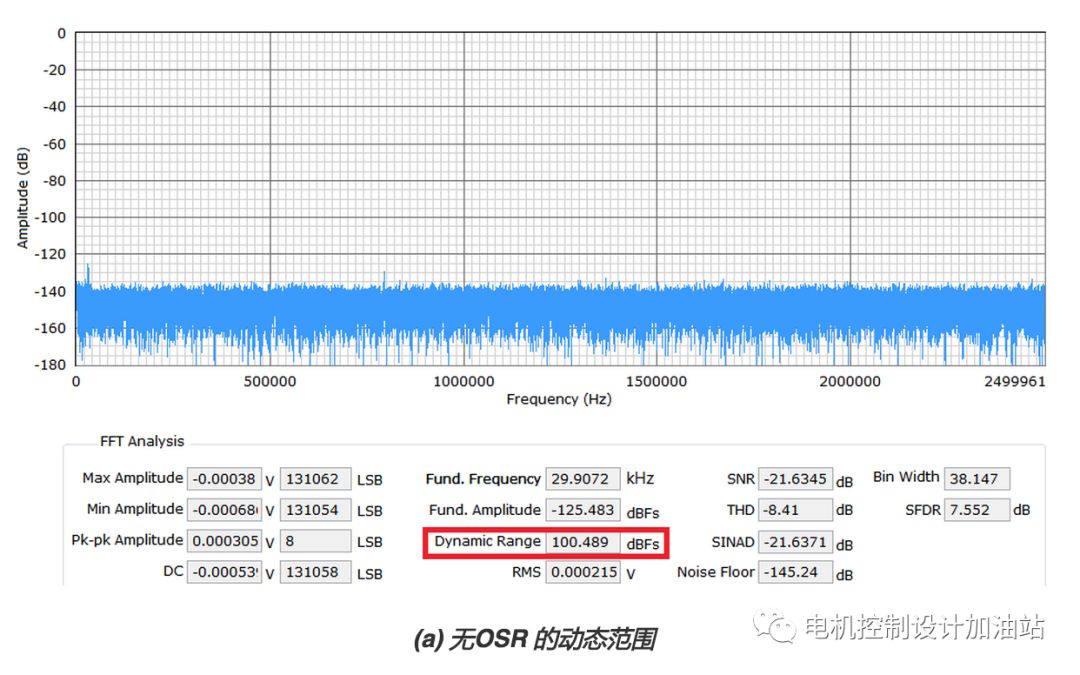

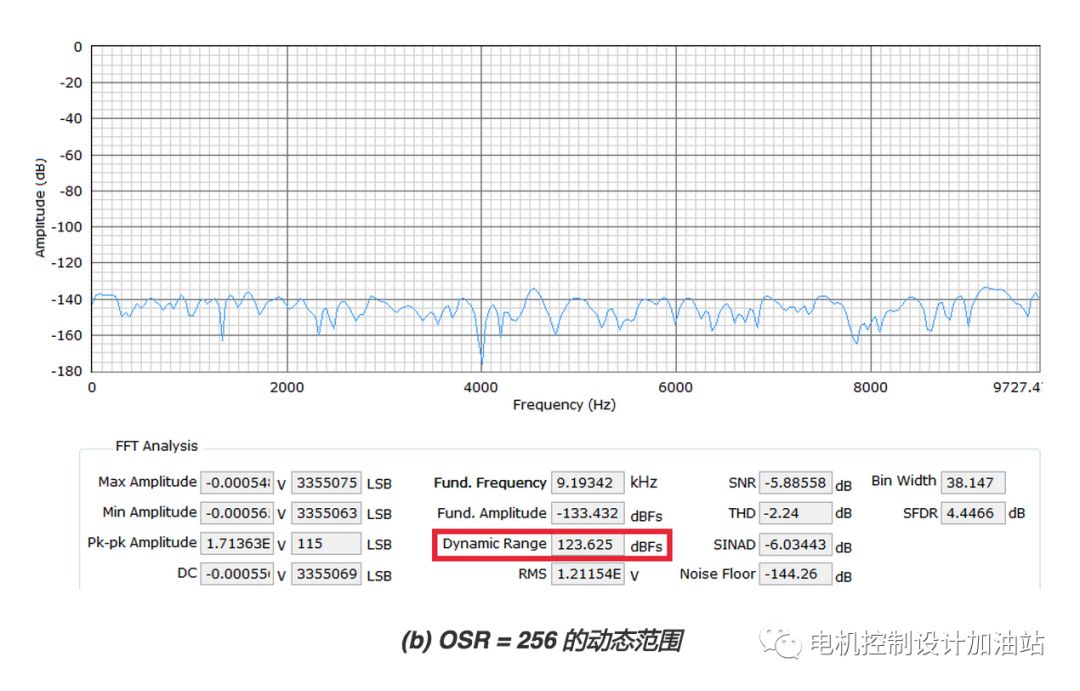

2. EVAL-AD7960FMCZ 评估板上利用过采样实现的动态改善

在应用笔记AN-1279 中,256×过采样下18 位AD7960 ADC 的 实测动态范围为123 dB。这是用于高性能数据采集信号链,如 光谱分析、磁共振成像 (MRI)、气相色谱分析、振动、石油/ 天然气勘探和地震系统等。

如图8 所示,与理论SNR 改善幅度计算相比,测得的过采样 动态范围低1 dB 至2 dB。原因是来自信号链器件的低频噪声 限制了总体动态范围性能。

图8.OSR 256 时的动态范围改善

3. 充分利用SAR 型和Σ-Δ 型ADC 中的集成数字滤波器

数字滤波器通常位于FPGA、DSP 或处理器中。为了减少系统 设计工作,ADI 公司提供了一些集成后置数字滤波器的精密 ADC。例如,AD7606 集成了一个一阶后置数字sinc 滤波器用 于过采样。它很容易配置,只需上拉或下拉OS 引脚。Σ-Δ 型 ADC AD7175-x 不仅有传统sinc3 滤波器,还有sinc5 + sinc1 和增强型50 Hz/60 Hz 抑制滤波器。AD7124-x 提供快速建立模 式(sinc4 + sinc1 或sinc3 + sinc1 滤波器)功能。

4.多路复用采样ADC 的延迟取舍

延迟是数字滤波器的一个缺点,它取决于数字滤波器阶数和主 时钟速率。对于实时应用和环路响应时间,应当限制延迟。数 据手册所列的输出数据速率是指在单一通道上执行连续转换 时转换结果有效的速率。当用户切换到另一通道时,建立Σ-Δ 调制器和数字滤波器还额外需要些时间。与这些转换器相关的 建立时间是指通道变更之后输出数据反映输入电压所需的时 间。通道变更之后,为精确反映模拟输入,必须清除数字滤波 器中与前一模拟输入相关的全部数据。

以前,Σ-Δ 型ADC 的通道切换速度比数据输出速率要小得多。 因此,在多路复用数据采集系统等切换应用中,必须明白:获 得转换结果的速率要比对单一通道连续采样时可达到的转换 速率低好几倍。

ADI 公司的某些新型Σ-Δ ADC(如AD7175-x)内置优化的数字 滤波器,可减少通道切换时的建立时间。AD7175-x 的sinc5 + sinc1 滤波器主要用于多路复用应用,在10 kSPS 和更低的输出 数据速率时,可实现单周期建立。

5.数字滤波器通过抽取避免混叠

很多文章都讨论过,过采样频率越高,模拟滤波器设计就越容 易。当采样速率高于满足奈奎斯特准则所需的速率时,便可使 用较简单的模拟滤波器来避免受到极高频率所产生的混叠影 响。很难设计一个能够衰减所需频段而不失真的模拟滤波器, 但很容易设计一个利用过采样抑制较高频率的模拟滤波器。这 样便很容易设计数字滤波器来限制转换信号的频带,然后通过 抽取来提供所需的最终采样速率,但又不会丧失所需信息。

实施抽取之前,需要确保这种重新采样不会引入新的混叠问 题。抽取之后,确保输入信号符合奈奎斯特关于采样速率的 理论。

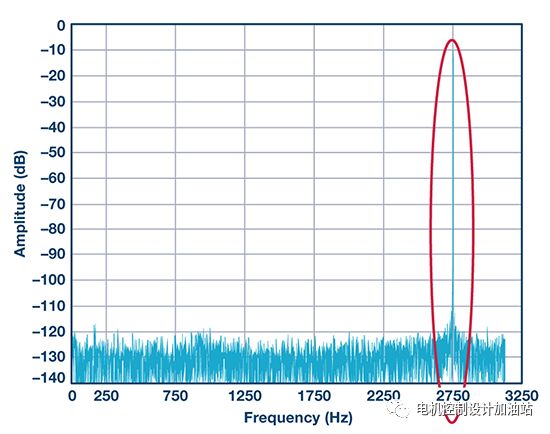

EVAL-AD7606/EVAL-AD7607/EVAL-AD7608EDZ 评估板可以每 通道200 kSPS 的速率运行。在下面的测试中,配置其采样速率为 6.25 kSPS,过采样比为32。然后,将一个3.5 kHz –6 dBFS 正弦 波施加于AD7606。图9 显示2.75 kHz (6.25 kHz – 3.5 kHz) 处有 一个–10 dBFS 混叠镜像。因此,若ADC 之前没有合格的抗混叠 模拟滤波器,当使用过采样时,数字滤波器就可能会因为抽取而 引起混叠镜像。应使用模拟抗混叠滤波器来消除这种叠加于模拟 信号上的噪声尖峰。

图9.OSR 抽取采样率小于奈奎斯特频率时的混叠

结论

本文讨论的挑战和考虑可帮助设计人员设计出实用的滤波器 以实现精密采集系统的目标。模拟滤波器必须在不违反系统误 差预算的条件下与SAR 型或Σ-Δ 型ADC 的非理想输入结构接 口,数字滤波器不应在处理器端引起误差。这不是简单的任务, 必须在系统规格、响应时间、成本、设计工作量和资源等方面 做出权衡。

参考电路

Holdaway, Mark. "ADC 用抗混叠滤波器设计"。EDN,2006 年。

Walsh, Alan。 精密SAR 型模数转换器的前端放大器和RC 滤 波器设计。Analog Dialogue,第46 卷第4 期,2012 年。

Wescott,Tim;Wescott 设计服务。 "采样:奈奎斯特没说什么 以及怎么办"。Wescott 研讨会,2015 年。

巴特沃兹滤波器设计。

模拟和数字抗混叠滤波。

-

滤波器

+关注

关注

161文章

7924浏览量

179587 -

adc

+关注

关注

99文章

6567浏览量

546720 -

数据采集

+关注

关注

39文章

6461浏览量

114517

原文标题:精密ADC用滤波器设计的实际挑战和考虑

文章出处:【微信号:motorcontrol365,微信公众号:电机控制设计加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字滤波器,数字滤波器原理是什么?

使用滤波器设计精密ADC需要考虑什么问题和面临的挑战

在ADC信号链中实现模拟和数字滤波器以便达到最佳性能所涉及到的设计挑战和考虑

在ADC信号链中实现模拟和数字滤波器以便达到最佳性能所涉及到的设计挑战和考虑

评论