这次奉上与LPC5500“核心”相关的“硬核”技术——双核,以飨读者。诚然,MCU双核已不是什么新鲜玩意儿。但是,LPC5500博采了LPC4300和LPC54110这两个系列所长,使得双核更简单实用。

LPC5500双核基本架构

双核并不高深,所谓双核就是两个CPU——中央处理单元,也就是一个MCU芯片内置了两个CPU。

和之前支持双核的LPC系列一样,针对于MCU嵌入式应用,LPC5500依然采用简单的非对称架构,即一个主CPU,一个从CPU,这类似于有些产品采用主MCU和从MCU的设计。只是支持双核的MCU,是共享此MCU所有的存储器和外设接口资源。

共享就带来竞争的问题,处理不当则影响性能。LPC5500有配套的系统架构来使得此共享可转化为并行的,从而尽量避免竞争,来保证性能不被影响。

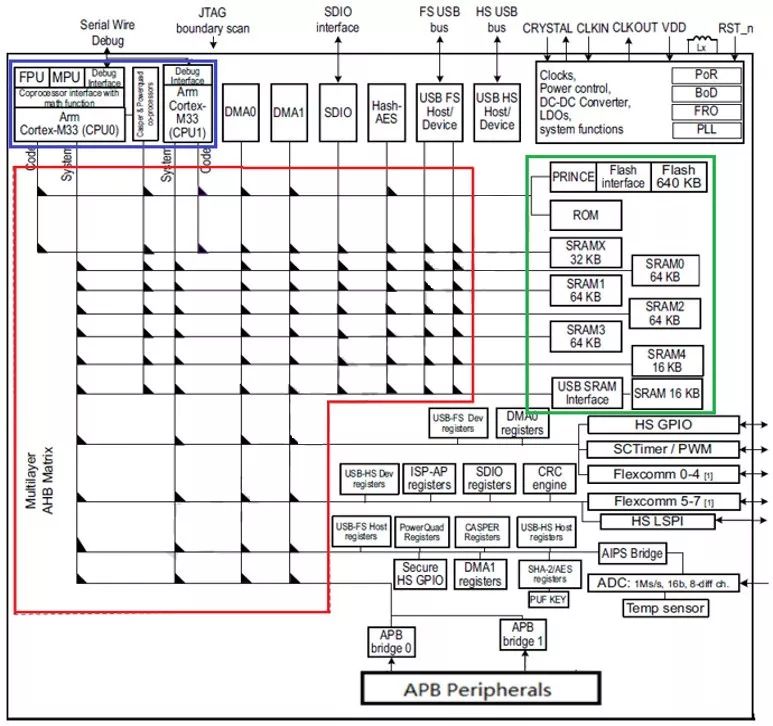

应对竞争架构上的考虑,如下图所示,主要有两条:

内部AHB总线是多层矩阵架构;

分离出多块独立的SRAM。

图中所示:红色框是多层AHB矩阵总线;绿色框是多块分立的存储块。主CPU和从CPU的代码数据可存放在不同存储块中,它们和图中左下角大量外设接口并行的挂在矩阵总线上。

这样,蓝色框中的双核CPU0和CPU1,可以同时并行地对存储块和外设接口进行访问,即程序可以同时运行。如此,则双核的威力能够得以充分的发挥。

至此,我们初步认识了LPC5500双核,了解了其基本框架。但是,这好比我们只是远远的看见了一个人,大概知道其身形,他具体容貌怎样的呢?让我们一起往下看

LPC5500双核面貌特征

上面提到,LPC5500双核分为主从,主CPU命名为CPU0,从CPU命名为CPU1。它们都是基于ARM Cortex-M33的。

它们的基本配置构成如下:

1、CPU0 (r0p3版):

频率最高可达100MHz

TrustZone、DSP、浮点单元和存储保护单元(MPU)

内置嵌套向量中断控制器(NVIC)

串行线调试接口(SWD)

内置嵌套向量中断控制器(NVIC)

串行线调试接口(SWD)

系统嘀嗒定时器(System tick timer)

2、CPU1 (r0p3版):

频率最高可达100 MHz

内置嵌套向量中断控制器(NVIC)

串行线调试接口(SWD)

系统嘀嗒定时器(System tick timer)

显然,作为从的CPU1比主CPU0少了TrustZone、浮点单元(FPU)等,这使得主CPU0天然地计算处理能力更强。

但是赋予主CPU0这些亮点,不是让它做颜值担当,而是任务担当的。这让我们自然想到双核的典型应用——相信这也是大家很关心的。

LPC5500双核典型应用

LPC5500的双核典型应用,即基本应用思路,与之前LPC4300和LPC54110一样。

主CPU用来做处理计算任务(比如算法),从CPU负责外设实时控制和数据传输。

这样,能充分利用双核达到更好性能。参见下图:

哦,LPC5500双核很“酷”的样子,有点“喜欢”上它了,可是,相爱容易相处难啊?!

不要担心,难,那是因为不懂得如何“相处”。

接下来,让我们来聊聊如何和LPC5500双核“相处”——双核的实现,这主要涉及到以下内容:双核启动;双核通讯;双核调试。

1双核启动

对于单核MCU,上电启动过程简单明了,如单身狗的生活简单自由,该干啥干啥,不能指望也无需考虑他人。

两人世界就需要协商着行动了,LPC5500采取了和最早LPC4300系列类似的双核启动机制,即出厂默认并固定一个核为主,另一个为从,不能更改,“专制”却简单易用。

随后的LPC54110系列则实行“民主”机制,两个核可以轮流坐庄,即用户可以在启动过程中选择其中之一为主核,这样提供了灵活性,但略微复杂。

为了简单起见,如今新的LPC5500双核使用固定的主从模式。

LPC5500上电时,自然地按照主从,主核CPU0如单核一样直接启动,从核CPU1则hold住不动——这由硬件自动完成。

主核启动后负责初始化运行环境,然后配置好从核的启动地址(即从核代码映像运行的起始地址),最后释放从核CPU1——这些由软件完成。这时,主从双核就分别如同单核一样同时运行它们各自的代码了。

要让双核“和谐”运作,关键是要让两个核的代码映像存储和运行空间独立互不干扰(参见前面关于多层总线矩阵和多块存储块的介绍),这点具体实现方法是灵活的,比单核来得复杂些。这里就不具体展开,有需要的可找相关资料学习,比如,我们有篇应用笔记通过测试双核coremark分数,提供了一种达到最好性能的实现方法。不关心这些细节也不用担心,NXP已经提供了相关SDK库可直接借用。

2双核通讯

当两个核都运行起来后,它们可以像两个不同行业的人,各自做着自己的本职工作,默默为社会贡献自己的力量,老死不相往来。但大多数应用中,两个核除了各司其职,还需要互相通讯,协同工作。

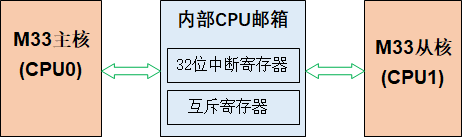

LPC5500提供了一套简单的硬件通讯机制,叫内部CPU邮箱通讯机制,可以适用于大多数嵌入式系统双核的通讯应用。

这套机制从LPC54110系列继承而来,最早的LPC4300系列双核通讯几乎完全靠软件来实现,占用资源,且给使用带来不少难度。目前这套机制,简单易用,但不死板,留给用户一定灵活发挥空间。

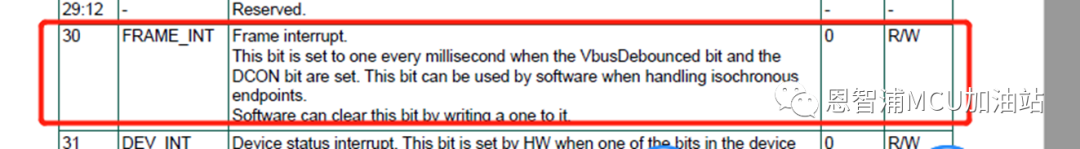

它主要提供了两种寄存器,一种是32位的CPU中断寄存器,两个CPU都能访问它,32位中只要有一位不为零,就能产生中断请求,且每一位可代表一个不同状况,比如事件或者状态,这完全可由用户自己定义。

这样CPU间就可相互实时通讯了,比如一个CPU完成某项任务,写入一个非0值到此寄存器,发出中断信号,另一CPU中断后读取此值,来决定后续工作。

通讯的一大需求就是同步,这就需要另一个叫做互斥寄存器的来完成,它只有第0位(bit0)可用,复位后默认值为1。当读此寄存器时,读出数值的同时这位自动被清0;当写它时,这位将再次被置为1。

此正是互斥量的特性,以用于实现CPU间对任何共享资源的握手同步。例如,当一个CPU要访问某共享资源时,先读此寄存器,若读到的是1,表示资源可用,同时1被自动清为0;若读到0,则表示资源被占用;在CPU用完共享资源时,即写此寄存器,使其置1,表示释放了资源为可用。

这套邮箱机制简单框架图如下:

顺便提下,我们在LPC5500 SDK包中还提供了一套开源多核软件开发包,包括库和大量例程。通过库的API提供了支持用户实现复杂的多核通讯机制。

这套多核SDK的库代码包含在LPC5500SDK包以下路径:

例程则在:

3双核调试

LPC5500的双核都支持SWD调试模式,就调试的级别来说,它们是”平等”的。实际实现时,每个核一般有自己的工程,它们各自的调试和单核无异。

但在两个核有关联时(即前面提到的双核启动和双核通讯过程),调试要有所注意,关键就是要真正理解了这两个过程机制,依据这两个机制的特点进行调试,则基本没什么问题。

-

mcu

+关注

关注

146文章

17525浏览量

355309 -

存储器

+关注

关注

38文章

7568浏览量

165159 -

cpu

+关注

关注

68文章

10960浏览量

214216

原文标题:【硬核干货】LPC5500——简便易用的双核技术

文章出处:【微信号:Zlgmcu7890,微信公众号:周立功单片机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于恩智浦LPC5500系列MCU的OKDO E1开发板详解

基于Cortex M33的LPC5500系列MCU主要功能特性介绍

恩智浦LPC55S16 MCU获得了PSA 2级和SESIP 2级保证认证

非对称双核MCU基础知识及核间通信

LPC55S69 Flashmagic不编程的原因?

LPC55S69的双核性能技巧是什么?

LPC5500 Flash过度编程是否可行?

非对称双核MCU基础知识及核间通信

LPC5500双核基本架构!LPC5500双核面貌特征

LPC5500双核基本架构!LPC5500双核面貌特征

评论