由于高速传输的数据速率和紧密耦合布线,高速PCB设计的串扰分析变得越来越重要。传统的基于路的分析已不能满足精度要求,需要三维全波电磁求解器来模拟与PCB结构和频率相关的效应。本文介绍了一种兼具速度和精度的新型混合求解器技术,同时开发了通过S参数后处理用于量化串扰水平的串扰度量的技术。结合这两种技术,工程师可以仅在数小时内就能按计划实现全板串扰分析,从而显著缩短layout后的检查时间并确保及时签核。

1

简介

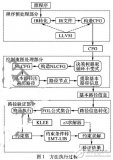

串扰存在于高速PCB中的不同区域。导致串扰的一个重要来源是连接器和封装下的引脚通孔区域和扇出区域。在本文中,我们将用Heracles工具来进行快速全板串扰扫描,以实现信号完整性和高速PCB设计的签核。Heracles提供的混合全波EM求解器具有与传统3D求解器相同的精度,但运行速度提高了一个数量级。

图 1 Heracles 流程

2

混合电磁场求解器

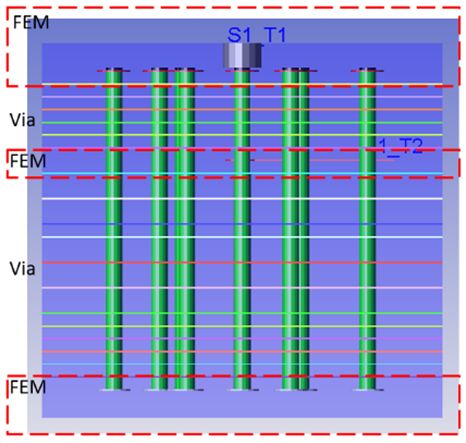

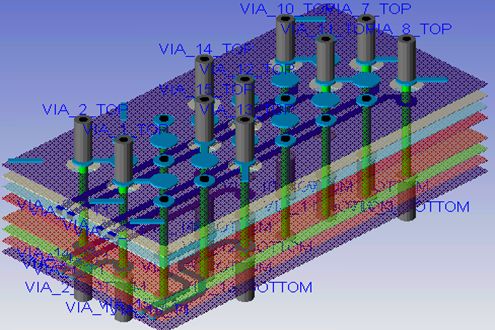

Heracles集成了一套新的基于区域分解的混合算法,与传统的3D求解器相比,它在保持3D仿真精度的同时能显著提高速度。首先,3D PCB结构会被分解为多个层,其中具有纯via的层可以使用via求解器快速求解,而具有via和trace的层则通过3D FEM求解器来解决。

图2 Hybrid 电磁场求解器

3

针对串扰的ICN/TDT

在频域中,ICN(累积串扰噪声)一般被用于量化串扰水平,它表示串扰作为频域中串扰噪声相对于被传输信号的功率谱的加权和。 在时域中,NEXT和FEXT串扰可以通过其频域对应的傅里叶变换获得。测量峰值能表示相应干扰源的串扰水平。所有干扰源的串扰噪声总和就是时域中的串扰量化。

图3 单扰 ICN 与 TDT

4

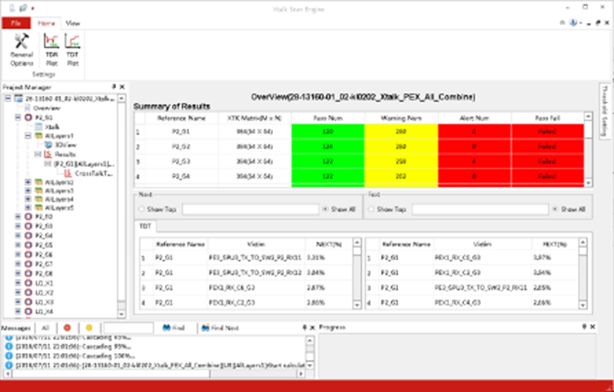

全板串扰检查

在芯禾科技Heracles工具中,设计人员可以轻松选择协议中定义的网络匹配规则的串扰扫描区域。在串扰矩阵中,使用了3种颜色来突出显示串扰级别(pass/warning/alert)。 串扰矩阵允许设计人员在Allegro工具中定位串扰热点,并返回EM仿真模型。

图4 EM 仿真模型

5

结论

本文介绍了Heracles工具中的混合求解器技术。与传统的3D求解器相比,它可以在保持3D仿真精度的同时显著提高速度。设计人员使用Heracles工具,能够在几个小时内实现完整的全电路板串扰分析,从而显着缩短layout后的检查时间并确保及时签核。

图5 仿真结果

-

pcb

+关注

关注

4319文章

23111浏览量

398329 -

求解器

+关注

关注

0文章

77浏览量

4536

原文标题:用于SI签核的自动串扰扫描、阻抗扫描和DRC+

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

《FPGACPLD设计工具──Xilinx+ISE使用详解》

混合电路和模块技术简史

混合信号设计的模拟工具

电子管集成电路混合功放制作详解

混合FEBI求解器的实现

IE和FEBI求解器详解及对比

基于SMT求解器的程序路径验证方法

Heracles工具中的混合求解器技术详解

Heracles工具中的混合求解器技术详解

评论