SRAM主要用于二级高速缓存。它利用晶体管来存储数据。与DRAM相比,SRAM的速度快,但在相同面积中SRAM的容量要比其他类型的内存小。

SRAM的速度快但昂贵,一般用小容量的SRAM作为更高速CPU和较低速DRAM 之间的缓存.SRAM也有许多种,如AsyncSRAM (异步SRAM)、Sync SRAM (同步SRAM)、PBSRAM (流水式突发SRAM),还有INTEL没有公布细节的CSRAM等。

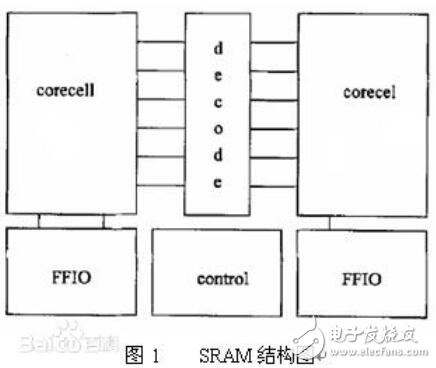

基本的SRAM的架构如图1所示,SRAM一般可分为五大部分:存储单元阵列,行/列地址译码器,灵敏放大器,控制电路,缓冲/驱动电路。SRAM是静态存储方式,以双稳态电路作为存储单元,SRAM不像DRAM一样需要不断刷新,而且工作速度较快,但由于存储单元器件较多,集成度不太高,功耗也较大。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

sram

+关注

关注

6文章

777浏览量

115119

发布评论请先 登录

相关推荐

DS1265AB 8M非易失SRAM技术手册

DS1265 8M非易失SRAM为8,388,608位、全静态非易失SRAM,按照8位、1,048,576字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视V~CC~是否超出容差范围

关于hpm6364的femc同时使用外接sdram和sram的问题

femc连接32Mb的sdram,同时连接fpga,用sram方式与fpga通信。

配置上IO口都配置了IOC_PAD_FUNC_CTL_ALT_SELECT_SET(12);当作femc接口

发表于 11-20 14:45

SRAM和DRAM有什么区别

静态随机存储器(Static Random Access Memory,简称SRAM)和动态随机存储器(Dynamic Random Access Memory,简称DRAM)是两种不同类

SRAM1/2/3可以使用LPDMA通过LPTIM触发ADC4搬运数据到SRAM4吗?

请教一下各位大佬 使用STM32U575LPBAM我看官方例程中 所有的代码运行域都是SRAM4,正常模式也是在SRAM4 但是目前我这边SRAM4 的16K 在正常模式下 不够用,我在正常模式用

发表于 09-20 15:17

请问如何使用片外SRAM?

Hi , 在项目中,我们需要增加片外SRAM,型号是IS62WVS5128GALL 大小是512kb,请问你们是否支持此IC,能否提供驱动或者demo?

发表于 06-25 08:01

C语言指针存在SRAM里面吗

应该有可以回答的上来的,但是大部分应该是回答不上来。标题的回答也不对。 计算机内存里面分这么几种数据 存在SRAM里面,嗯?内存?对也不对,大家觉得内存条应该很快了吧?不,不快。 我的电脑里面有三种

探索存内计算—基于 SRAM 的存内计算与基于 MRAM 的存算一体的探究

本文深入探讨了基于SRAM和MRAM的存算一体技术在计算领域的应用和发展。首先,介绍了基于SRAM的存内逻辑计算技术,包括其原理、优势以及在神经网络领域的应用。其次,详细讨论了基于MRAM的存算一体

请问SRAM地址重映射是在哪一级实现的?

SRAM容量比较大的型号,常见的除了SRAM分为几块如 SRAM1, SRAM2, TCM RAM 等之外,还常见地址重映射的设计。

例如下面这个图是 STM32L4Rx 的地址空间,

发表于 04-24 08:07

Microchip推出容量更大、速度更快的串行SRAM产品线

为满足客户对更大更快的SRAM的普遍需求,MicrochipTechnology(微芯科技公司)扩展了旗下串行SRAM产品线,容量最高可达4Mb,并将串行外设接口/串行四通道输入/输出接口(SPI

STM32把程序下到SRAM里调试好用吗?

刚学会把程序下到SRAM里,以前都直接下载到flash里。下载速度好像也差不多,下载到SRAM里比较麻烦。flash有寿命,直接下载到flash里除了会影响寿命外,还有什么好处吗?请大佬解答一下

发表于 04-08 06:35

Microchip推出容量更大、速度更快的串行 SRAM产品线

该产品线提供了并行SRAM的低成本替代方案,容量高达 4 Mb,具有143 MHz SPI/SQI™ 通信功能 为满足客户对更大更快的 SRAM 的普遍需求,Microchip

发表于 04-03 15:24

•1251次阅读

Microchip Technology扩展了旗下串行SRAM产品线,容量最高可达4Mb

为满足客户对更大更快的 SRAM 的普遍需求,Microchip Technology(微芯科技公司)扩展了旗下串行SRAM产品线,容量最高可达4 Mb,并将串行外设接口/串行四通道输入/输出接口(SPI/SQI™)的速度提高到143 MHz。

STM32G4如何把所有程序都在SRAM中运行?

通过外部引脚可配置BOOT从SRAM中启动,上电过程SRAM没有初始化,BOOT从SRAM启动的作用是什么,这个我不能理解。

我想实现所有程序都在S

发表于 03-12 07:30

sram作用

sram作用

评论