是的。当时钟输入信号穿过输入级的开关区域时,输入级中的随机噪声在信号传递到后续级时增加了信号的时间抖动。更快地穿过该开关区域(具有更高的压摆率)的信号受随机噪声的影响较小,导致较少的附加时间抖动和较低的时钟输出抖动。对于相同幅度的信号,较高频率信号具有较高(较快)的转换速率,因此可以通过时钟分配系统导致较低的时间抖动。

时钟频率的输入中添加的任何抖动都不能通过随后的时钟频率划分来降低(相位噪声会随着分频而降低,但不会降低抖动)。因此,应在输入端尽可能减少抖动。

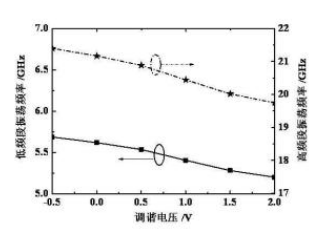

这意味着原则上运行VCO的频率高于时钟输出所需的频率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

频率

+关注

关注

4文章

1588浏览量

62372 -

VCO

+关注

关注

14文章

321浏览量

71450 -

输入信号

+关注

关注

0文章

559浏览量

13219

发布评论请先 登录

相关推荐

热点推荐

多通道频率计模块优势与应用场景

大规模的重新设计。在工业自动化生产线上,随着生产规模的扩大和检测需求的增加,可能需要对更多设备的运行频率进行监测。此时,多通道频率计模块可以方便地进行扩展,适应不断变化的测量需求,为系统的升级和优化提供了

发表于 06-12 16:16

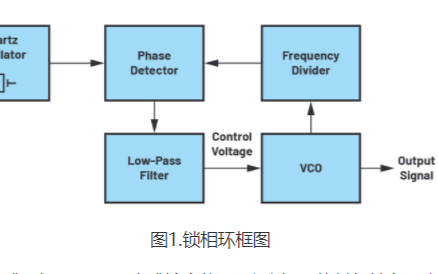

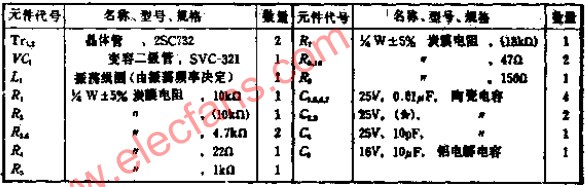

微型高稳定的锁相频率源电路设计

合成一般通过混频、倍频、分频、滤波等方式进行频率变换和组合,从而产生大量离散的稳定频率信号。这不仅使频率合成器具有庞大的体积和重量,其输出信号中的谐波、噪声及寄生

发表于 07-09 08:12

如何用交叉耦合电流饥饿型VCO设计实现降低时钟频率的相位噪声?

本文设计了一个适用于以太网物理层芯片时钟同步PLL的高宽带低噪声VCO,采用了具有良好抗噪能力的交叉耦合电流饥饿型差分环形振荡器。仿真结果表明,在同样输入噪声和环境噪声的情况下,本文的VC

发表于 02-25 07:39

如何锁住相位使VCO的频率等于参考信号的频率呢?

鉴频鉴相器,当两输入信号频率相同但相位不同的时候,有电压差输出,然后去控制VCO,改变反馈信号频率。这不是导致两输入频率不同了,这如何锁住相位啊,使

发表于 04-24 10:23

驱动高压锁相环频率合成器电路中的VCO详细分析

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率

发表于 11-25 09:23

•18次下载

驱动高压锁相环频率合成器电路的VCO

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率

VCO的频率稳定性是什么

VCO(Voltage-Controlled Oscillator,压控振荡器)的频率稳定性是一个关键的性能指标,它描述了VCO输出频率对输入电压变化的敏感程度及在长时间或不同环境条件

变频器运行频率与给定频率不一致的原因及解决方案

变频器作为现代工业控制中不可或缺的核心设备,其运行频率与给定频率的偏差问题直接影响生产效率和设备寿命。在实际应用中,这种不一致现象可能由硬件故障、参数设置、负载特性或外部干扰等多重因素引发,需通过

VCO频率的运行频率高,具有什么优势?

VCO频率的运行频率高,具有什么优势?

评论