在第二部分中,我们将侧重于详细考察与PLL相关的两个关键技术规格:相位噪声和参考杂散。导致相位噪声和参考杂散的原因是什么,如何将其影响降至最低?讨论将涉及测量技术以及这些误差对系统性能的影响。我们还将考虑输出漏电流,举例说明其在开环调制方案中的重要意义。

振荡器系统中的噪声

在任何振荡器设计中,频率稳定性都至关重要。我们需要考虑长期和短期稳定性。长期频率稳定性是关于输出信号在较长时间(几小时、几天或几个月)内的变化情况。其通常以一定时间内的比率f/f来规定,单位为百分比或dB。

信号源中的已知时钟频率、电力线干扰和混频器产品都可能引起离散杂散成分。随机噪声波动引起的扩张是相位噪声造成的。其可能是有源和无源器件中的热噪声、散粒噪声和/或闪烁噪声造成的。

电压控制振荡器中的相位噪声

在考察PLL系统中的相位噪声之前,我们先看看电压控制振荡器(VCO)中的相位噪声。理想的VCO应该没有相位噪声。在频谱分析仪上看到的输出应是一条谱线。当然,事实并非如此。输出上会有抖动,频谱分析仪会显示出相位噪声。为了便于理解相位噪声,请考虑一种相量表示方式,如图2所示。

图中所示信号的角速度为wo,峰值幅度为VSPK。叠加于其上的误差信号的角速度为wm。Δrms表示相位波动的均方根值,单位为rms度数。

在许多无线电系统中,必须符合总积分相位误差规格的要求。该总相位误差由PLL相位误差、调制器相位误差和基带元件导致的相位误差构成。例如,在GSM中,允许的总相位误差为5度rms。

Leeson方程

Leeson(第6项参考文献)提出了一项方程,用以描写VCO中的不同噪声组分。

其中:

LPM为单边带相位噪声密度(dBc/Hz)

F为工作功率水平A(线性)下的器件噪声系数

k为玻尔兹曼常数,1.38 × 10-23 J/K

T为温度(K)

A为振荡器输出功率(W)

QL为加载的Q(无量纲)

fo为振荡器载波频率

fm为载波频率失调

要使Leeson方程有效,以下条件必须成立:

fm,载波频率失调大于1/f闪烁角频;

已知工作功率水平下的噪声系数;

器件运行呈线性特征;

Q包括元件损耗、器件加载和缓冲器加载的影响;

振荡器中只使用了一个谐振器。

从理论上讲,噪声功率密度由调幅(调相)和调相(调相)分量组成。这意味着总噪声功率密度是上述的两倍。然而,在实践中,PM噪声占主导地位的频率接近承运人和AM噪声占主导地位的频率有些远离承运人。

Leeson方程只适用于断点(f1) 与从“1/f” (更普遍的情况是1/fgamma) 闪烁噪声频率到超过后放大白噪声将占据主导的频率点 (f2)。 的跃迁之间的膝部区域。如图3所示[gamma = 3]。 f1 应尽量低;一般地,它小于1 kHz,而f2则在几MHz以内。高性能振荡器要求使用针对低1/f跃迁频率而专门选择的器件。有关如何尽量降低VCO中相位噪声的一些指导方针如下:

使变容二极管的电压足够高(一般在3至3.8 V)

在直流电压电源上用滤波。

使电感Q尽量高。典型的现成线圈的Q在50至60之间。

选择一个噪声系数最小且闪烁频率低的有源器件。闪烁噪 声可借助反馈元件降低。

多数有源器件都展现出较宽的U形噪声系数与偏置电流之 关系曲线。用该信息来为器件选择最佳工作偏置电流。

使振荡电路输出端的平均功率最大化。

在对VCO进行缓冲时,要使用噪声系数最低的器件。

闭环

前面,我们讨论了自由运行VCO中的相位噪声,考虑了降低该噪声的方式,接下来,我们将考虑闭环(见 本系列第一部分) )对相位噪声的影响。

图4所示为PLL中的主要相位噪声贡献因素。系统传递函数可通过以下等式来描述:

在下面的讨论中,我们将把SREF定义为出现于参考输入上且在鉴相器上看到的噪声。该噪声取决于参考分频器电路和主参考信号的频谱纯度。SN为出现在频率输入端且在鉴相器上看到的、由反馈分频器导致的噪声。SCP为因鉴相器导致的噪声(取决于具体的实现方法)。SVCO为VCO的相位噪声,可用前面提出的方程来描述。

输出端的整体相位噪声性能取决于上面描述的各项。以均方根方式对输出端的所有效应加总,得到系统的总噪声。因此:

其中:

STOT2为输出端的总相位噪声功率。

X2为输出端因SN 和 SREF导致的噪声功率。

Y2为输出端因SCP导致的噪声功率。

Z2为输出端因SVCO导致的噪声功率。

对于PD输入端的噪声项SREF 和 SN,其运算方式与 SREF相同,还要乘以系统的闭环增益。

低频下,在环路带宽范围内,

高频下,在环路带宽范围以外,

鉴相器噪声 SCP导致的总输出噪声贡献可通过把SCP引回PFD的输入端来计算。PD输入端的等效噪声为SCP/Kd。然后将其乘以闭环增益:

最后,VCO噪声 SVCO对输出相位噪声的贡献可按类似方式计算得到。这里的正向增益很简单,就是1。因此,其对输出噪声的贡献为:

闭环响应的正向环路增益G通常是一个低通函数;在低频下非常大,在高频下则非常小。H为一常数,1/N。因此,以上表达式的分母为低通,可见SVCO实际上是由闭环滤波的高通。

针对PLL/VCO中噪声贡献因素的类似描述见参考文献1。前面提到,闭环响应是一个低通滤波器,其截止频率为3-dB,其中,BW表示环路带宽。对于输出端小于BW的频率失调,输出相位噪声响应中的主导项为X和Y、参考噪声N(计数器噪声)导致的噪声项和电荷泵噪声。使SN和SREF保持最小,使Kd保持较大值并使N保持较小值,可以使环路带宽BW中的相位噪声最小化。由于N对输出频率编程,因此,在降噪方面一般不予考虑。

对于远远大于BW的频率失调,主导噪声项为VCO导致的噪声项SVCO.。这是由于环路对VCO相位噪声进行高通滤波的关系。较小的BW的值最为理想,因为可以最大限度地降低积分输出噪声(相位误差)。然而,较小的BW会导致缓慢的瞬态响应,并加大环路带宽中VCO相位噪声的影响。因此,环路带宽计算必须权衡瞬态响应以及总输出积分相位噪声。

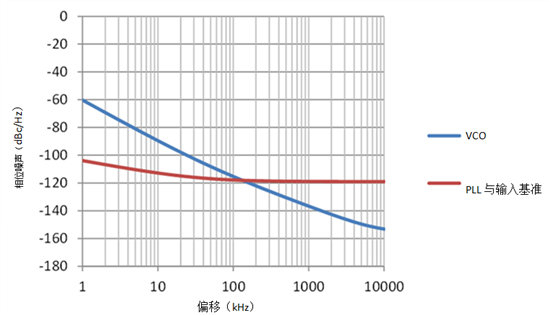

为了展示闭环对PLL的影响,图5展示了一个自由运行的VCO的输出与一个作为PLL一部分的VCO的输出相叠加的情况。请注意,与自由运行VCO相比,PLL的带内噪声已经衰减。

相位噪声测量

测量相位噪声的一种最为常用的方法是使用高频频谱分析仪。图6为一个典型示例,展示了通过分析仪可以看到的情况。

借助频谱分析仪,我们可以测量各单位带宽的相位波动频谱密度。VCO相位噪声最好在频域中描述,其中,频谱密度是通过测量输入信号中心频率任一端的噪声边带获得的。相位噪声功率以分贝为单位,为在偏离载波达给定频率时相对于载波(dBc/Hz)的分贝数。以下等式描述了该SSB相位噪声(dBc/Hz)。

设在频谱分析仪后面板连接器上的10-MHz、0-dBm参考振荡器具有优秀的相位噪声性能。R分频器、N分频器和鉴相器都是ADF4112频率合成器的一部分。这些分频器可通过PC进行控制,从而按顺序编程。频率和相位噪声性能可通过频谱分析仪观察。

图8所示为一款采用ADF4112 PLL和Murata VCO (MQE520-1880)的PLL频率合成器的典型相位噪声图。频率和相位噪声均在5-kHz的范围内测得。所用参考频率为fREF = 200 kHz (R = 50),输出频率为1880 MHz (N = 9400)。如果这是一款理想的PLL频率合成器,则会显示一个离散信号音升至频谱分析仪噪底之上。这里展示的正是该信号音,其中,相位噪声由环路元件所致。选择的环路滤波器值旨在使环路带宽达20 kHz左右。相位噪声中与低于环路带宽的频率失调相对应的平坦部分实际上是“闭环”部分用X2和Y2描述的相位噪声,适用于f处于环路带宽范围内的情况。其额定失调为1-kHz。实测值,即1-Hz带宽范围内的相位噪声功率为–85.86 dBc/Hz。它包括以下组成部分:

1-kHz失调条件下,载波与边带噪声(单位:dBc)之间的相 对功率。

频谱分析仪显示特定分辨率带宽(RBW)的功率。图中使用 的是10-Hz RBW。要在1-Hz带宽范围内表示该功率,必须 从(1)所得结果中减去10log(RBW)。

必须把考虑了RBW实现方法、对数显示模式和检波器特征 的校正系数加到(2)所得结果中。

对于HP 8561E,可使用标记噪声函数MKR NOISE快速测量 相位噪声。该函数考虑了上述三个因素并以dBc/Hz为单位 显示相位噪声。

以上的相位噪声测量值为VCO输出端的总输出相位噪声。如果我们要估算PLL器件的贡献(鉴相器、 R&N 分频器和鉴相器增益常数导致的噪声),则必须将结果除以N2(或者从以上结果中减去20×logN )。结果得到相位噪底[-85.86 - 20×log(9400)] = -165.3 dBc/Hz.

参考杂散

在整数N PLL(其中,输出频率为参考输入的整数倍)中,导致参考杂散的原因是,电荷泵以参考频率速率持续更新。我们再来看看本系列第一部分 中讨论过的基本PLL模型。该模型在这里重复如图9所示。

当PLL锁定时,PFD的相位和频率输出(fREF和fN)实际上是相等的,并且在理论上,PFD无输出。然而,这可能导致一些问题(留待本系列第三部分讨论),因此,PFD在设计上应使得其处于锁定状态时,来自电荷泵的典型电流脉冲如图10所示。

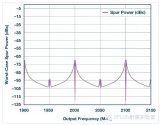

尽管这些脉冲具有极窄的宽度,但它们的存在意味着驱动VCO的直流电压是由频率为fREF的信号进行调制的。这会在RF输出中产生参考杂散,且发生的失调频率为fREF的整数倍数。可以用频谱分析仪来检测参考杂散。只需把范围增至参考频率的两倍以上即可。典型曲线图如图11所示。本例中,参考频率为200 kHz;显然,图中参考杂散发生于RF输出1880 MHz± 200 kHz的范围内。这些杂散的电平为–90 dB。如果把范围增至参考频率的四倍以上,则在(2 × fREF)时也可看到杂散。电

电荷泵漏电流

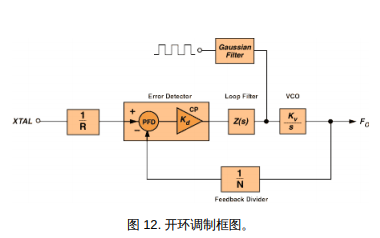

当把频率合成器的CP输出编程为高阻抗状态时,理论上,不会有漏电流流动。实际上,在某些应用中,漏电流的大小会影响到系统的整体性能。例如,考虑这样一种应用,其中,开环模式使用一个PLL来实现频率调制——这是一种简单而经济的高频方法,比闭环模式支持更高的数据速率。对于FM来说,尽管闭环法确实有效,但数据速率却受环路带宽的限制。一种采用开环调制的系统是欧洲无绳电话系统DECT。输出载波频率范围为1.77 GHz至1.90 GHz,数据速率较高,达1.152 Mbps。

开环调制的框图如图12所示。工作原理如下:开始时,环路闭合以锁定RF输出,fOUT = N fREF。调制信号被开启,开始时,调制信号只是调制的直流均值。然后,把频率合成器的CP输出置于高阻抗模式,从而断开环路,同时将调制数据馈入高斯滤波器。然后,调制电压出现在VCO,并乘以KV。当数据突发结束时,环路返回闭环工作模式。

由于VCO通常具有高灵敏度(典型值在20至80 MHz/V之间),因此,在VCO之前的任何小电压漂移都会导致输出载波频率漂移。在高阻抗模式下,该电压漂移以及由此导致的系统频率漂移直接取决于电荷泵CP的漏电流。该漏电流会导致环路电容充电或放电,具体取决于漏电流的极性。例如,1 nA的漏电流会导致环路电容(如1000 pF)上的电压充电或放电dV/dt =I/C(本例中为1 V/s)。这又会导致VCO漂移。因此,如果环路断开1 ms且VCO的KV为50 MHz/V,则1-nA漏电流在1000-pF环路电容中导致的频率漂移为50 kHz。事实上,DECT突发脉冲一般较短(0.5 ms),因此,对于本例中所使用的环路电容和漏电流,漂移实际上会更小。然而,这的确可以证明电荷泵漏电流在这类应用中的重要性。

接收器灵敏度

LO中的宽带噪声会提高IF噪声水平,从而降低总噪声系数。例如,FLO + FIF条件下的宽带相位噪声会在FIF下产生噪声积。这会对接收器灵敏度造成直接影响。该宽带相位噪声主要取决于VCO相位噪声。

LO中的近载波相位噪声也会影响到灵敏度。显然,接近FLO 的任何噪声都会产生接近FIF的噪声积,并直接影响灵敏度。

接收器选择性

结论

在本系列的第二部分中,我们讨论了与PLL频率合成器相关的部分重要技术规格,介绍了相应的测量技术,并展示了一些结果示例。另外,我们还简要讨论了相位噪声、参考杂散和漏电流对系统的影响。

在本系列的最后一部分 中,我们将考察PLL频率合成器的构建模块。此外,还将对PLL的整数N和小数N架构进行比较。

-

振荡器

+关注

关注

28文章

3832浏览量

139035 -

频率合成器

+关注

关注

5文章

219浏览量

32350 -

pll

+关注

关注

6文章

776浏览量

135130

发布评论请先 登录

相关推荐

发现抖动、相位噪声、锁定时间或杂散问题怎么解决

LMX2531 整数杂散优化的案例分析

整数边界杂散的仿真测试与消除方法分析

如何生成和使用杂散进行测试:时钟相位噪声探讨资料下载

如何解决抖动、相位噪声、锁定时间或杂散问题

导致PLL相位噪声和参考杂散的原因及解决方案

导致PLL相位噪声和参考杂散的原因及解决方案

评论