摘要:本论文基于搭建一种具有优秀可移植性的高性能通用软件无线电平台的目的。以亚诺德半导体有限公司的射频捷变收发器AD9364为核心器件代替由分立器件搭建射频收发端,并采用了在Vivado环境用HDL语言对FPGA进行开发的方法,完成了对AD9364的控制和数据收发操作。FPGA与AD9364间的控制通路分别采用了利用UART接口,以及利用ROMIP核的进行AD9364寄存器配置的两种方法,数据接口采用了LVDS兼容模式。利用此平台实现了16APSK调制。平台通过资源占用分析和系统收发试验。得出了通用软件无线电平台的能完成数据收发且具有优秀可移植性的结论。

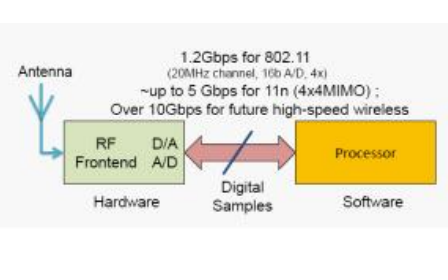

软件无线电的概念最早由美国MITRE公司的Joe.Mitola于1992年5月在美国国家远程会议上提出,其基本思想是以硬件平台作为无线电通信的基础,通过软件编程的方式在此硬件平台上实现可定制的无线电功能。软件无线电系统具有数字化、可编程性、模块化、可扩展性和开放性的特点,使其在包括通信、雷达、导航等无线电应用领域都得到广泛的认可和应用[1-4]。

目前主要有两种软件无线电方案:一种方案是基于分立器件搭建硬件平台,这种方案会导致整个系统结构复杂,功耗大,成本高,另外这种方案的通用性差,针对不同的应用环境需要重新设计硬件平台;另一种方案是采用高集成度器件完成多种功能,能降低成本和功耗,提高开发效率[5-7]。亚诺德半导体有限公司联手赛灵思(Xilinx)公司推出的AD9364便是这样一款高集成度高性能的射频捷变收发器[8-9]。

文中主要设计了一种基于AD9364的通用软件无线电平台方案,完成了该系统的FPGA实现,利用此系统实现了16APSK调制器。且进行了相关的资源消耗评估和性能测试。

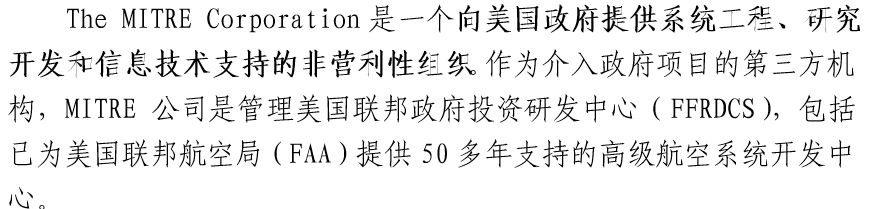

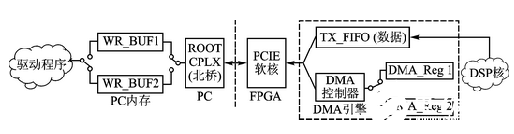

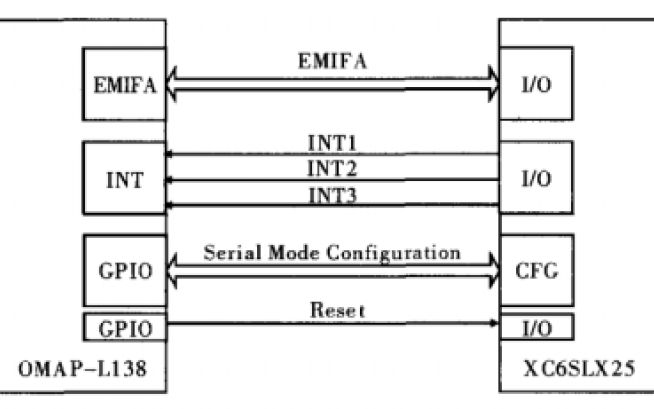

1 总体方案设计此平台以AD9364和FPGA为核心。选用Xilinx公司带有Kintex-7系列XC7K325T芯片的KC705评估板以及AD9364配套的AD-FMCOMMS4-EBZ评估套件,二者通过FMC连接。FPGA外联PC和用户终端机。接收时,无线信号经过天线、双工器、低噪声放大器(LowNoiseAmplifier,LNA)通过AD9364,进入FPGA;发射时,FPGA通过AD9364经过功率放大器(PowerAmplifier,PA)、双工器、天线发射无线信号。双工器隔离发射和接收讯号。PC协助FPGA完成对AD9364的控制;用户终端机产生数据源,并完成后续的信号和数据处理。系统框图如图1所示。

图1 系统框图

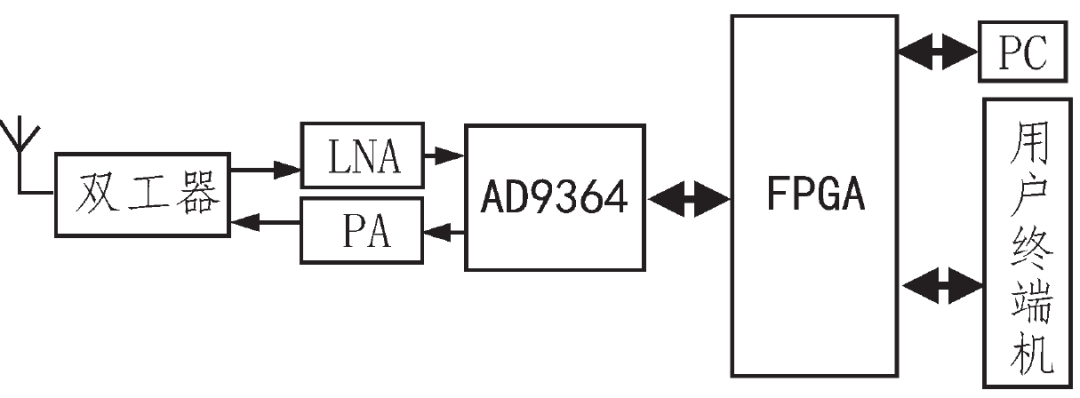

系统包括两个通路:控制通路和数据通路。FPGA功能模块及接口如图2所示。

图2 FPGA功能模块及接口

控制通路完成对AD9364内部寄存器的写入、读取和校验等工作。要求能完成两种配置寄存器配置方式:通过外部接口配置和通过固化在FPGA内部的配置信息配置。为保证在调试阶段AD9364参数实时可调,要求可通过外部接口对AD9364进行控制;为在实际运行中减少对外部依赖,要求系统可独立对AD9364进行控制。

控制通路包括6个模块:通用异步收发传输器(UniversalAsynchronousReceiver/Transmitter,UART)模块、一级指令解析模块、只读存储器(Read-OnlyMemory,ROM)及ROM控制模块、二级指令解析和控制模块以及串行外设接口(SerialPeripheralInterface,SPI)读写模块。AD9364的指令有两种方式获得。第一种方式是携带有寄存器信息的数据由UART口进入FPGA,UART模块完成对数据的接收,送入一级指令解析和编码模块,得到AD9364的指令。第二种方式是由ROM及ROM控制模块读取BlockMemoryGeneratorIP核[10],产生AD9364的指令。二级指令解析和控制模块接收AD9364的指令,控制SPI模块的收发操作,并能完成等待校准等工作。若为读取操作时,此模块能控制读回的数据经过一级指令解析模块,通过UART模块发出。数据通路包括数据发送和数据接收两部分。

AD9364的并行数据接口有两种工作模式可选:标准CMOS兼容模式或低电压差分信号(Low-VoltageDifferentialSignaling,LVDS)兼容模式。由于LVDS兼容模式能提供更高的数据传输速率,因此采用此种模式。发送模块接收来自基带处理器的数据,转换成LVDS形式的信号,发送给AD9364;接收模块接收来自AD9364的LVDS形式的信号,还原为I、Q的形式,送入基带处理器。

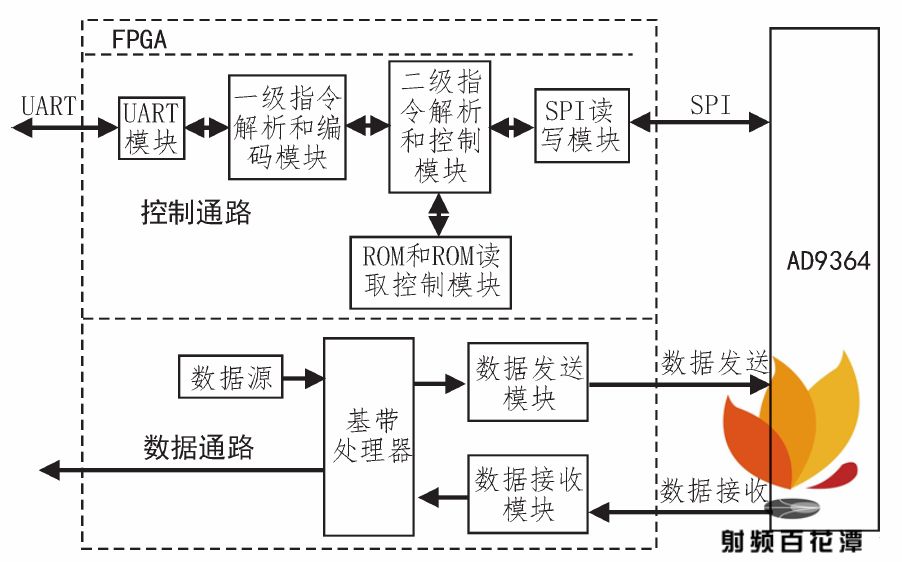

2 AD9364性能及结构AD9364支持时分双工(TimeDivisionDuplexing,TDD)和频分双工(FrequencyDivisionDual,FDD),工作频率范围70MHz到6.0GHz,支持通道带宽范围为200kHz以下至56MHz。集成射频前端和部分信号处理功能,采用零中频架构,内部包括单通道直接变频射频接收器和发射器、模拟滤波器、ADC和DAC以及系统校准功能[11-14]。其内部结构如图3所示[15]。

3 控制通路设计控制通路由UART模块、一级指令解析模块、ROM及ROM控制模块、二级指令解析和控制模块、SPI模块组成。其中系统将指令解析部分分为两级,提升了系统的兼容性。

图3 AD9364功能框图

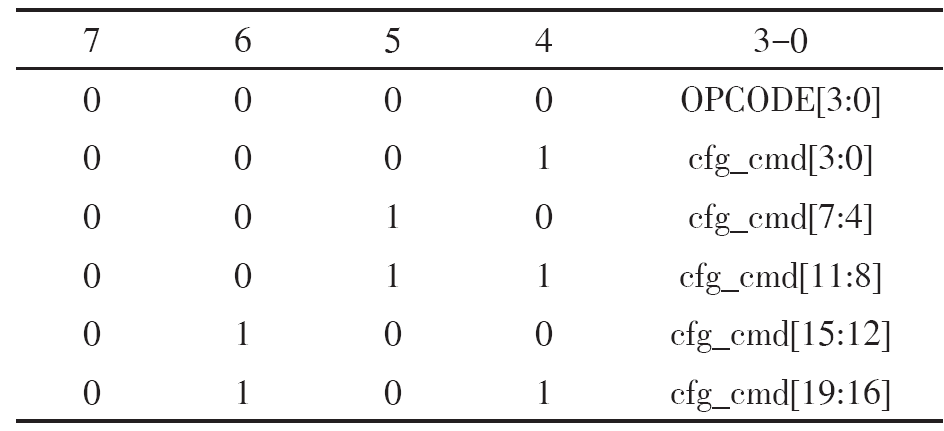

3.1 一级指令解析模块一级指令解析模块在UART配置方式时工作,完成对UART接收数据的初步解析,获取系统级的操作码和操作数,递交给二级指令解析和控制模块,当进行读取操作时可执行其逆过程,生成相应自己送入UART模块。由于UART接口一次只能发送8位信息,而AD9364的寄存器地址为10位,数据为8位,加上操作码,需要UART发送多次信息才能得到一次完成指令。因此,设计采用如表1的格式组合UART字节。

表1 UART 字节格式

将6个UART字节作为一条完整指令,7至4位为字节序号,低四位携带指令。将第一字节的低四位设为系统级操作码OPCODE,0x0代表配置AD9364。后5个字节低四位存储AD9364的指令cfg_cmd。

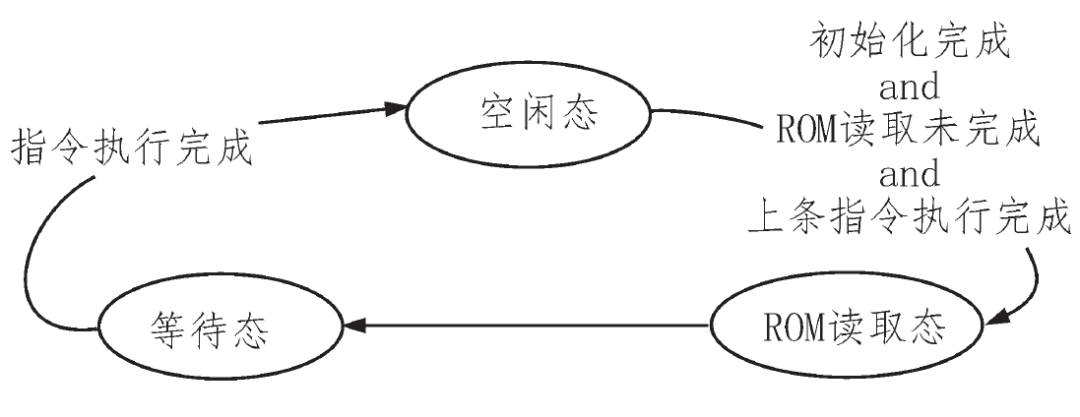

3.2 ROM 及ROM 控制模块ROM及ROM控制模块在通过ROM控制AD9364时工作,通过状态机控制,在ROM中读取一条指令,待执行完成后读取一下条指令,直到最后一条指令执行完成。ROM控制状态机如图4所示。

3.3 二级指令解析和控制模块二级指令解析和控制模块,接收来自一级指令解析模块或ROM 及ROM 控制模块的系统级操作数cfg_cmd,解析得到ad9364的操作码cmd_op,寄存器数据和地址。若为读操作,可执行其逆过程。

图4 ROM配置状态机

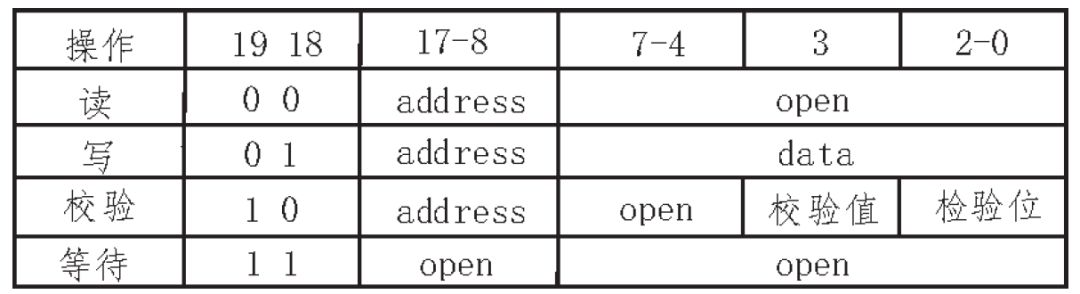

cfg_cmd的格式如图5所示。

图5 cfg_cmd格式

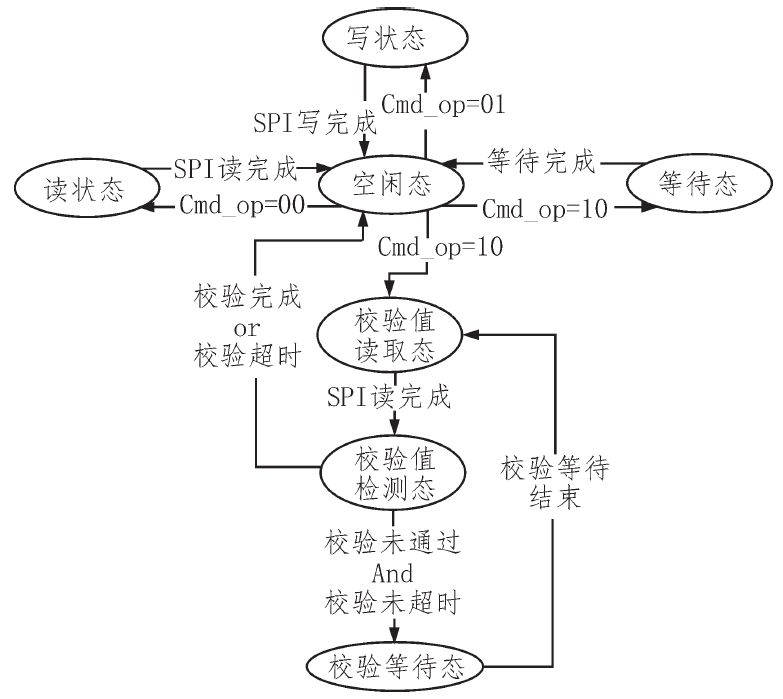

模块根据指令cfg_cmd中的cmd_op获取需要完成的操作,通过限状态机控制SPI模块完成相应操作。状态机如图6所示。此状态机控制整个系统完成寄存器写、寄存器读、等待和寄存器校验操作寄存器写操作将数据写入AD9364相应地址的寄存器中;寄存器读操作读取AD9364相应地址的寄存器的值,并通过UART接口将此寄存器的地址和值发出;等待操作时,系统停止工作一段时间;寄存器校验操作首先读取相应地址的寄存器内的值,检测其中的校验位是否满足校验值,若满足即校验通过,若不满足则等待一段时间后再次读取校验,如此循环,直到校验通过或超时校验失败。

图6 控制状态机

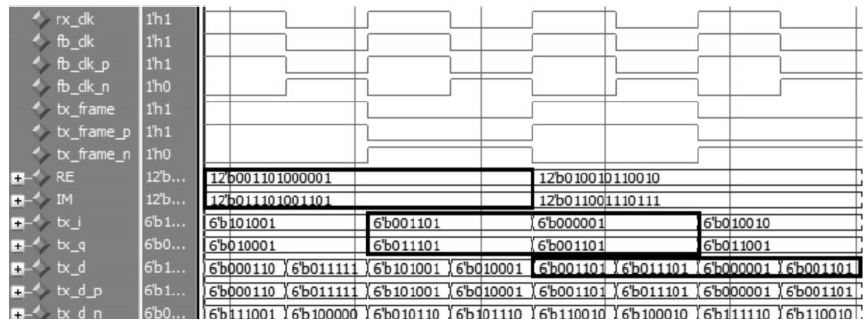

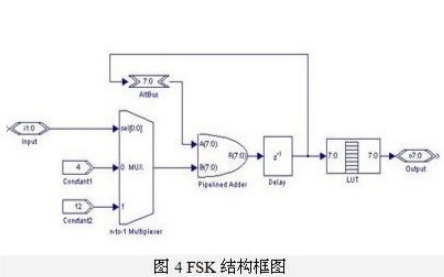

4 数据通路设计数据通路包括数据发送和数据接收两部分。数据源模块产生要传输的数据并完成星座映射。测试中以线性反馈移位寄存器产生的伪随机数作为待传输数据,调制方式采用16APSK。通过星座映射将伪随机数映射为I、Q各12bit的16APSK符号。送入数据发送模块。数据发送模块将每个符号的两个12bit的数据转换为分4次发送的4个6bit数据。在一条6bit宽的总线上发送。发送单音信号时的发送端仿真结果如图7所示。

图7 数据通路发送模块仿真结果

接收模块可将此形式的数据还原为各12bit的I、Q数据。

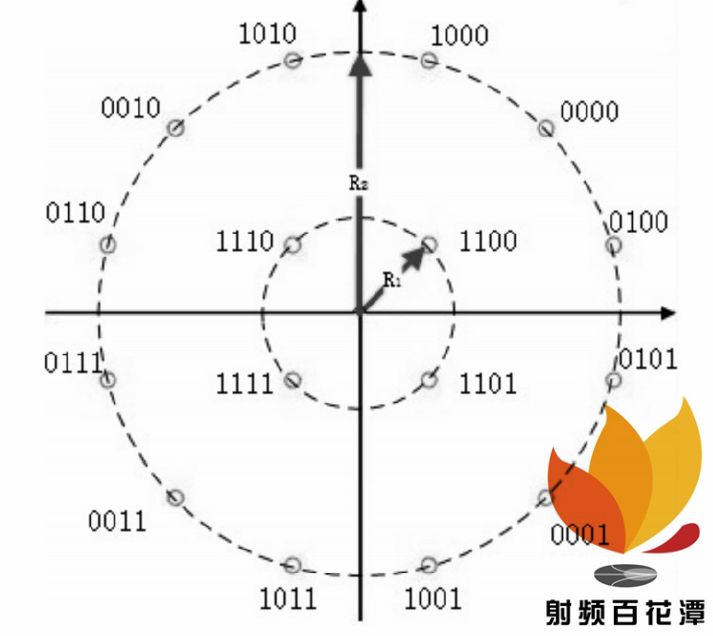

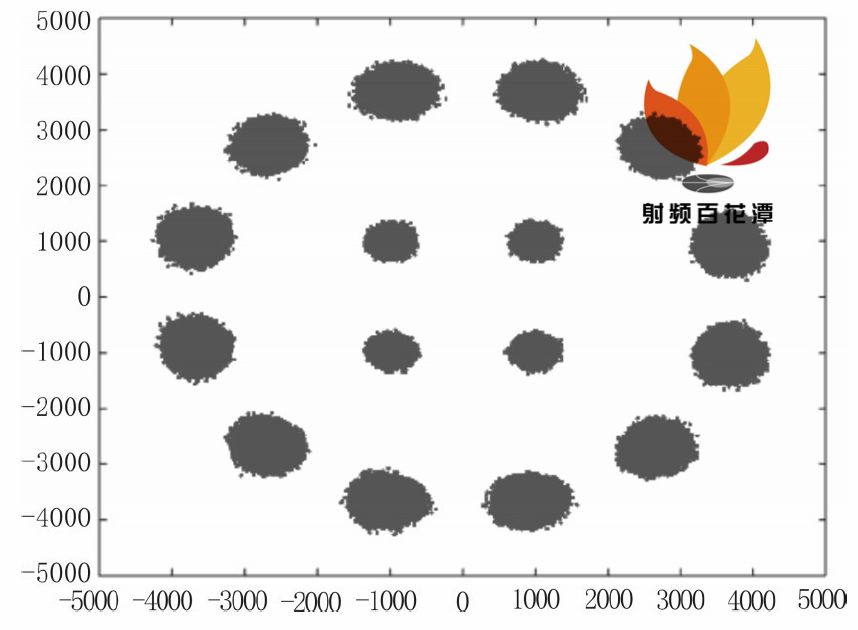

5 16APSK 调制利用此平台实现16APSK调制。为方便测试,将数据源内置于FPGA中,采用线性反馈移位寄存器产生的伪随机数作为数据源。AD9364工作在FDD模式,符号速率30MHz,由SPI控制ENSM状态机,增益控制采用自动模式。首先在数据源模块完成16APSK的星座映射。根据文献[16]设计映射,星座映射图如图8所示。

图8 16APSK星座图

由分别在半径为R1的内圆上均匀分布的4个星座点和半径为R2的外圆上均匀分布的12个星座点组成。每个符号包含4bit信息,采用格雷码形式,最高有效位优先,表示为:b3b2b1b0。保证每两个星座点的欧式距离中的最小值最大化,且内圆功率最小[17],

令γ =R2/R1 =2.73

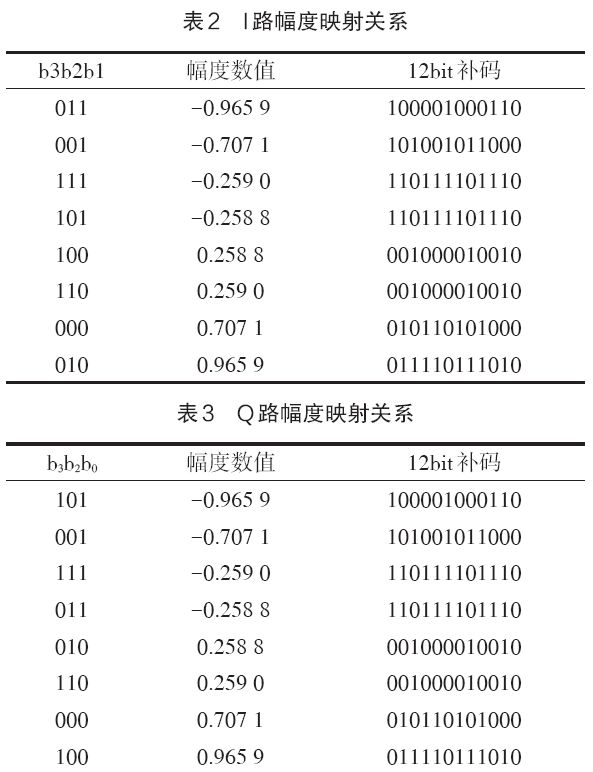

其中γ表示R2和R1的比。观察图8可知,I、Q两路各含8个幅值,可由3bit表示。对于I路,可由b3b2b1表示,对于Q路,可由b3b2b0表示。映射后的幅值采用I、Q各12bit的补码形式表示。I路幅度映射关系如表2所示,Q路幅度映射关系如表3所示。

其中对于幅度0.2588和0.2590映射后的12bit补码形式相同。星座映射后的数据通过6bit宽LVDS形式的数据接口发送到AD9364。

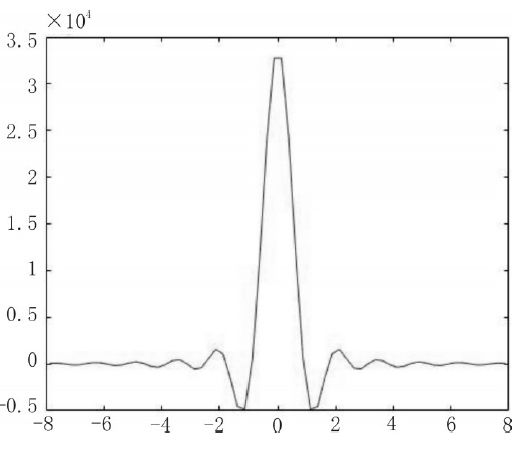

理想脉冲信号的频谱无限宽的,不能在带通信道中传输,因此要通过滤波器对其频谱进行限制,同时要求在信号采样时刻幅度无失真或低失真,这边是基带成型。在此系统中,利用AD9364内部FIR滤波器完成脉冲成形。采用平方根升余弦(SquareRootRaisedCosine,SRRC)形式的滤波器,滚降系数α=0.43,四倍插值。FIR滤波器冲击响应如图9所示。

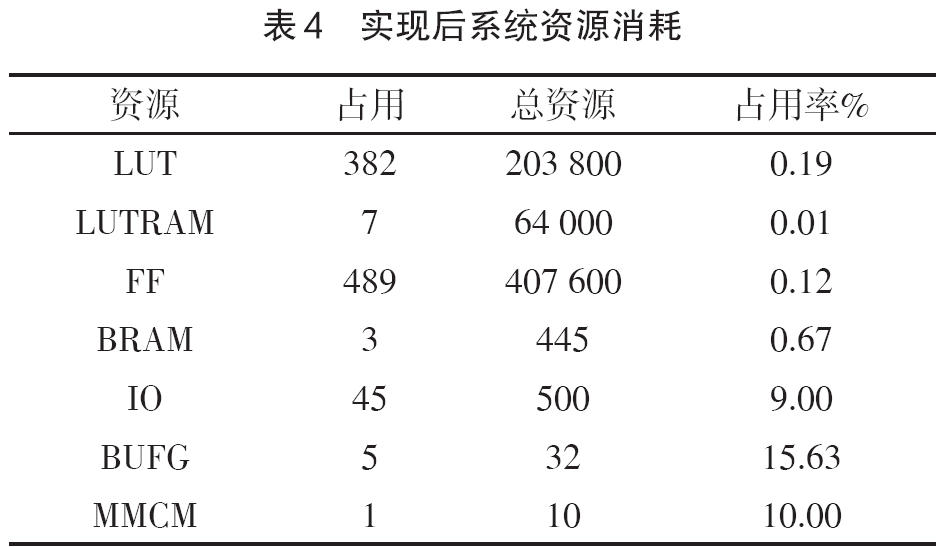

6 FPGA 资源使用情况系统在Vivado环境下完成开发,对系统进行综合、实现。在包括UART模块、一级指令解析模块、ROM及ROM控制模块、二级指令解析和控制模块、SPI读写模块、数据收发模块、16APSK调制模块的情况下。其资源使用情况如表4所示。

图9 FIR滤波器冲击响应

7 测试结果7.1 16APSK 发射测试

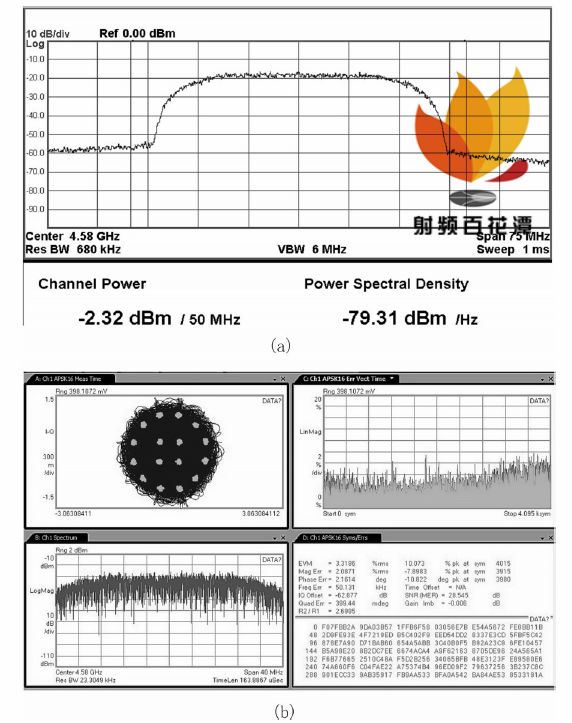

首先测试系统的发射端性能。数据源采用伪随机序列,调制方式采用16APSK,利用频谱仪测试频谱,解调。测试结果如图10所示。可见16APSK信号能正常发送。

7.2 系统接收测试对系统的接收端进行测试。对接收端数据接收模块接收的数据进行解调,利用MATLAB绘制解调后的星座图如图11所示。得出结论16APSK通信成功。

8 结束语文中介绍了一种基于AD9364的通用软件无线电平台的FPGA结构和详细设计。利用此平台实现了16APSK调制器并完成了相应的测试。此设计仅占用较小的FPGA资源,便能实现对软件无线电系统的配置;同时,利用此系统能提高开发效率,降低发开的人力和物理成本。此系统中仅使用了必要的ClockingWizard和BlockMemoryGeneratorIP核,其他部分均采用HDL语言的方式实现,易于移植到其他型号或品牌的FPGA平台上,大大提升了系统的通用性。(参考文献略)

图10 发送端频谱仪测试结果

图11 16APSK解调星座图

-

射频

+关注

关注

105文章

5649浏览量

168599 -

无线电

+关注

关注

60文章

2154浏览量

117073 -

AD9364

+关注

关注

2文章

4浏览量

11342

原文标题:基于AD9364软件无线电平台的FPGA设计与实现

文章出处:【微信号:gh_f97d2589983b,微信公众号:高速射频百花潭】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

USRP系列软件无线电平台

一种软件无线电平台的设计及应用

基于FPGA的通用软件无线电平台设计

基于Xilinx Virtex6 FPGA的通用软件无线电平台设计

SORA软件无线电平台的介绍和使用说明

基于搭建一种具有优秀可移植性的高性能通用软件无线电平台的目的

基于搭建一种具有优秀可移植性的高性能通用软件无线电平台的目的

评论