课程介绍

介绍“详细讲解三态电路”主要涉及的几个问题

第一个问题就是设计电路时需要用运用怎样的思维?

第二个问题就是三态电路有什么特点,什么是上拉电阻、下拉电阻以及高阻态?

第三部分是电路在设计时应该注意两态电路,为什么需要两态?

第四部分是如何增强电路的抗雷击和高压静电能力?

整个系列的课程流程是这样的:

首先,我们会重点讲解电感的四大特性,并利用掌握的知识点来设计电路和分析原理;然后,我们分析电感电流与电容电压的关系。当你已经理解它们的工作原理就可以开始设计电路,并学习运用电阻、电容、稳压管来实现电路信号的延时;整个课程的教学流程是从它的工作原理,设计思维到电路设计,层层渐进的不断的迭代,来完成我们的学习。

我们在整个课程中,重点讲解电感的四大特性和电路设计时的思维方式。我们所有课程都是让每位学习者有更多电子技术研发的实战经验,这个课程不仅是一个项目设计教程,更希望能让大家运用这种思维方式去完成实验。

学习获得:

通过这个课程你可以:

系统掌握电感的特性和相关应用技巧;

快速高效学习如何设计三态电路;

快速成为一名电子研发工程师从事令人羡慕的研发类工作;

提升技术,升职加薪。

适宜学习人群:

1、对硬件设计与开发感兴趣的同学(含电子信息类的大学生,工程研发技术人员,电子爱好者等);

2、只会设计电路但对工作原理却感觉模糊的同学;

3、工作中需要用到电感相关知识的人群;

4、希望提升技术水平,获得更高薪水的工程师;

5、希望提升技术,学习项目设计思考与流程的工程师。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

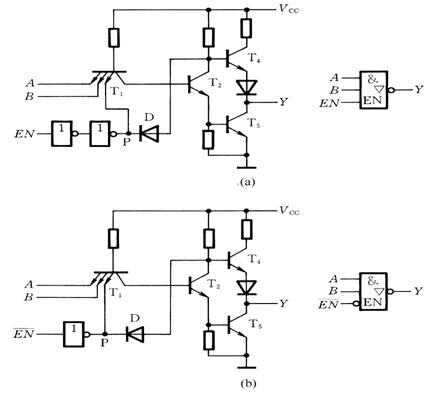

指示灯,继电器等,其驱动指示灯的电路如图所示。什么是三态门?三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门

发表于 05-26 13:01

常用表示方法:高阻态常用字母 Z 表示三态门图1 三态门逻辑符号 三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第

发表于 01-08 11:03

三态输出门的电路图和图形符号

发表于 10-25 07:17

一、三态单片机IO的三态是指:高电平(1)、低电平(0)、高组态(Z)。二、高阻态高阻i是一种电路状态.既不是高电平,也不是低电平,以高阻态

发表于 11-25 06:42

本文就三态电路在FPGA中的应用作了详细的说明。文章首先描述了一个调用lpm中三态电路模块的VHDL程序,这个程序会出现编译不能通过的问题。然后从这个问题出发,通过尝试

发表于 08-06 16:56

•27次下载

什么是三态门?

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻

发表于 05-26 12:48

•4.8w次阅读

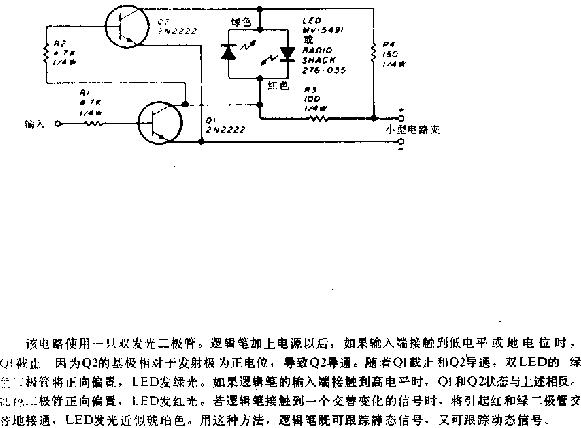

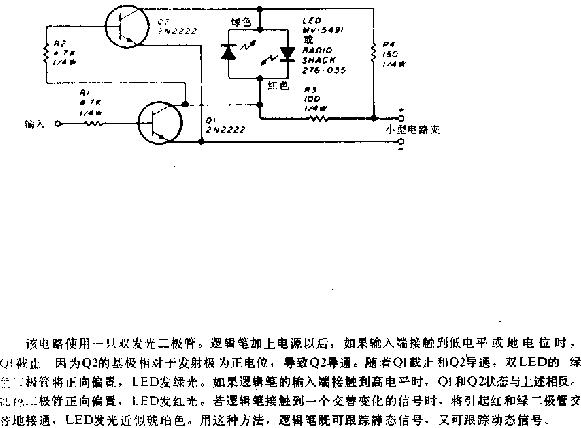

三态逻辑笔电路图

发表于 04-07 09:16

•1808次阅读

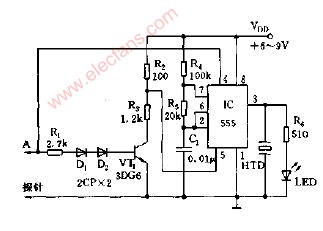

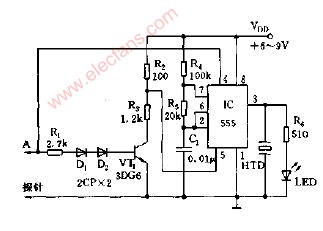

三态声光逻辑笔电路图

发表于 05-19 13:42

•798次阅读

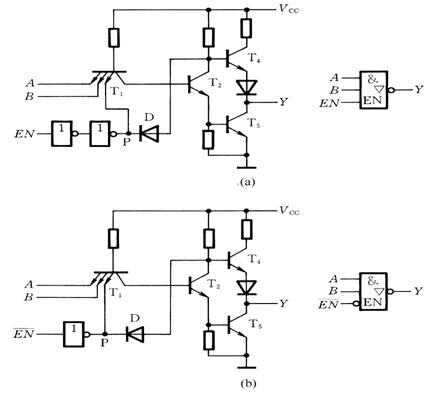

三态输出门的电路图和图形符号

发表于 07-15 19:03

•3320次阅读

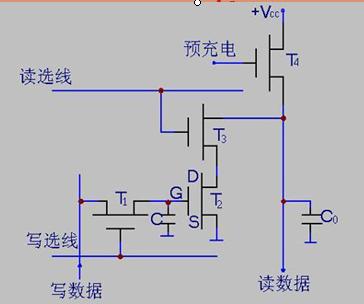

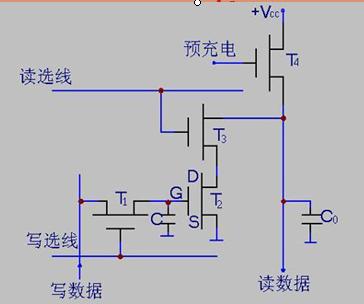

三态MOS动态存储单元电路

发表于 10-10 18:45

•1336次阅读

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态门的逻辑符号,最后介绍了

发表于 03-01 14:03

•8w次阅读

本文开始介绍了三态门的定义与三态门的应用,其次对三态门的三态及特点进行了介绍,最后阐述了三态输出

发表于 03-01 14:47

•13w次阅读

三态门亦称“三态输出门”、“三态门输出电路”。是一种重要的总线接口电路。具有高电平、低电平和高阻抗三

![的头像]() 发表于

发表于 03-10 09:29

•1.8w次阅读

三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O

![的头像]() 发表于

发表于 11-29 07:09

•4646次阅读

三态门电路是一种特殊的数字逻辑电路,其输出可以有三种状态:高电平、低电平和高阻抗状态。这种电路在

![的头像]() 发表于

发表于 07-30 15:17

•6912次阅读

什么是三态电路 三态电路有什么特点

什么是三态电路 三态电路有什么特点

评论