声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pll

+关注

关注

6文章

991浏览量

138459 -

功率

+关注

关注

14文章

2131浏览量

76122 -

RF

+关注

关注

66文章

3204浏览量

172325

发布评论请先 登录

相关推荐

热点推荐

MAX2880:高性能分数/整数-N PLL的全面解析

下工作,为各种应用提供了精确且灵活的频率合成解决方案。本文将对MAX2880进行详细的介绍,包括其特性、应用、工作原理以及寄存器配置等方面。 文件下载: MAX2880.pdf 一、MAX2880概述 MAX2880是一款高性能的PLL

ADF4116/ADF4117/ADF4118:高性能RF PLL频率合成器解析

ADF4116/ADF4117/ADF4118:高性能RF PLL频率合成器解析 一、引言 在无线通信领域,频率合成器是实现精确频率控制的关键组件。ADF4116/ADF4117/ADF4118作为

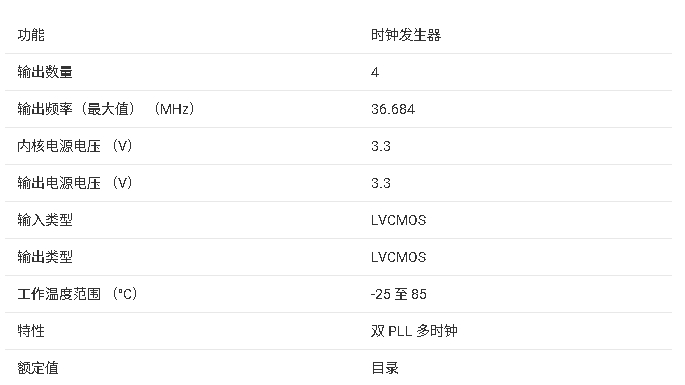

Texas Instruments PLL1705/PLL1706:3.3-V 双 PLL 多时钟发生器的卓越之选

Texas Instruments 推出的两款低功耗、高性能的 3.3-V 双 PLL 多时钟发生器——PLL1705 和 PLL1706。 文件下载:

深入剖析LMX2470:高性能Delta - Sigma分数N PLL的全方位解读

深入剖析LMX2470:高性能Delta - Sigma分数N PLL的全方位解读 在当今的电子设备设计中,频率合成器扮演着至关重要的角色。TI的LMX2470作为一款高性能的Delta

Texas Instruments PLL1707和PLL1708:低抖动多时钟发生器的卓越之选

Texas Instruments的PLL1707和PLL1708,这两款低功耗、高性能的锁相环(PLL)多时钟发生器。 文件下载: pll

探索LMX2491:6.4-GHz低噪声RF PLL的卓越性能与应用

探索LMX2491:6.4-GHz低噪声RF PLL的卓越性能与应用 引言 在当今的电子世界中,高性能的射频锁相环(PLL)是许多先进系统的

探究PLL1705与PLL1706:3.3V双PLL多时钟发生器的卓越性能

一下德州仪器(Texas Instruments)推出的两款低相位噪声、高性能的3.3V双PLL多时钟发生器——PLL1705和PLL1706。 文件下载:

深入解析PLL1707-Q1:高性能多时钟发生器的理想选择

深入解析PLL1707-Q1:高性能多时钟发生器的理想选择 在电子设计领域,时钟发生器是系统稳定运行的关键部件。今天要介绍的是德州仪器(TI)的PLL1707 - Q1,一款专为满足汽

PLL1708双PLL多时钟发生器技术文档总结

引脚和PLL1708的引脚可以通过 串行模式控制引脚。该设备为客户提供 通过消除外部 组件并使客户能够实现非常 高性能音频所需的低抖动性能 DAC 和/或 ADC。PLL1707和

PLL1707/PLL1708 双PLL多时钟发生器技术文档总结

引脚和PLL1708的引脚可以通过 串行模式控制引脚。该设备为客户提供 通过消除外部 组件并使客户能够实现非常 高性能音频所需的低抖动性能 DAC 和/或 ADC。PLL1707和

TLC2933A 高性能锁相环 (PLL) 芯片技术文档摘要

。带有内部电荷泵的高速PFD检测参考频率输入和外部计数器输入的信号频率之间的相位差。VCO和PFD都具有抑制功能,可用作掉电模式。由于TLC2933A高速和稳定的振荡能力,该TLC2933A适合用作高性能PLL。

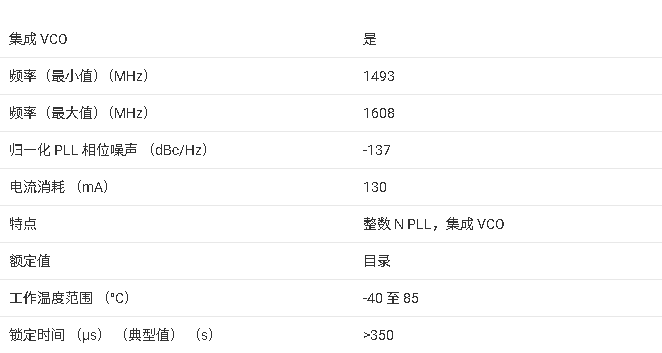

TRF3761系列整数N锁相环(PLL)与集成VCO芯片技术文档总结

TRF3761 是高性能、高度集成的频率合成器系列, 针对高性能应用进行了优化。该TRF3761包括一个低噪声、电压控制的 振荡器 (VCO) 和整数 N PLL。

TRF376

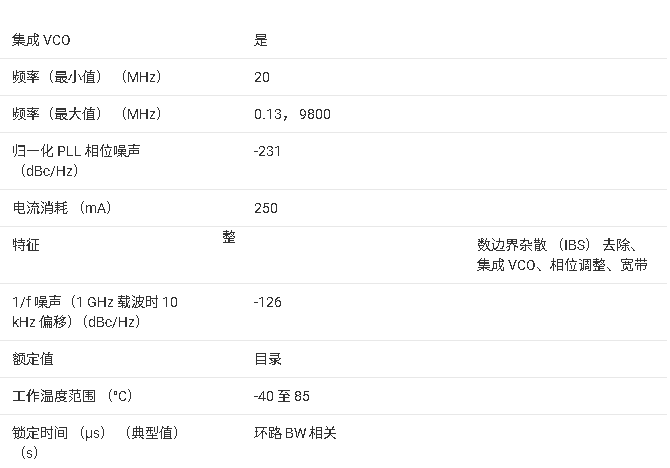

LMX2592 高性能宽带射频合成器技术文档总结

行精细的频率选择。6 GHz 输出的集成噪声为 49 fs,使其成为理想的低噪声源。该器件将一流的 PLL 和集成 VCO 噪声与集成 LDO 相结合,无需在高性能系统中使用多个分立器件。

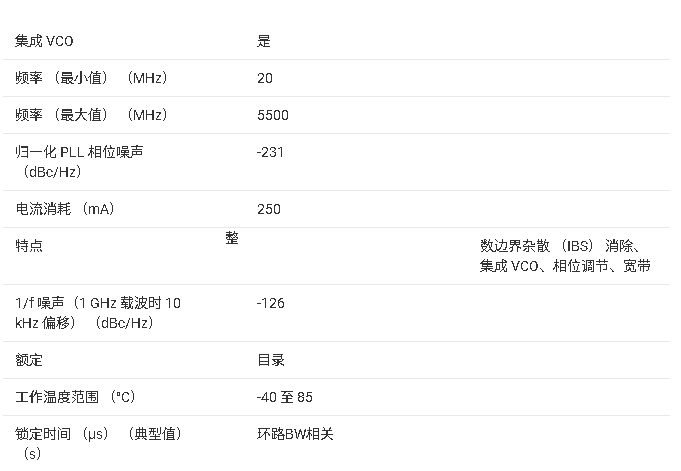

LMX2582高性能宽带RF合成器(集成VCO)技术文档总结

的频率选择。1.8 GHz 输出的集成噪声为 47 fs,使其成为理想的低噪声源。该器件将一流的PLL和集成VCO噪声与集成LDO相结合,无需在高性能系统中使用多个分立器件。

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc

电子发烧友网为你提供()集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器相关产品参数、数据手册,更有集成整数 N 分频 PLL 和 VCO 的 35

发表于 05-22 18:31

高性能RF PLL和PLL VCO技术的介绍

高性能RF PLL和PLL VCO技术的介绍

评论