- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:40fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

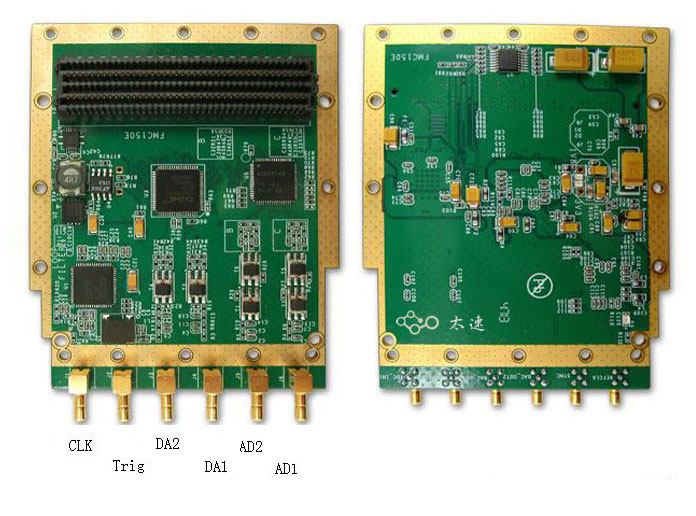

AD9739A FMC板基于14位DAC,能够让有线电视和宽带运营商将高至1 GHz的整个电缆频谱合成于Xilinx Virtex-6 ML605、Kintex-7 KC705和Virtex-7 VC707上的单个RF端口。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电视

+关注

关注

15文章

2502浏览量

76241 -

Xilinx

+关注

关注

71文章

2172浏览量

122461 -

dac

+关注

关注

43文章

2315浏览量

191816

发布评论请先 登录

相关推荐

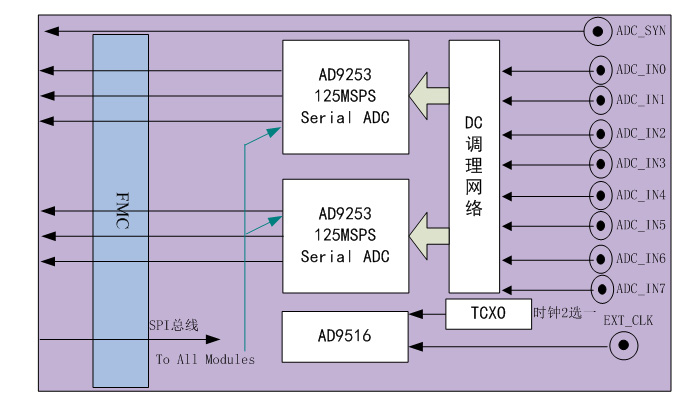

FMC子卡设计原理图:FMC209-基于FMC的4路125MAD输入、2路1GDA输出子卡 中低频信号采集

FMC子卡 , 中低频信号采集 , AD9268板卡 , DA输出子卡 , FMC连接

FMC子卡设计方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速数据处理核心板

AD FMC子卡 , FMC子卡 , FMC子卡模块 , XC7K420T处理板 , 图像FMC子卡

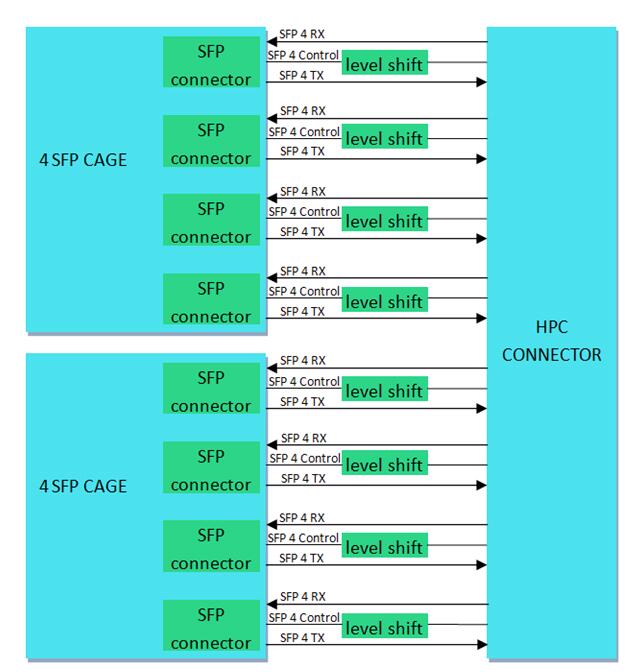

ADC的FMC接口协议支持VITA 57.1 FMC1 HPC CONNECTOR吗?

ADC芯片评估板的FMC接口协议支持VITA 57.1 FMC1 HPC CONNECTOR吗?

发表于 12-13 14:03

ADC12DL3200EVM评估板lvds接口是标准的FMC接口吗?

我查看原理图首页框图标注FMC,但引脚定义似乎与普通fmc不同:

第一图为ADC12DL3200EVM,A1 A2是一对差分对,图2是Xilinx KC705的

发表于 11-22 06:45

NUCLEO-H753ZI stlink串口引脚和定义的fmc引脚有冲突要怎么办?

用的是NUCLEO-H753ZI开发板,但是stlink串口引脚和我需要定义的fmc引脚有冲突(fmc驱动lcd),要怎么办!

发表于 05-31 07:46

调试STM32H750的FMC总线读写PSRAM遇到的问题求解?

_Bank1->BTCR[1] |= 0 << 28;//模式A

FMC_Bank1->BTCR[1] |= 4 << 0;//地址建立

发表于 05-01 19:26

调试STM32H750的FMC总线读写遇到的问题求解

将使用内部的 ADDR[25:1] 地址来作为对外部存储器的寻址地址FMC_A[24:0]。”,所以地址实际是右移一位?

各位大神们,可否帮忙解答?指点一二?

发表于 04-10 08:12

请问STM32F437AIH6 FMC是否能外挂SRAM?

求助如题:芯片是BGA169 pin 封装:

1、该芯片FMC无FMC_A13 引脚; 2、用CubeMX 配置FMC,无SRAM选项; 3、芯片手册上写的FMC是支持SRAM的;

发表于 04-07 07:45

AD9739A FMC板的性能及应用分析

AD9739A FMC板的性能及应用分析

评论