声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

收发器

+关注

关注

10文章

3836浏览量

111442 -

3G

+关注

关注

4文章

853浏览量

184200 -

4G

+关注

关注

15文章

5627浏览量

124517

发布评论请先 登录

相关推荐

热点推荐

高速差分线收发器SN65LVDM176:性能与应用全解析

高速差分线收发器SN65LVDM176:性能与应用全解析 在电子设计领域,高速数据传输一直是一个关键需求,而差分线收发器则是实现这一目标的重要组件。今天,我们就来深入探讨德州仪器(TI

AFE80xx RF采样收发器:高性能、宽带宽的多通道解决方案

AFE80xx RF采样收发器:高性能、宽带宽的多通道解决方案 在电子工程师的设计世界里,一款高性能、宽带宽的多通道收发器往往是实现先进系统

AFE8190:高性能16通道RF收发器的卓越之选

AFE8190:高性能16通道RF收发器的卓越之选 在无线通信技术飞速发展的今天,高性能的RF收发器

探索CC2500:2.4 GHz RF收发器的卓越性能与应用潜力

探索CC2500:2.4 GHz RF收发器的卓越性能与应用潜力 在当今无线通信技术飞速发展的时代,低功耗、低成本的射频(RF)收发器在众多

CC2520 2.4GHz IEEE 802.15.4/ZigBee® RF收发器深度解析

CC2520 2.4GHz IEEE 802.15.4/ZigBee® RF收发器深度解析 在当今的无线通信领域,低功耗、高性能的射频收发器至关重要。TI的CC2520作为一款出色的2

CC1100E:低功耗Sub - GHz RF收发器的卓越之选

CC1100E:低功耗Sub - GHz RF收发器的卓越之选 在当今的无线通信领域,低功耗、高性能的RF收发器需求日益增长。CC1100E

探索DS36277:主导模式多点收发器的卓越性能与应用

探索DS36277:主导模式多点收发器的卓越性能与应用 在电子工程领域,收发器的性能和特性对于数据传输的稳定性和效率起着关键作用。今天,我们将深入探讨德州仪器(TI)的DS36277主

TNETE2201B 1.25 - 千兆以太网收发器:性能与应用解析

TNETE2201B 1.25 - 千兆以太网收发器:性能与应用解析 在高速数据传输的领域中,以太网收发器扮演着至关重要的角色。今天我们要深入探讨的是德州仪器(Texas Instruments

探索TJA1028:集成稳压器的LIN收发器的卓越性能与应用

探索TJA1028:集成稳压器的LIN收发器的卓越性能与应用 在汽车电子和工业控制领域,Local Interconnect Network (LIN) 总线系统以其低成本、简单易用的特点,成为

国内唯一,对标ADI!这家芯片公司发布零中频射频捷变收发器

10月14日晚间,成都华微披露了发布两收两发射频捷变收发芯片的公告。公告称,公司研发的HWD9361型射频收发芯片是一款两收两发、最大带宽5

发表于 10-15 13:49

•1537次阅读

软件无线电-AD9361 璞致 PZSDR 软件无线电系列板卡之PZ-FL9361(FMCOMMS3)使用说明

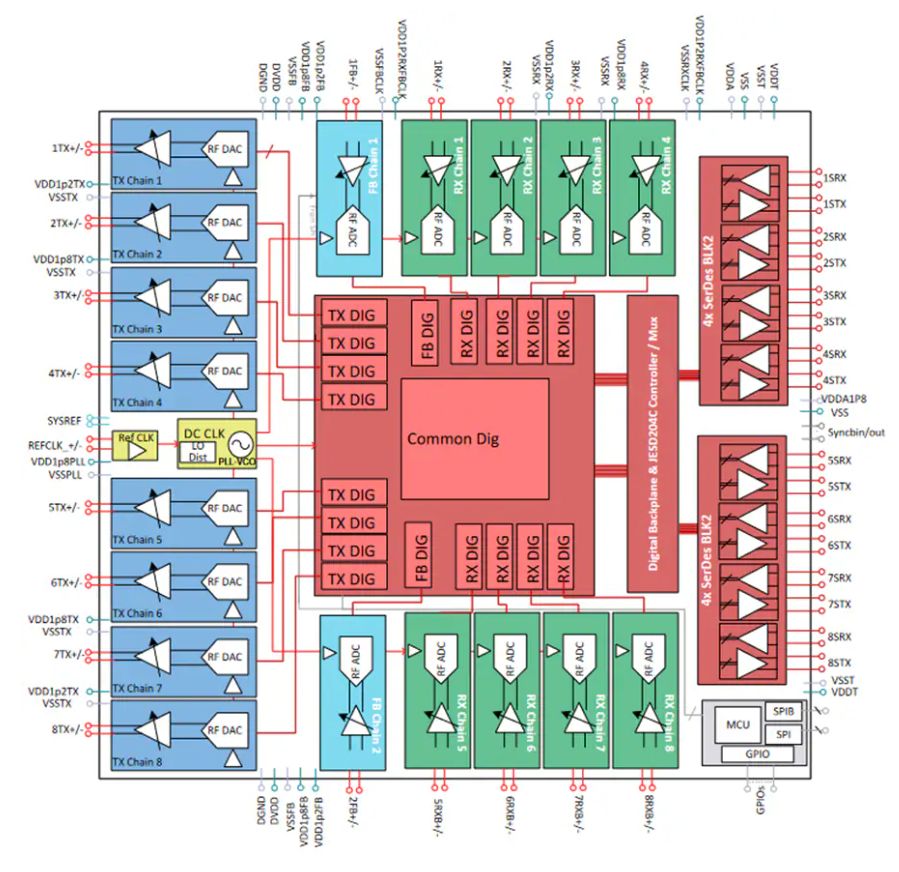

ADI-AD936X系列包含AD9361、AD9364和AD9363三款高性能射频收发器,支持70MHz-6GHz频段和200kHz-56MHz带宽,适用于多种通信标准。FMCOMMS3

AFE8092八通道RF收发器技术解析与应用指南

Texas Instruments AFE8092八通道RF收发器是一款高性能、高带宽、多通道收发器,集成了八个RF采样发送

AD9361

我使用AD9361芯片,参考时钟为10MHz,鉴相频率为20MHz,设置BBPLL频率为800MHz,ADC_CLOCK为BBPLL的2分频,为400MHz,clock_OUT为ADCclock的8

发表于 06-25 15:02

AD9361 RF捷变收发器的性能与应用

AD9361 RF捷变收发器的性能与应用

评论