在刚刚结束的Tesla Autonomy活动中,Tesla非常“大方”的介绍了自己的Full Self-Driving (FSD) Computer从系统到芯片的很多细节。从芯片来看,其“透明度”超过了除Google第一代TPU之外所有的AI相关芯片。实际上,和Goolge TPU的情况类似,在这次发布之前,Tesla也做了一定的专利布局,这正好让我们可以从不同角度更深入的了解Tesla的FSD芯片。

时间线

Tesla自动驾驶芯片负责人Pete Bannon首先介绍了芯片研发的过程:

Feb. 2016:第一个团队成员入职;

Aug. 2017:第一版流片(经过18个月);

Dec. 2017:芯片返回,点亮;

Apr. 2018:BO Release to manufacturing;

Jul. 2018:Production start;

Dec. 2018:Employee retrofits start;

Mar. 2019:Model S & X production start;

Apr. 2019:Model 3 production start

用Pete的话说,从加入Tesla开始到芯片和系统在实际产品中部署,大约用了3年时间,这可能是他做过的项目中用时最短的了。他把这归功于Tesla很强的垂直整合和并行工作的能力,还特别提到了Tesla有很强的Power supply design,Signal integrity design,Package design,System software,Board design,Firmware,System validation团队。这里Tesla给了我们一个参考,即设计,生产和成功部署一颗SoC芯片所需付出的努力和时间。

系统和芯片设计

在具体介绍系统和芯片设计之前,Pete Bannon首先说了项目的前提,“只有一个客户Tesla”,这就很大程度上降低了芯片需求的复杂性。总结起来,FSD芯片的需求就落到了如下几点,依次是功耗,算力,Barch size(latency),安全性。在后面的Q&A中,Pete进一步提到Model 3的功耗的目标是每英里250W(Elon Musk对此作了补充,实际的功耗和道路环境有一定关系)。

前面几个需求主要反映在芯片设计上,而安全性则在系统层面也有很多考虑,比如大量的冗余设计。同一块板卡上的两颗芯片的供电和数据通道都是独立且互为备份的。而一个很有趣的想法是两颗芯片同时都对同样的数据进行分析,然后对比分析结果(或者相互验证),再得出最终结论。

在这个地方Elon Musk还亲自插进来讲了一下这块板卡上的任何部分如果出现故障都不会影响基本的汽车的行驶(他在之后的Q&A环节还补充说明了这一点)。

之后Pete Bannon就开始对芯片进行非常详细的说明。首先是芯片的外观,硅片和一些总体信息。后面的Q&A环节中透露了该芯片使用的是Samsung的14nm工艺。

然后是SoC芯片的基本组成部分,CPU(12核A72),GPU,各种接口,片上网络。这些部分都是采用第三方标准IP。

此外还专门强调了一个SAFETY SYSTEM(如下图所示),是一个独立的CPU,有最终的控制权。

当然,芯片中自研的最重要的部分是Neural Network Processor,也是发布中重点介绍的内容。首先是整体信息,每颗芯片有两个NNP,每个NNP有一个96x96个MAC的矩阵,32MB SRAM,工作在2GHz。所以一个NNP的处理能力是96x96x2(OPs)x2(GHz) = 36.864TOPS,单芯片72TOPS,板卡144TOPS。

这里比较值得注意的片上SRAM的数量。如果我们对比Google的初代TPU(256 x 256MAC,24MiB SRAM),这个片上存储的数量是相当高的。从下图也可以看到NNP中存储器大概占了总面积3/4以上。Pete Bannon的解释是为了降低功耗,他们的设计目标是将所有的模型都能存储在片上。精度的选择是乘法8bit,加法32bit。之后Pete Bannon介绍了芯片工作的方式,没有太多新鲜的东西。

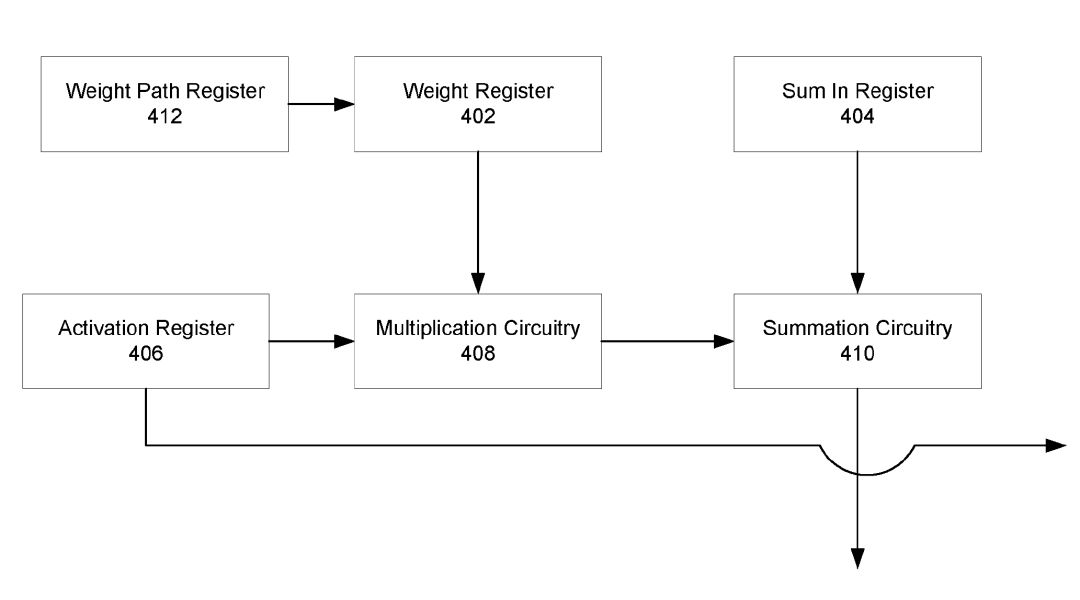

读256B activation和128B weight,经过变形和buffer,组合成96x96的乘加,然后在MAC矩阵中进行运算,最后结果shift out到专门的ReLU和Pool的硬件模块,然后再以每周期128B的带宽存回memory。由于MAC矩阵是96 x 96,所以在把数据输入给MAC矩阵之前,需要做数据格式的变换。完成这一系列动作,总带宽需求是1TB/Sec。考虑到所有数据都在片上SRAM中,这个带宽比较容易满足。

Pete Bannon还提了一下控制逻辑功耗的问题,认为ICache,Register File和Control逻辑消耗的能量要远比运算消耗的能量大,所以NNP的设计就尽量简化了控制逻辑,只做运算。相应的,指令集比较简单,只有8条指令:DMA Read,DMA Write,Convolution,Deconvolution,Inner-product,Scale,Eltwidth,Stop。编程模型(控制流)也非常简单,完成一次运算只需配置4个信息。另外也介绍了编译工具,这个基本也是常见的功能。

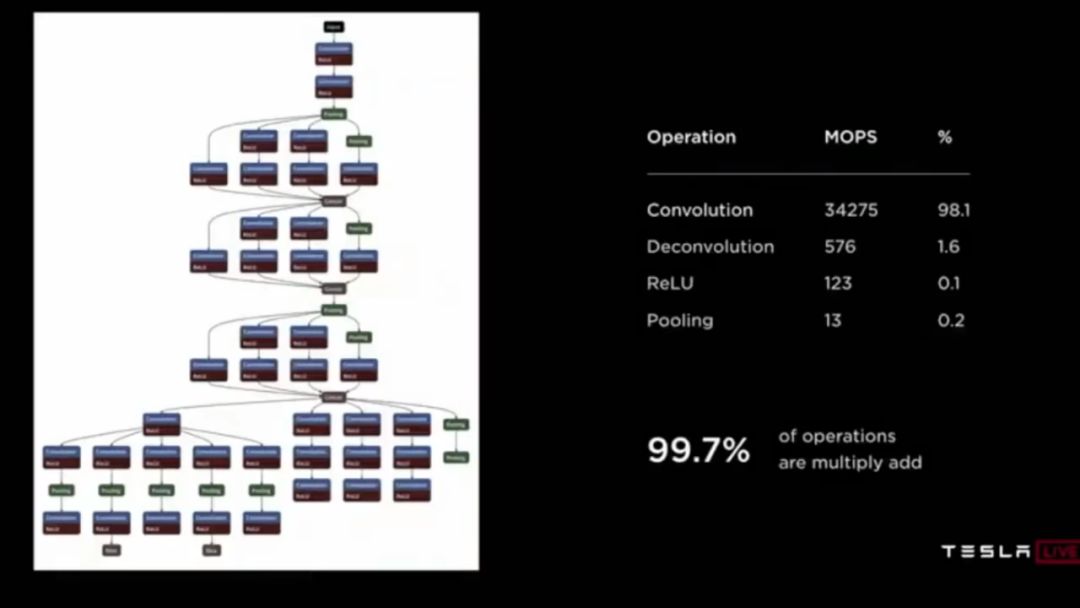

最后,Pete Bannon给出了芯片的实际性能指标,2300 帧/秒,72W。当然我们并不知道这是运行什么网络的结果。如果是讲演中给出的如下示例网络,每帧需要35GOPS,每秒是35x2300=80TOPS,即能达到55%左右的利用率。

到此我们看到了FSD芯片的一些细节,但还不足以充分了解它的架构设计。实际上,在这次公开之前,Tesla是给NNP申请了一系列专利的[2],我们可以从中看到一些更详细的东西。

专利布局

Tesla目前公开的专利,大体的思路和Google之前给TPU申请专利也是差不多的(Google的神经网络处理器专利),先申请整体框架和方法的专利,然后是具体运算,数据格式准备,Vector处理,包括下面几个。

Accelerated Mathematical Engine(Sep. 2017)

Computational Array Microprocessor system with variable latency memory access(Mar. 2018)

Computational array microprocessor system using non-consecutive data formating(Mar. 2018)

Vertor Computational Unit(Mar. 2018)

这里先要说明一下,专利和实际实现可能是有很大差别的。我们对专利的阅读主要是作为对比和参考。下面我们主要看一下第一个专利,即整体架构和方法的专利。虽然这里的名字叫“ACCELERATED MATHEMATICAL ENGINE”,但权力要求里的说法是,“A matrix processor for accelerating convolutions in a neural network”,基本就是一个CNN加速器。

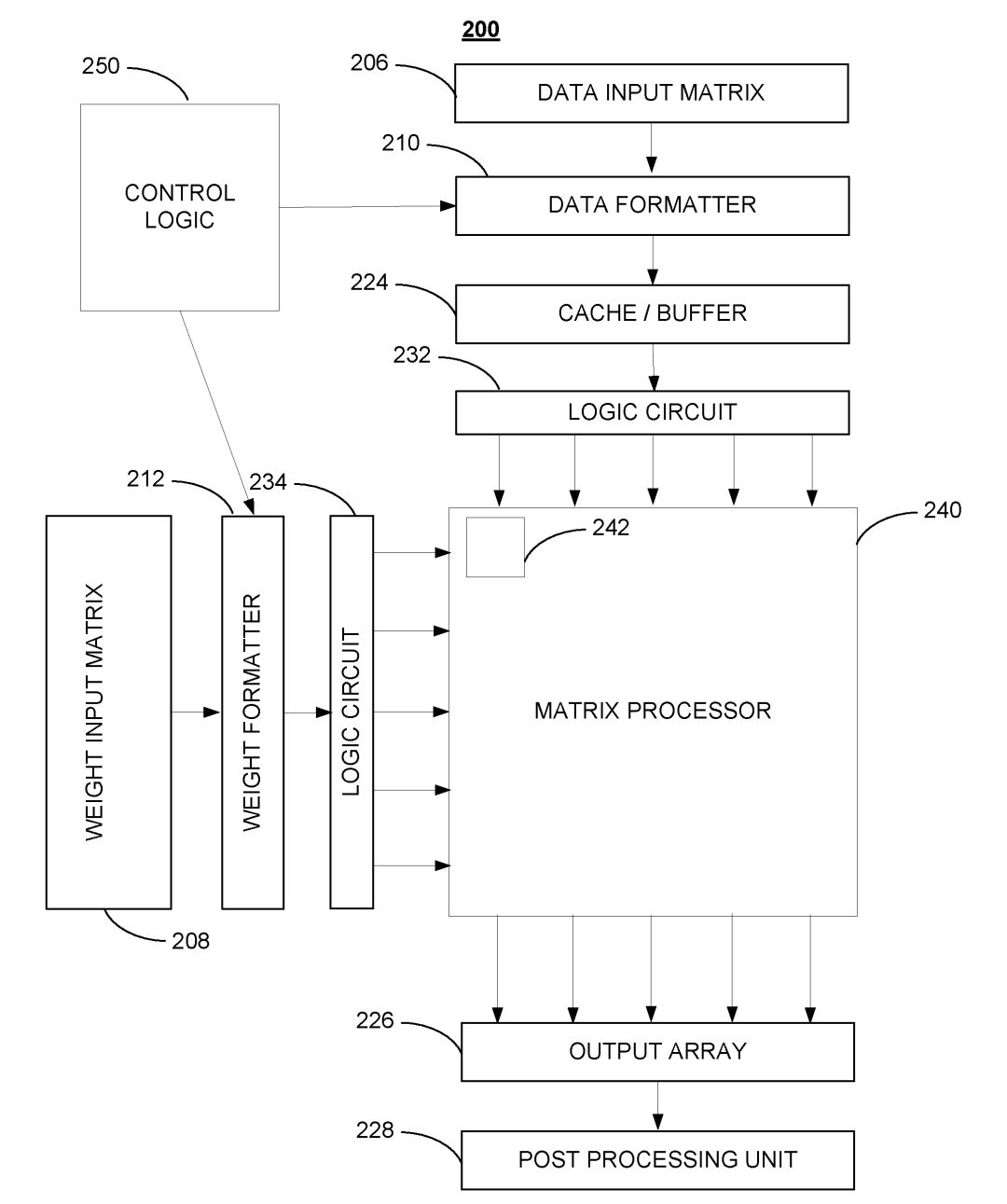

它的基本硬件架构主要是围绕一个大的矩阵处理器(MATRIX PROCESSOR)做文章(如下图)。

Data和Weight分别经过一个FORMATTER进行格式的转换,存入BUFFER,之后有一个硬件电路读出提供给矩阵处理器。专利中提到FORMATTER可以用软件或者硬件实现,它们实际芯片中应该是硬件实现的。由于要有效利用这种规模(96x96)的MAC矩阵,必须把输入数据排好,这个FORMATTER起到了很大作用。因此他们也专门对它申请了专利(Google也是类似情况),有兴趣的同学也可以看看。

在完成了矩阵乘加运算后,结果会移出(shift)矩阵处理器(根据专利里的描述,应该是从上向下逐级移动)进行后续处理,包括累加,ReLU,和Pooling。由Vector Engine和Post-Processing Unit完成。这部分也有专门的专利(申请时间要晚一些),表述上和主架构专利似乎有点不一致。此外就是控制逻辑部分,这部分是一个尽量简单的设计。

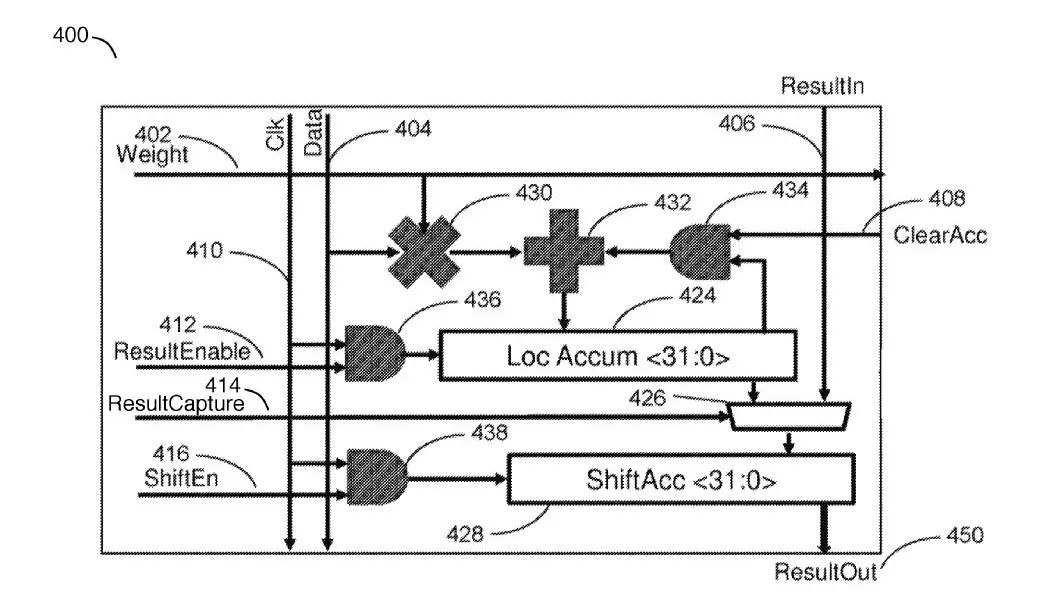

下面我们进入矩阵处理器(MAC Array)内部看看运算单元的设计。

source:Tesla patent “ACCELERATED MATHEMATICAL ENGINE”

对比一下Google的专利中的计算单元,

可以看出主要的区别在于Tesla多了一级累加器ShiftAcc,支持的数据流也能更灵活一些。总得来说,Tesla描述的架构和Google TPU专利描述的NNP("Neural network processor")是类似的,不过看起来在设计和表述上更为完整。在具体实现上,一个主要区别在于,FSD芯片主要使用片上SRAM工作,而不像是Google TPU还需要使用片外的DRAM。当然,还是那句话,专利不代表具体实现,而且Google的专利要早很多。这里只是单纯参考一下。

这几个专利中还有一些有意思的细节,时间关系我每来及细读。大家感兴趣可以自己阅读一下,有趣的信息也欢迎留言分享。我把这四个专利整理了一下,大家可以在后台回复“teslapat”获得下载的链接。回复“googlepat”可以获得Google专利的链接。

Q&A环节的花絮

回到Tesla的活动,在芯片发布之后还进行了Q&A环节,这部分其实也很有意思。首先,Elon Musk说了如下一段话(大意),“我们今天之所以要提供如此详细的信息,就是因为,在一开始,对于Tesla这样从没做过芯片的公司来说,要研发一颗世界最先进的芯片看起来是不可能的。我们的目标就是这样,而且我们的目标不仅仅是领先一点,而是大幅度的领先。”从这段话可以看出,Tesla自研芯片应该是有必要性和能力上的质疑的。对于系统和应用厂商来说,这种质疑也是很正常的。必要性比较容易讲,如问答环节所说,Telsa如果每年卖上百万辆车,而自研芯片能让整车成本降低,当然就值得去做。而针对芯片研发的能力的质疑,这次发布算是一个回答。所以,虽然这颗芯片目前还谈不上世界领先(指标上和Nvidia的对比是不太科学的,这个Nvidia已有回应),Musk也要硬着头皮去说。从另一个角度,这颗芯片至少可以证明自研的可行性。而且Musk也很认真强调了这套系统的优势在于它的软硬件都是专门为Tesla的自动驾驶定制的。对比Nvidia,他是这么说的,“Nvidia is great company, but they have many customers, as they apply their resources, they need to do a generalized solution. We care about one thing so private. It was designed to do that increadibly well and the software was also designed runing on that hardware increadibly well. The combination of hardware and software I think is unbeatable.” 看起来Tesla会在这条路上继续走下去。在被问道工艺问题的时候,Elon Musk专门提到下一代芯片正在研发当中(已经halfway done)。

在被问道是否使用Lidar,Elon Musk说“lidar is fool's errand, anyone luck reliant on lidar is doomed.”在后面关于神经网络和软件的talk里,AI网红Andrej Karpathy也解释了这个观点,"Lidar只是回避了关键的图像识别问题,只是给我们一个技术进步的假想,虽然可以做一些快速DEMO,最终肯定失败"。

还有一个关于实际路测和仿真的问题,Elon Musk说,“Tesla也做很好的仿真,不过还是很难模拟真实环境发生的各种情况,如果仿真环境能够模拟真实情况(这里他顿了一下)我们也不知道自己是不是生活在仿真环境中。”好像他确实认真的感知了一下。

总结

Tesla的自动驾驶芯片是FSD系统的最重要部分,其对标的产品应该是Nvidia的Nvidia Xavier SoC芯片(参考Hot Chips 30 - 巨头们亮“肌肉”中相关部分)。客观来看,Tesla的芯片和NvidiaXavier SoC芯片在各方面还是有差距的。Tesla的SoC设计中,除了自研的Neural Network Processor部分之外,其它都是用业界标准IP,并没做太多定制工作,只能说中规中矩。而NNP也是一个比较简单的架构,也很难说做了很多架构和技术上的创新。从另一个角度来看,这款芯片如果真的大量使用了,那它至少也是合格的。可以看到,Tesla的目标和执行策略是清晰和实际的,这是系统厂商自研芯片的最大优势。

-

自动驾驶

+关注

关注

784文章

13877浏览量

166618

原文标题:多角度解析Tesla FSD自动驾驶芯片

文章出处:【微信号:IV_Technology,微信公众号:智车科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

现代汽车与三星电子洽谈自动驾驶芯片制造合作

三星芯片部门任命新负责人

Rapidus与电装携手共享芯片设计,加速AI及自动驾驶汽车芯片研发

FPGA在自动驾驶领域有哪些优势?

FPGA在自动驾驶领域有哪些应用?

自动驾驶的传感器技术介绍

三星电子任命半导体业务新负责人,加码AI芯片市场

三星电子更换设备解决方案部门负责人

荣耀研发负责人被除名 因违反商业行为准则

黑芝麻智能与腾讯云签署战略合作,共同推动自动驾驶芯片生态合作

未来已来,多传感器融合感知是自动驾驶破局的关键

小鹏汽车迎来新AI负责人,研发XNGP技术

高通自动驾驶靠软件开发革新力压英伟达自动驾驶芯片

Tesla自动驾驶芯片负责人Pete Bannon介绍芯片研发的过程

Tesla自动驾驶芯片负责人Pete Bannon介绍芯片研发的过程

评论